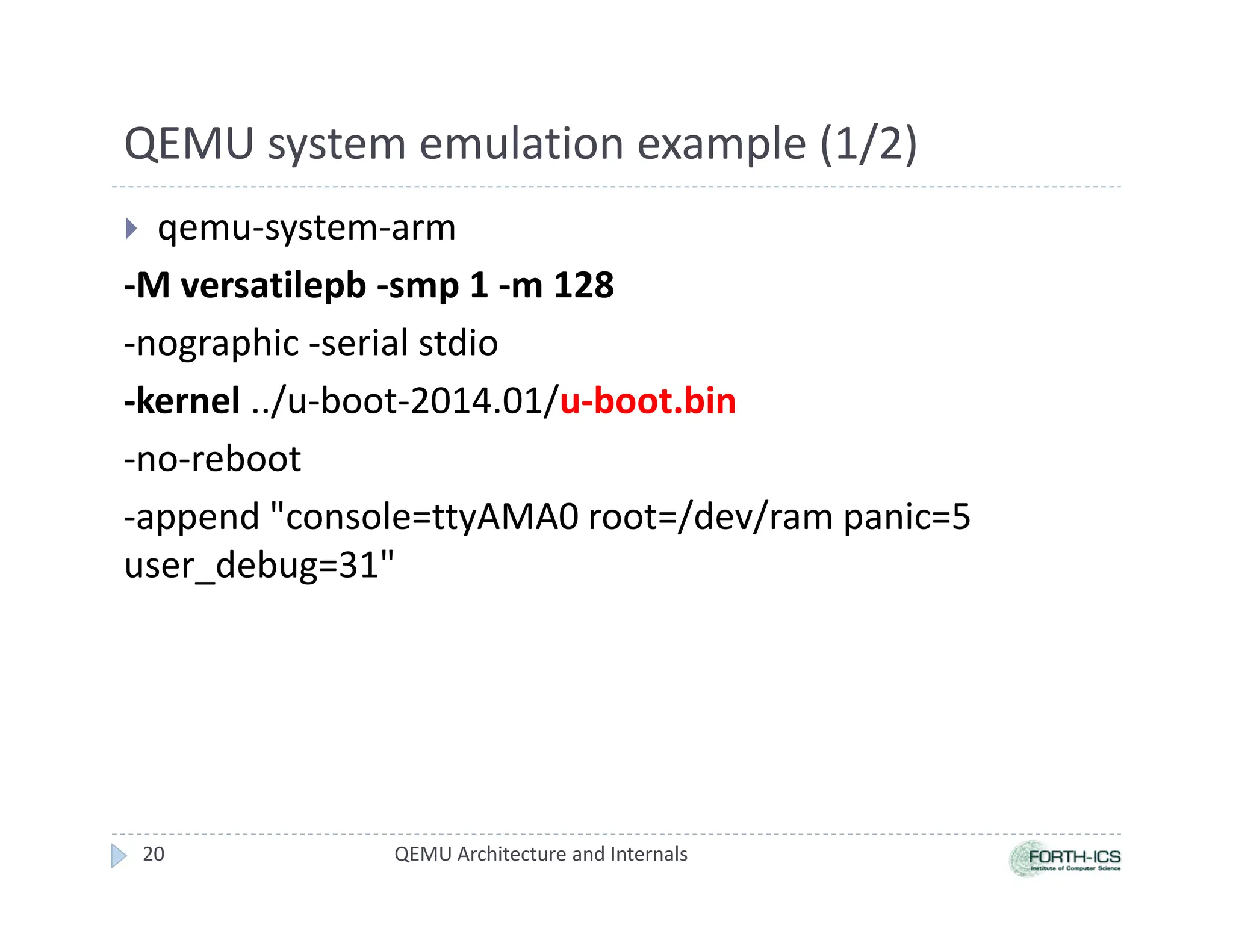

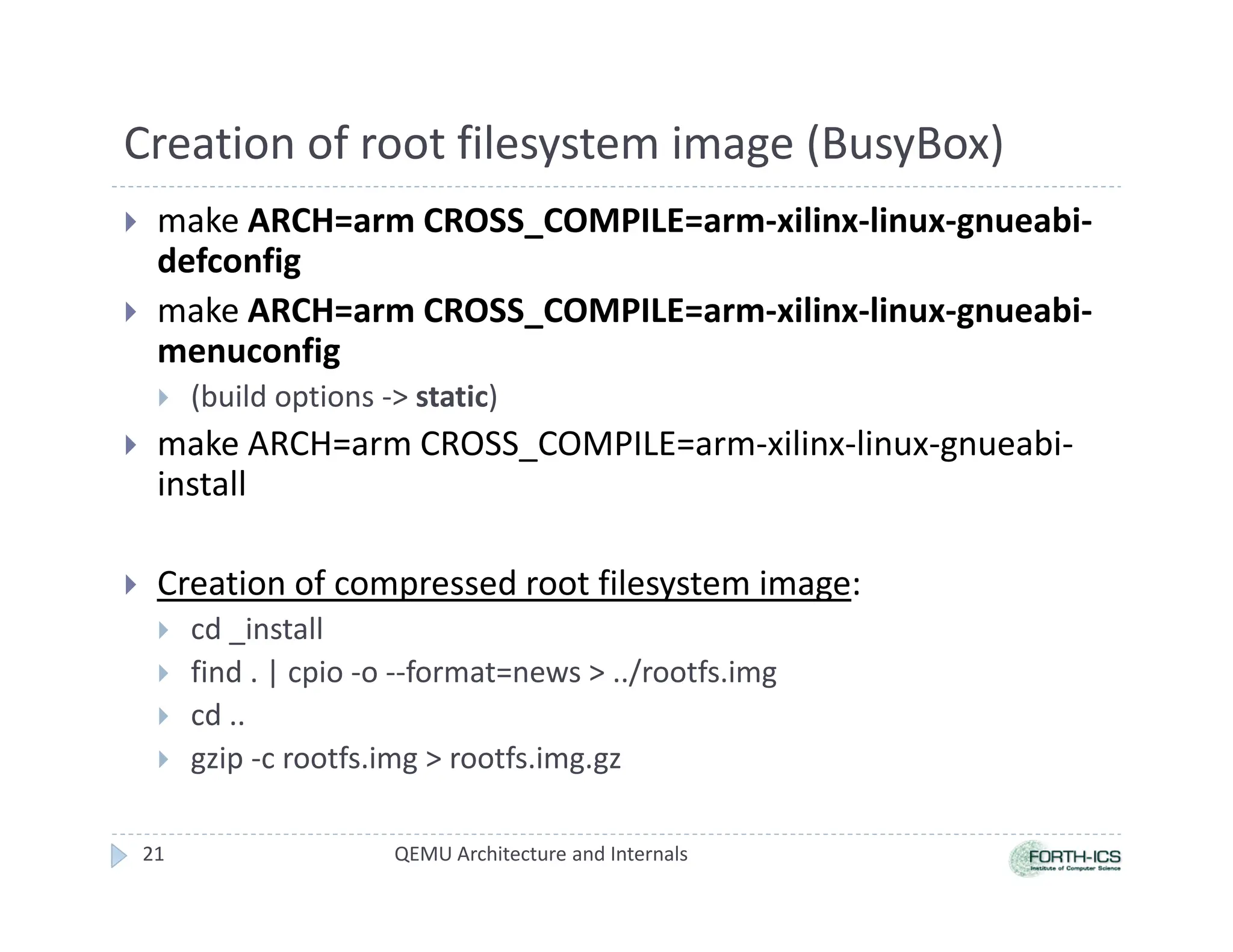

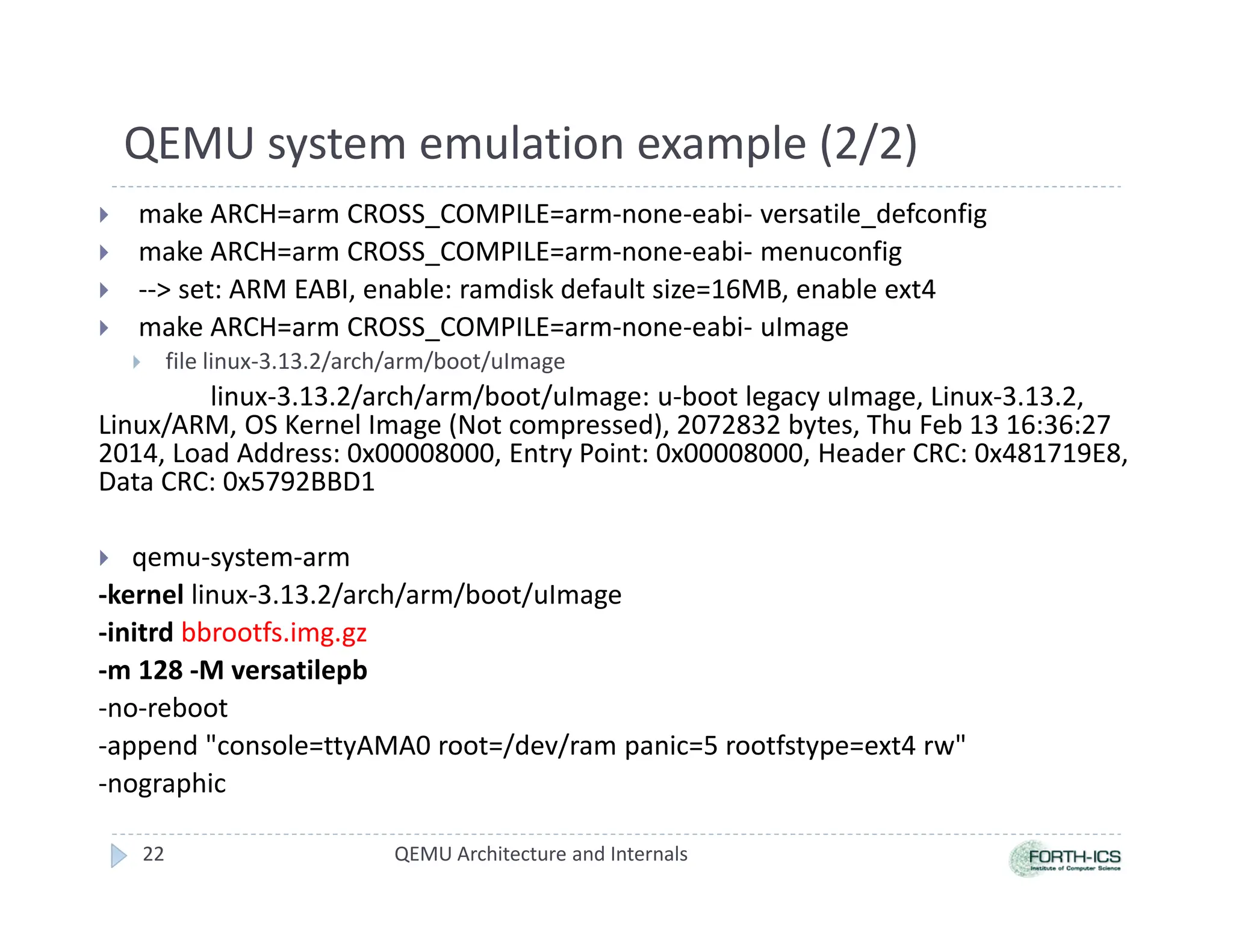

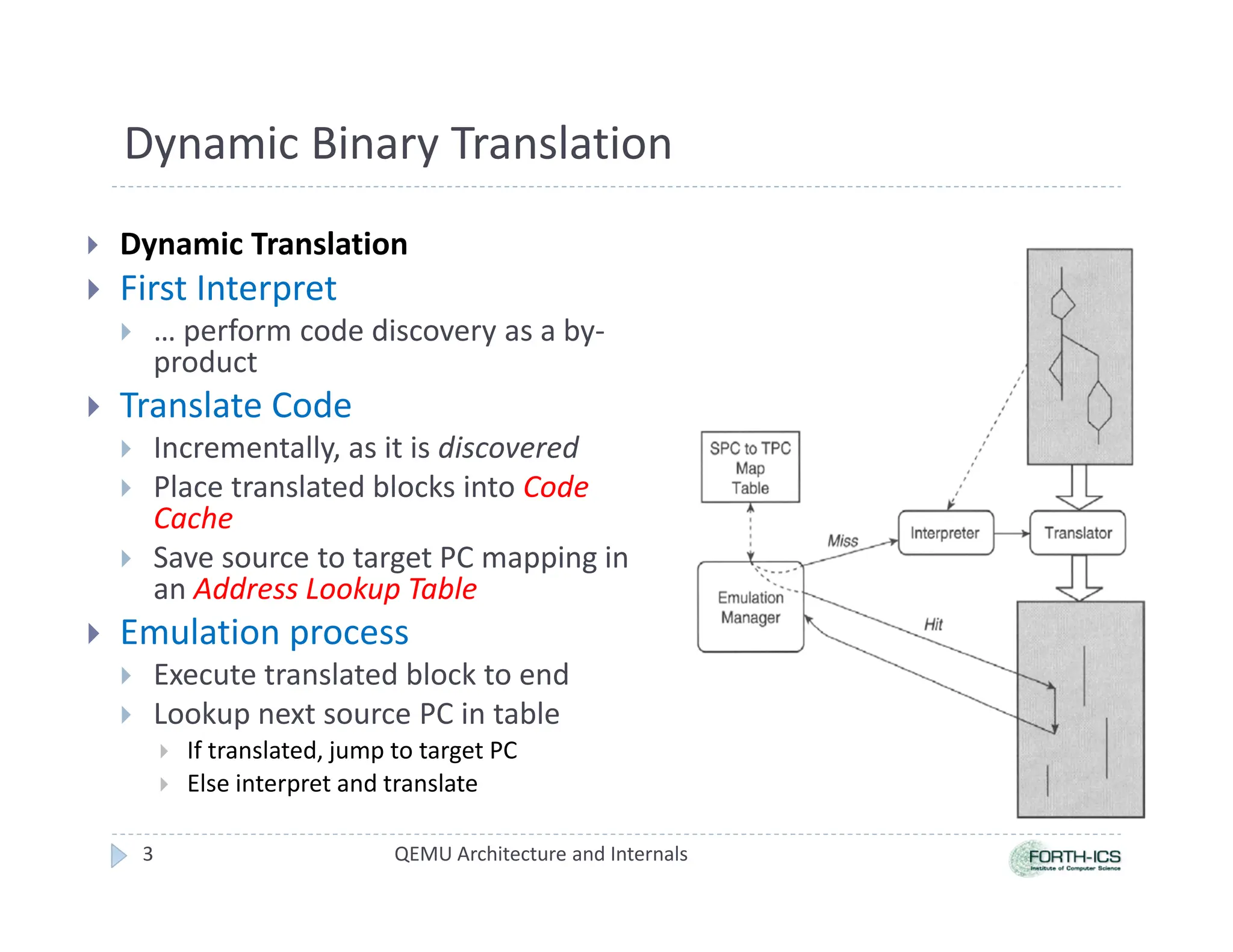

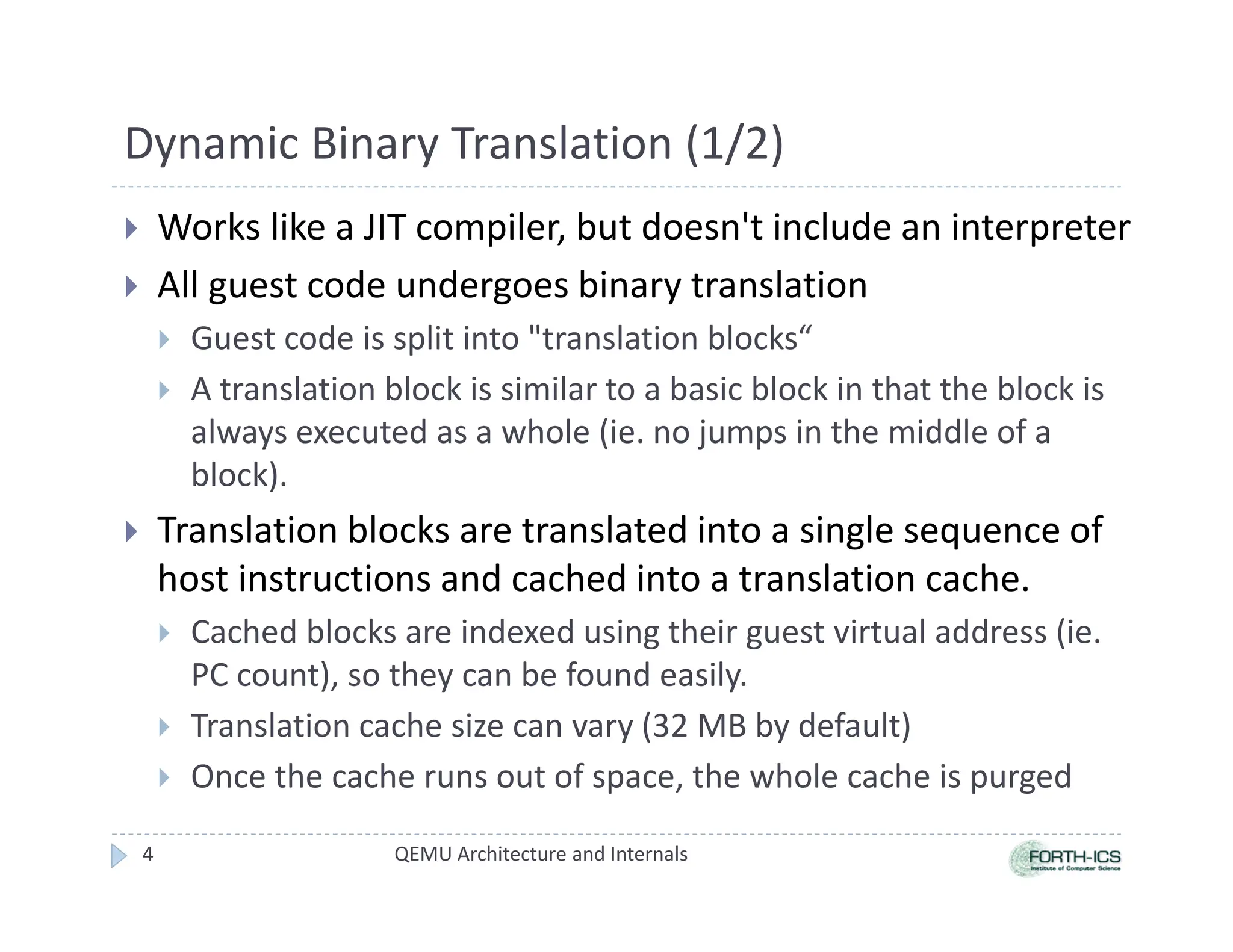

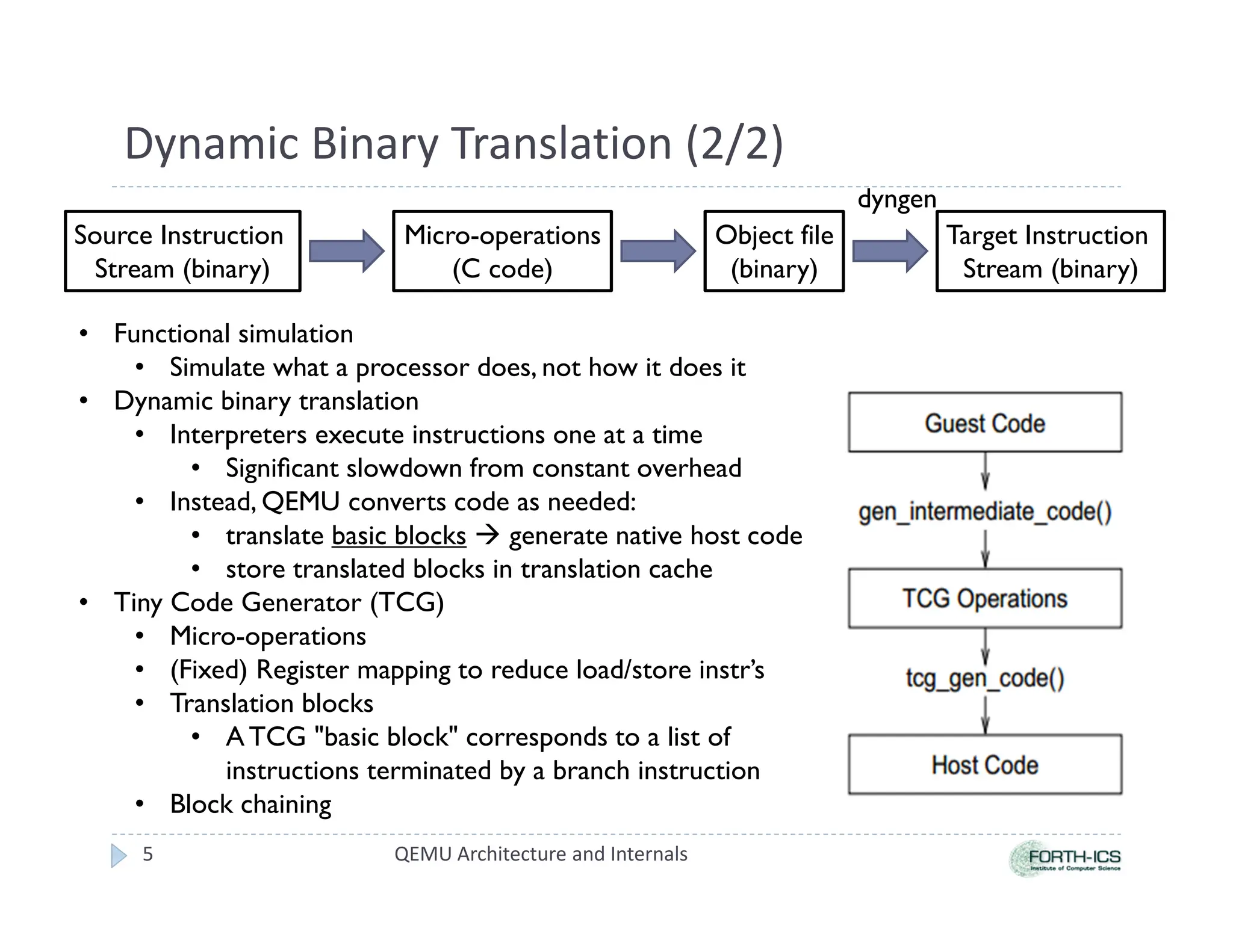

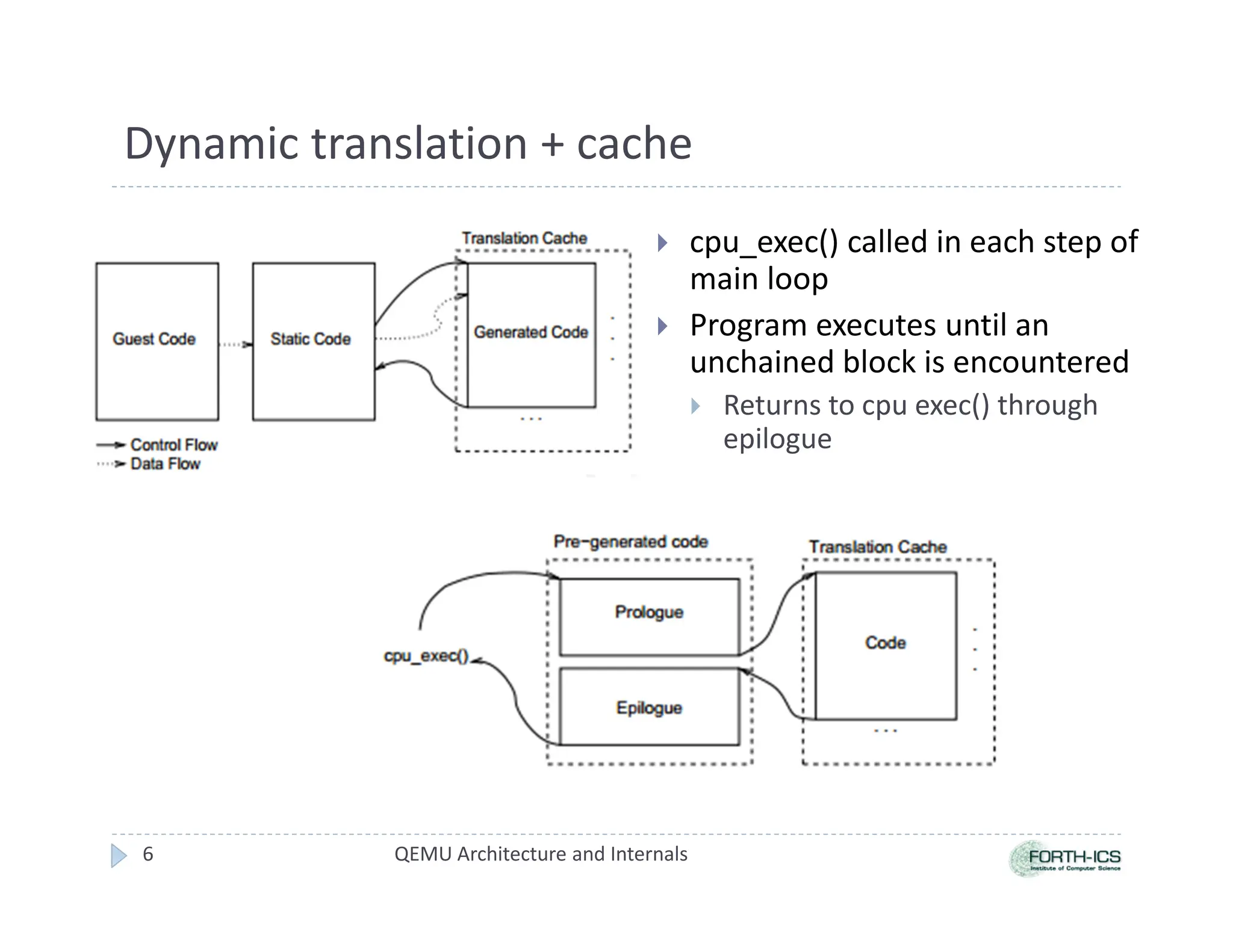

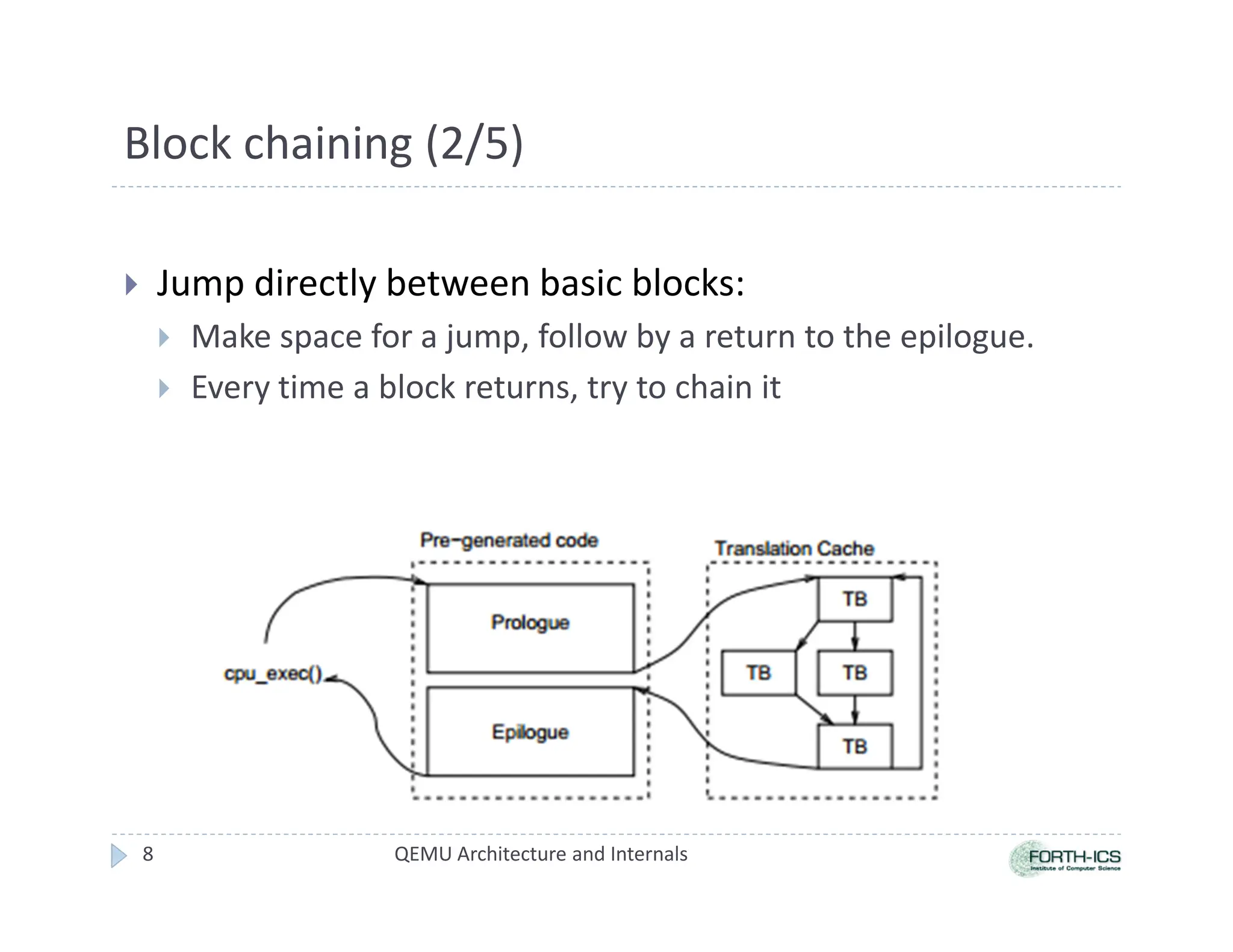

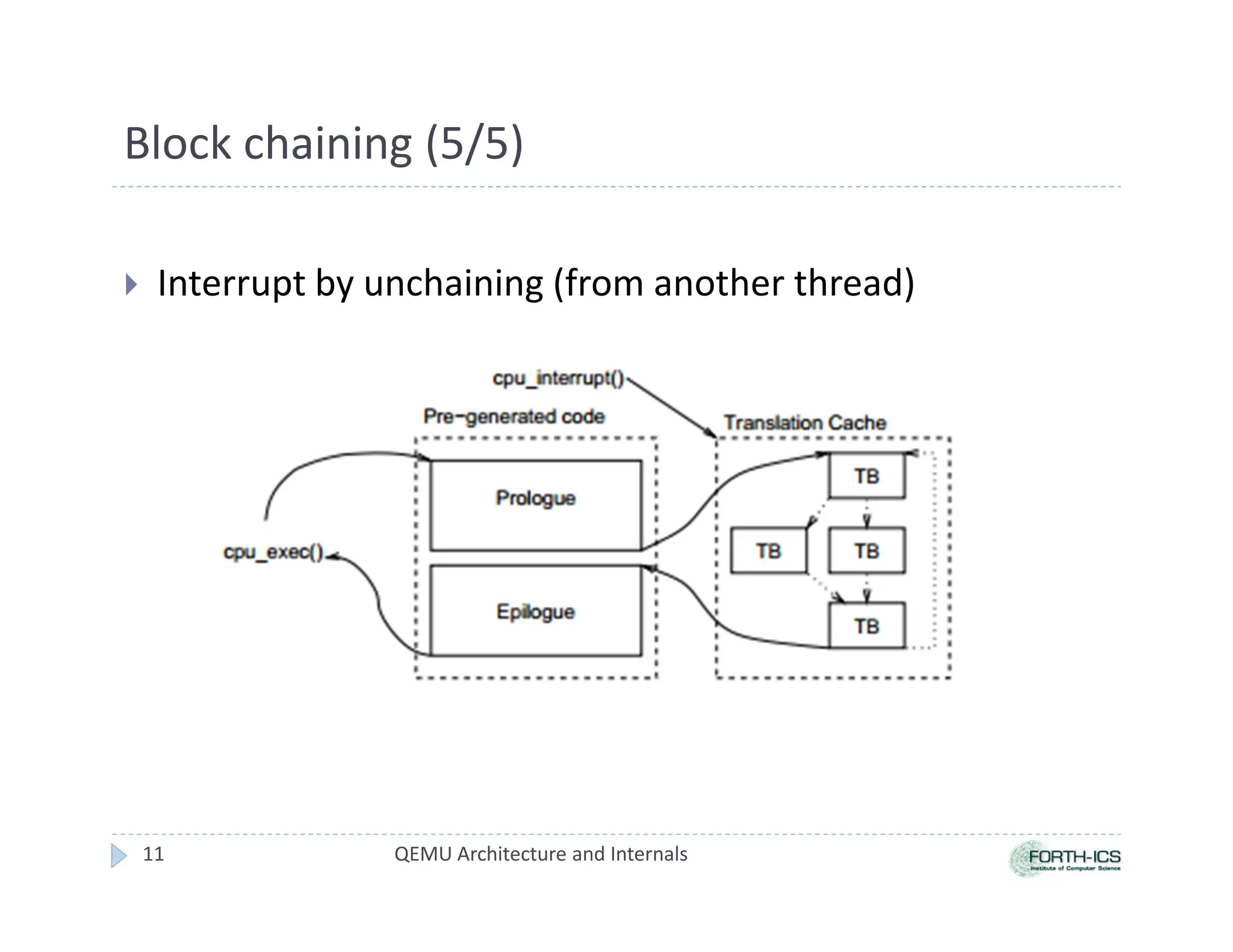

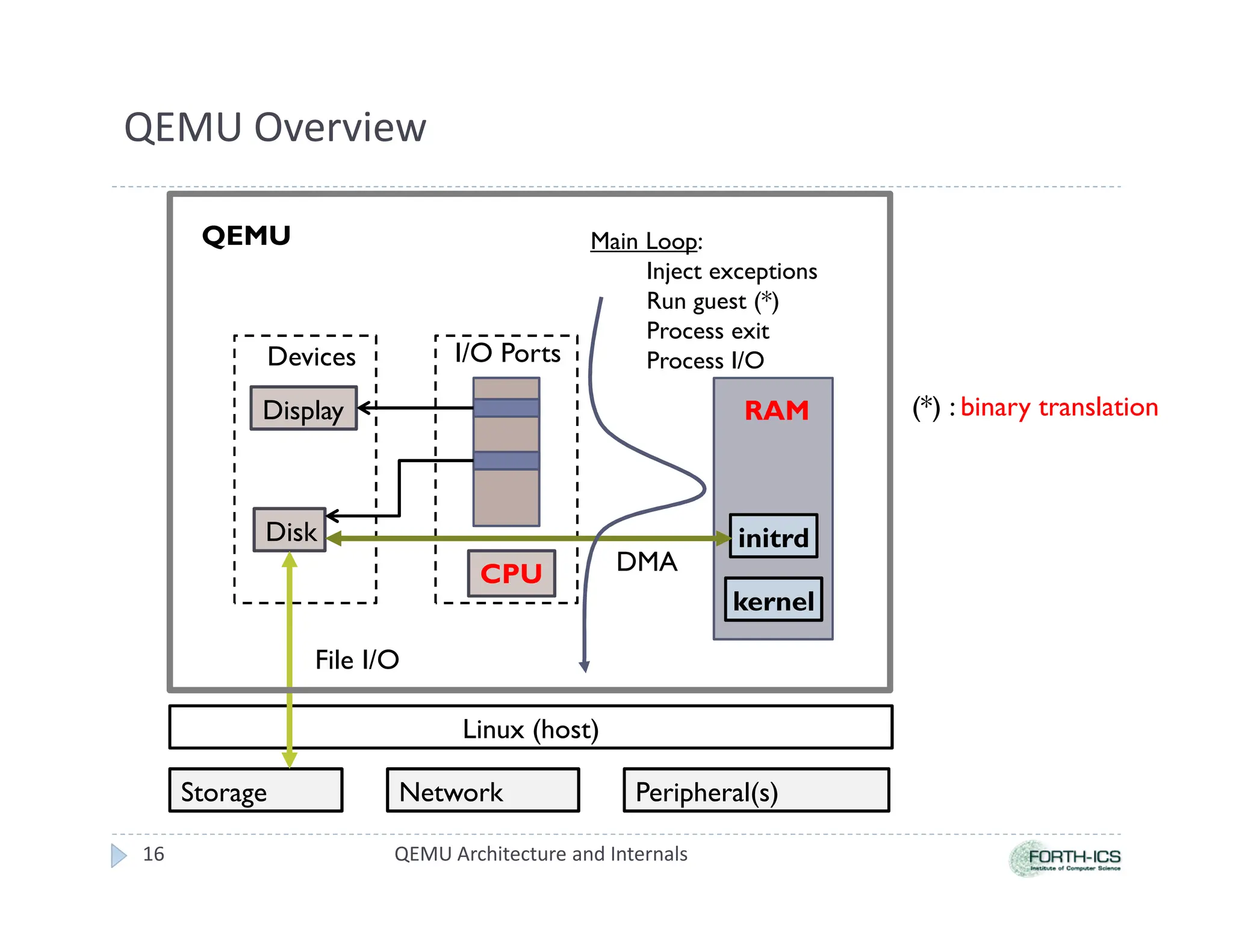

The document provides an overview of QEMU, a machine emulator and virtualizer used for system emulation and user-mode emulation. It discusses its architecture, dynamic binary translation, block chaining, and key components like memory address translation and device emulation, emphasizing its use in cross-compilation and virtualization. Additionally, the document includes examples of user-mode and system emulation for ARM architecture.

![Block chaining (4/5)

[1]

[2]

[3]

[4]

[5]

QEMU Architecture and Internals

10](https://image.slidesharecdn.com/qemuinternals-241116122717-07cbc961/75/qemu-architecture-and-internals-How-it-works-10-2048.jpg)

![QEMU Storage Stack

17 QEMU Architecture and Internals

[ source: Stefan Hajnoczi, - IBM LinuxTechnology Center, 2011]](https://image.slidesharecdn.com/qemuinternals-241116122717-07cbc961/75/qemu-architecture-and-internals-How-it-works-17-2048.jpg)