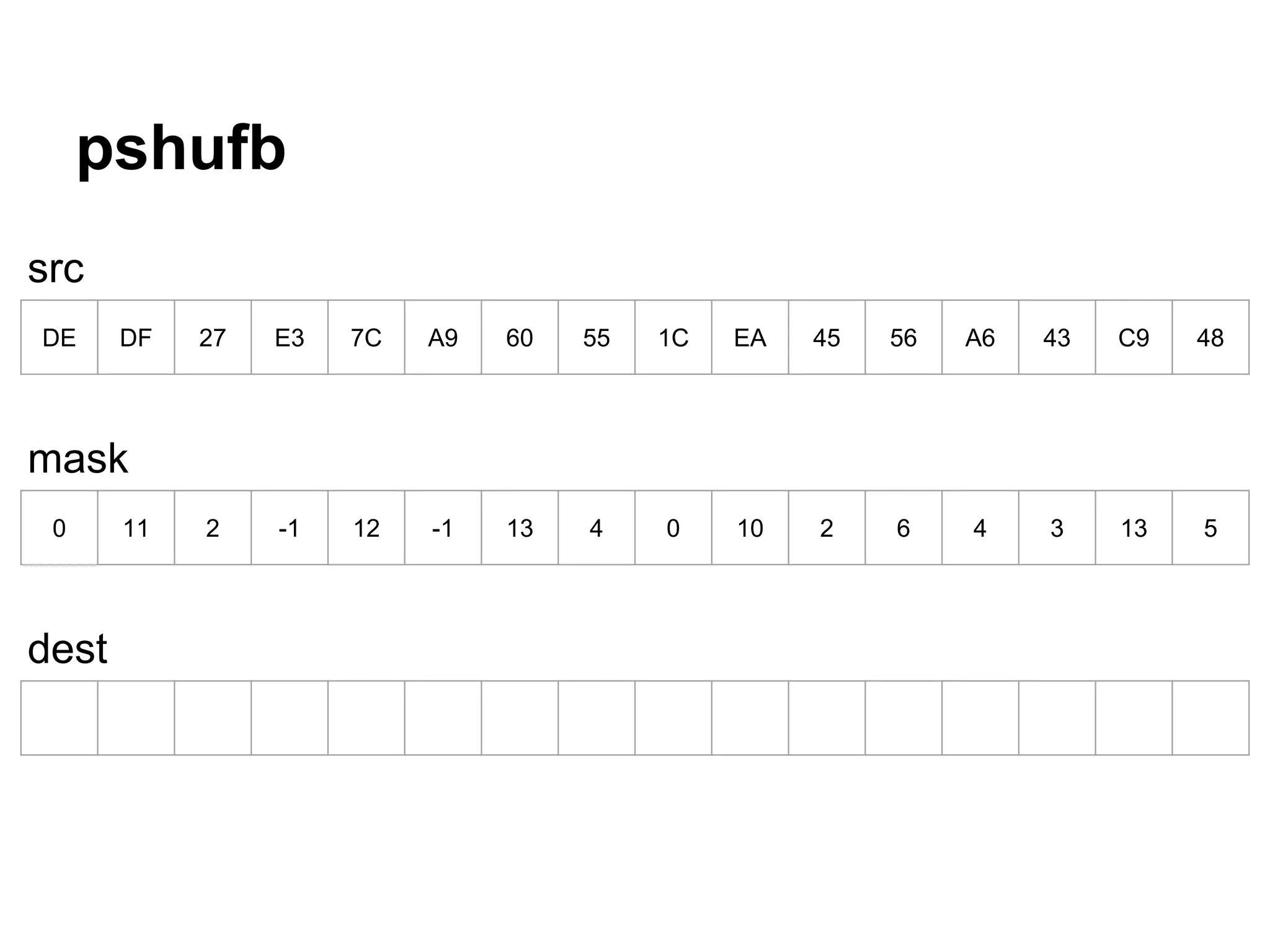

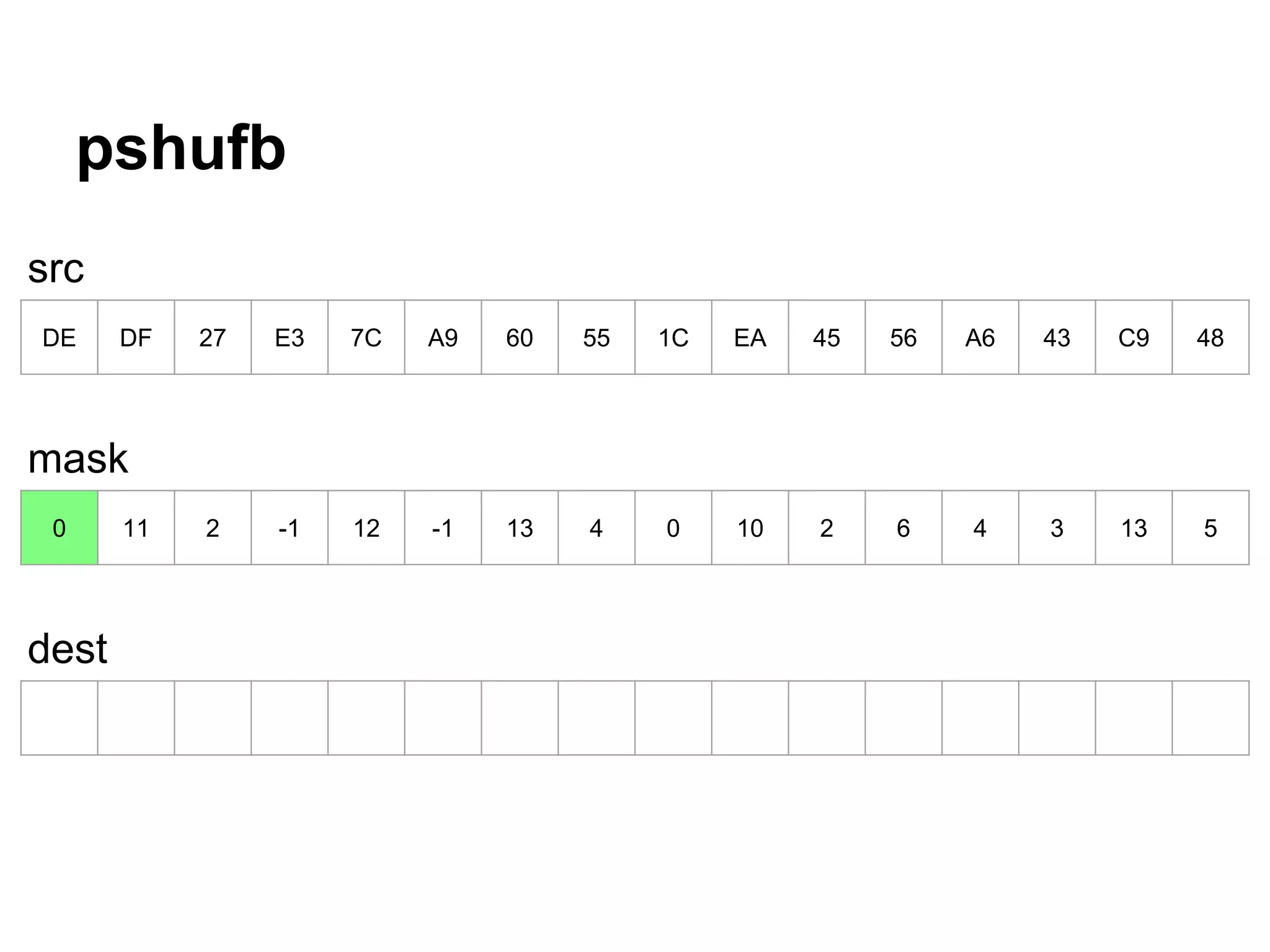

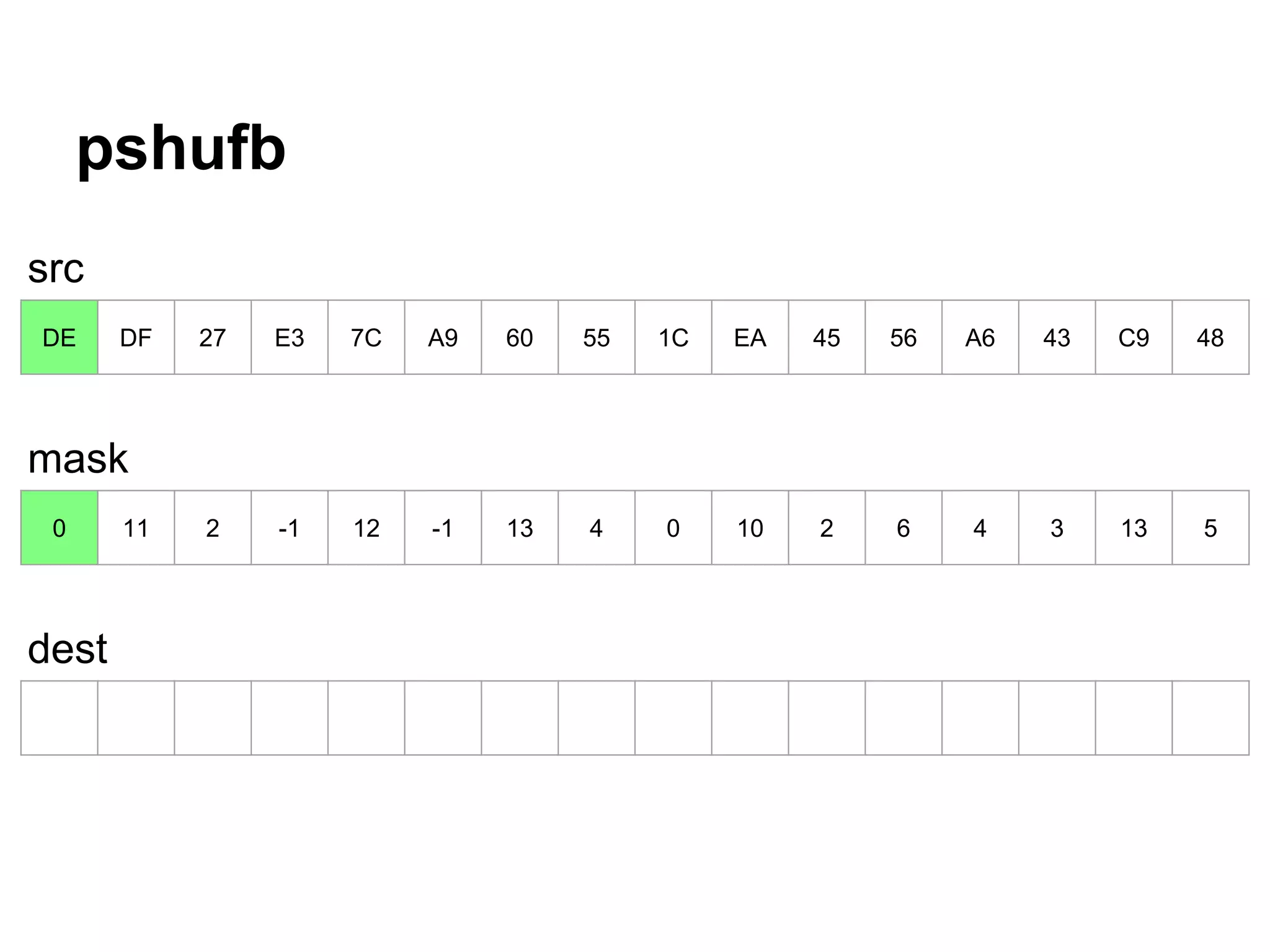

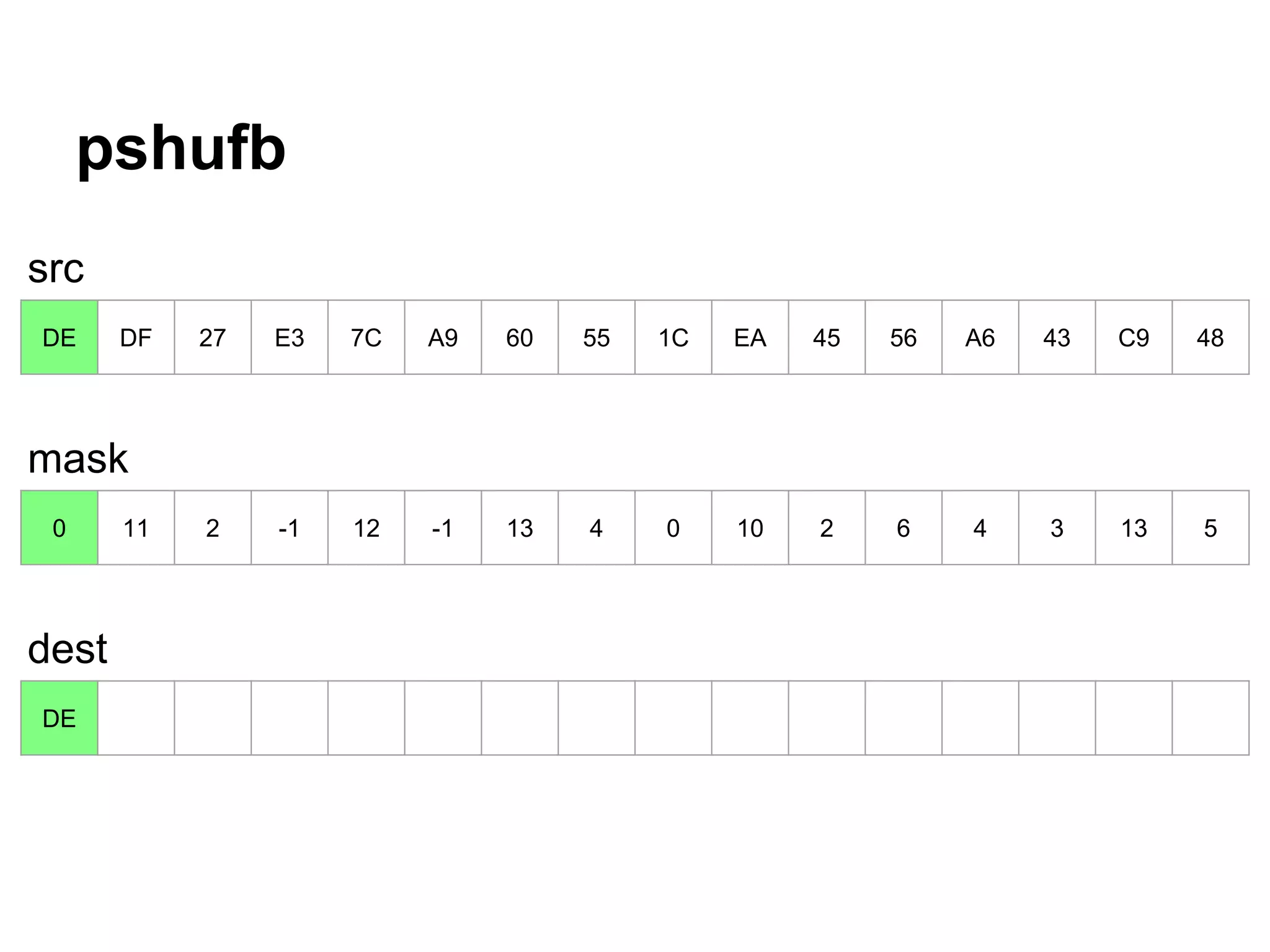

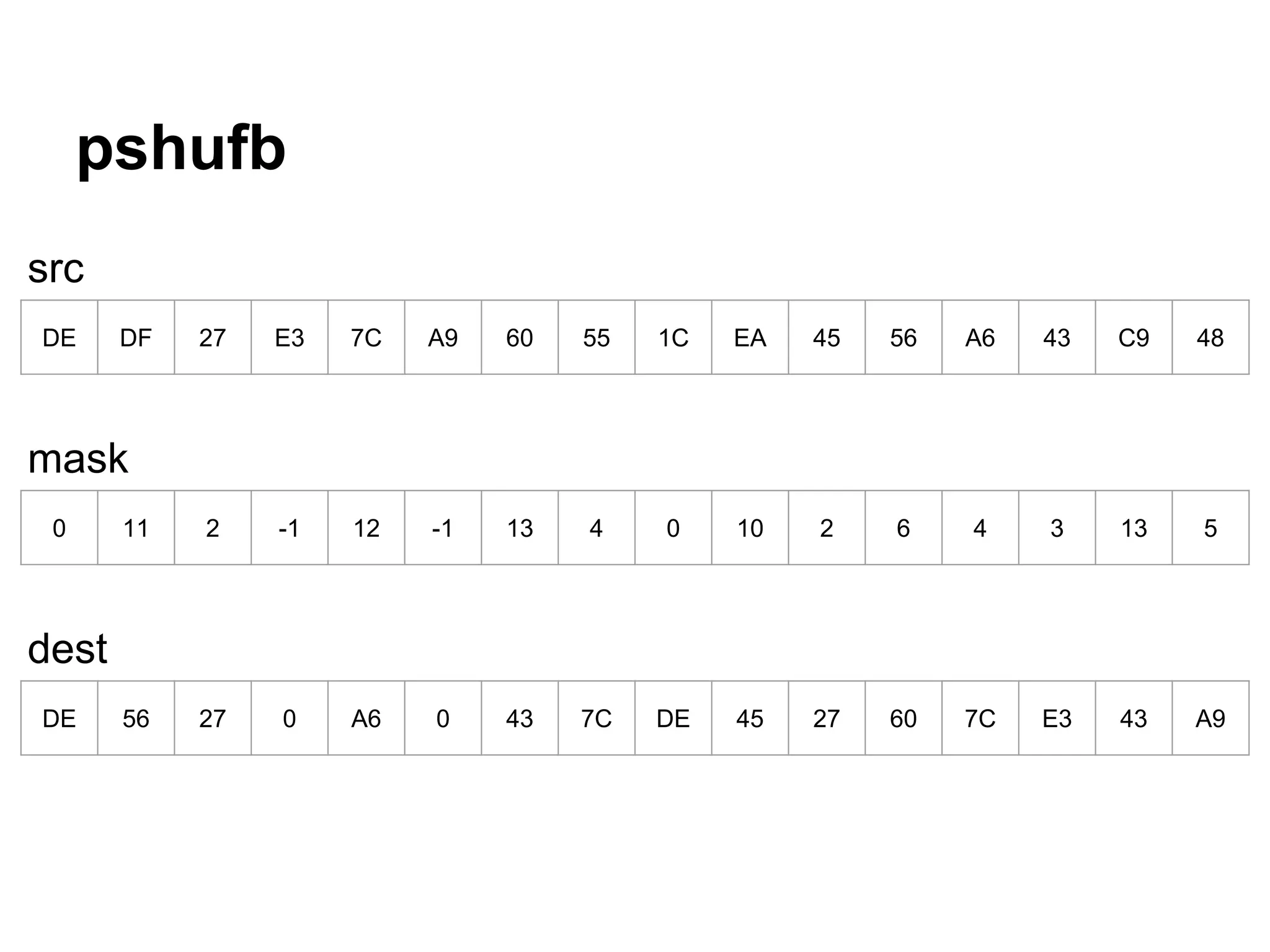

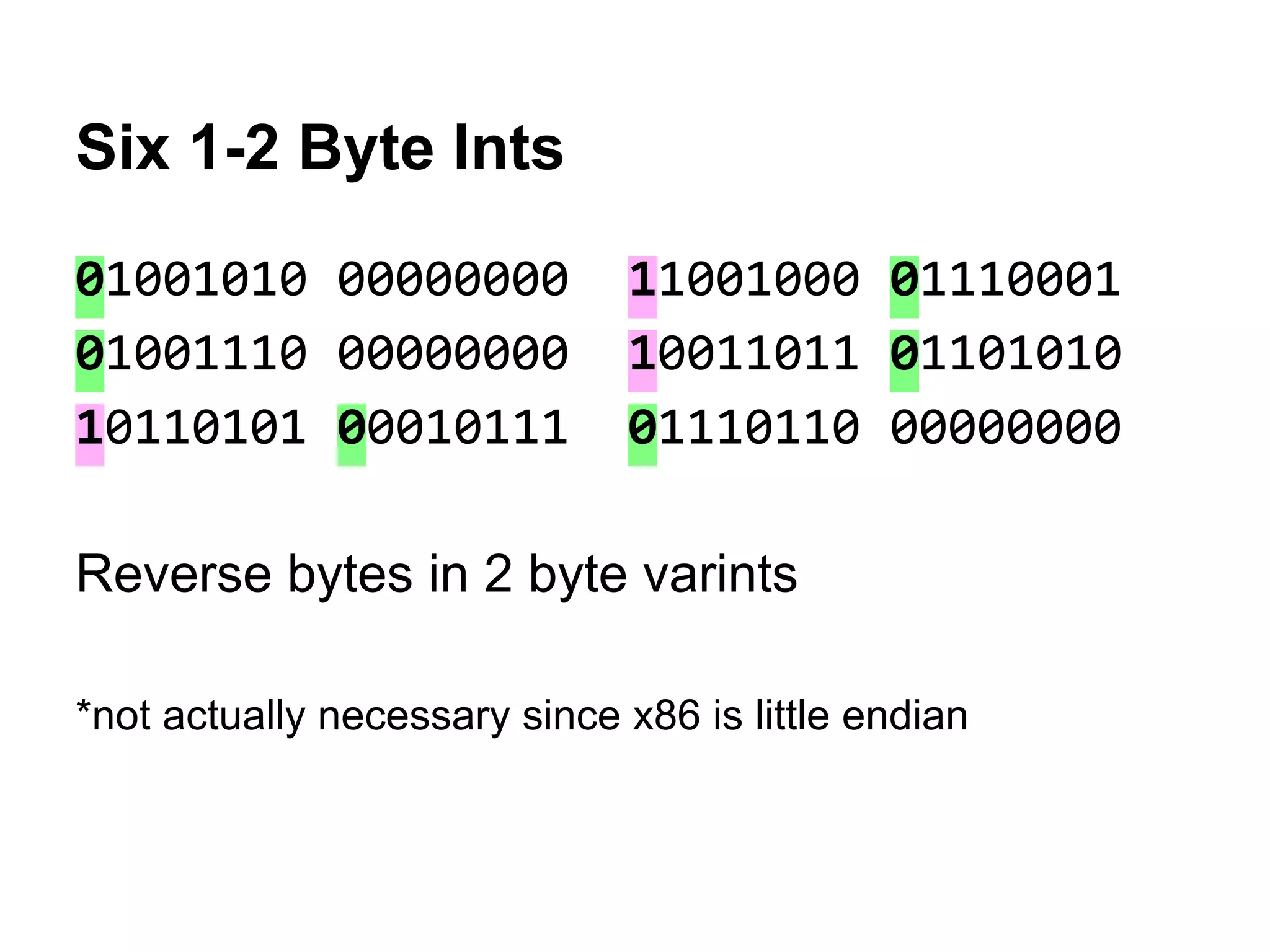

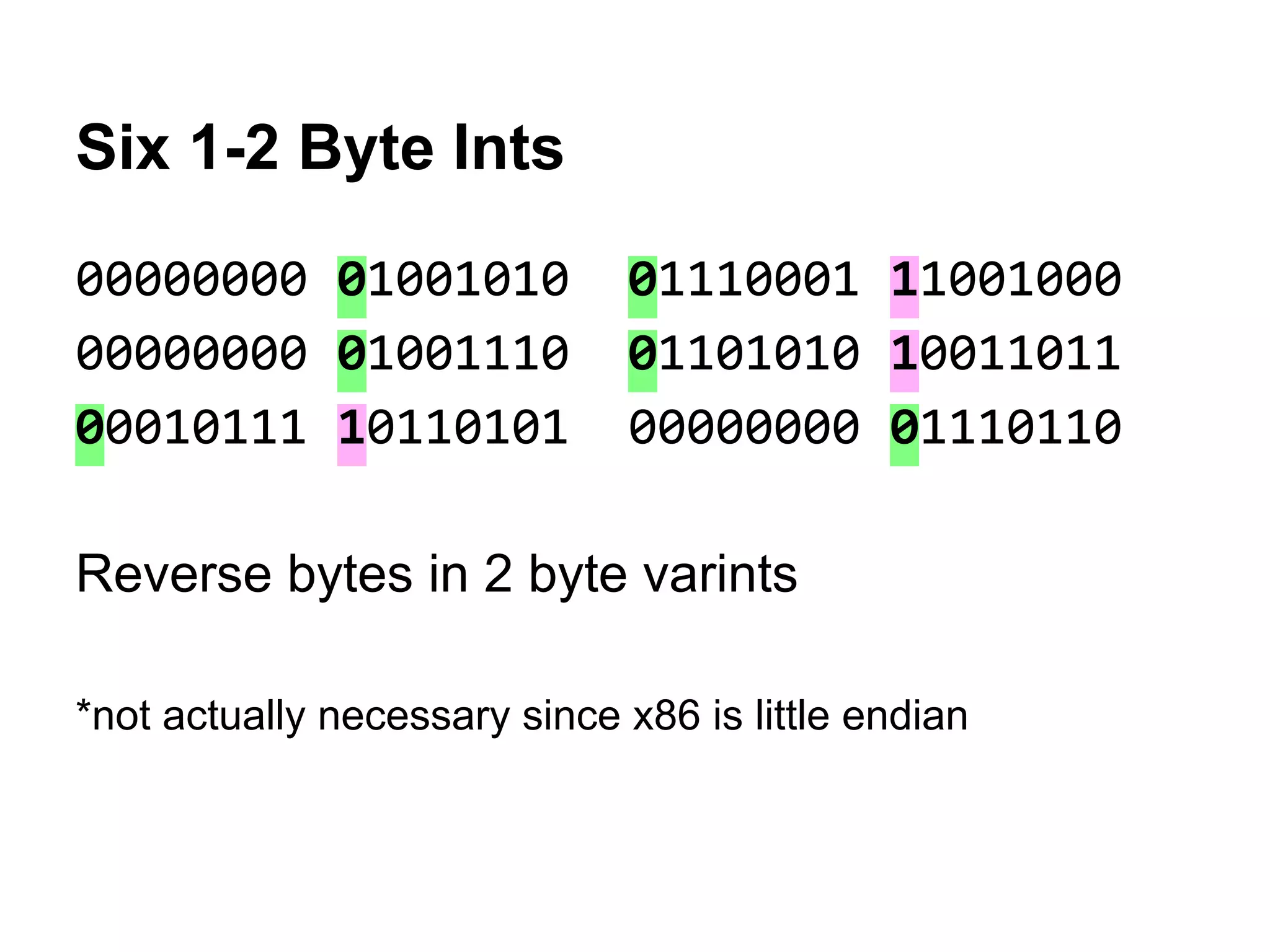

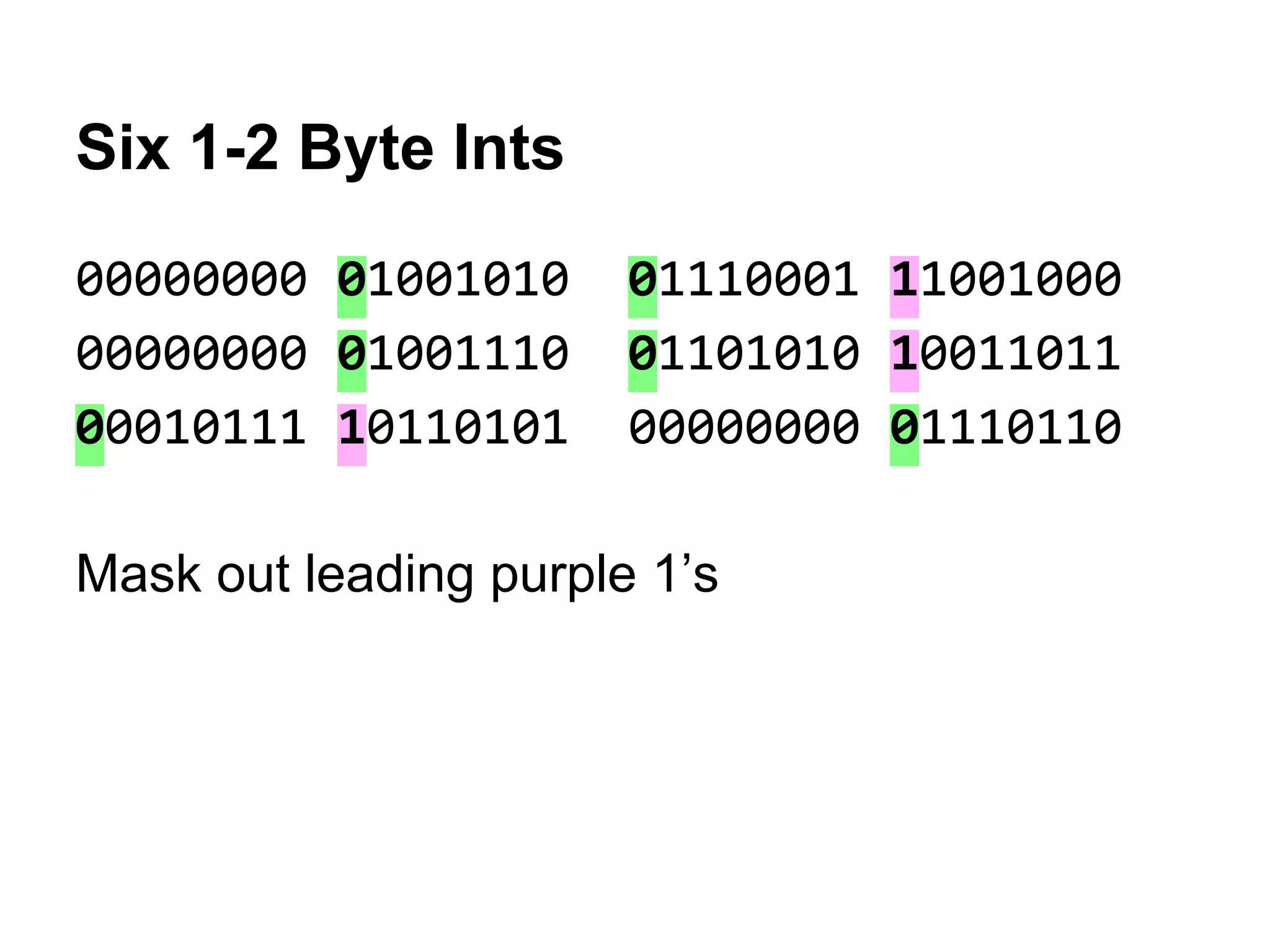

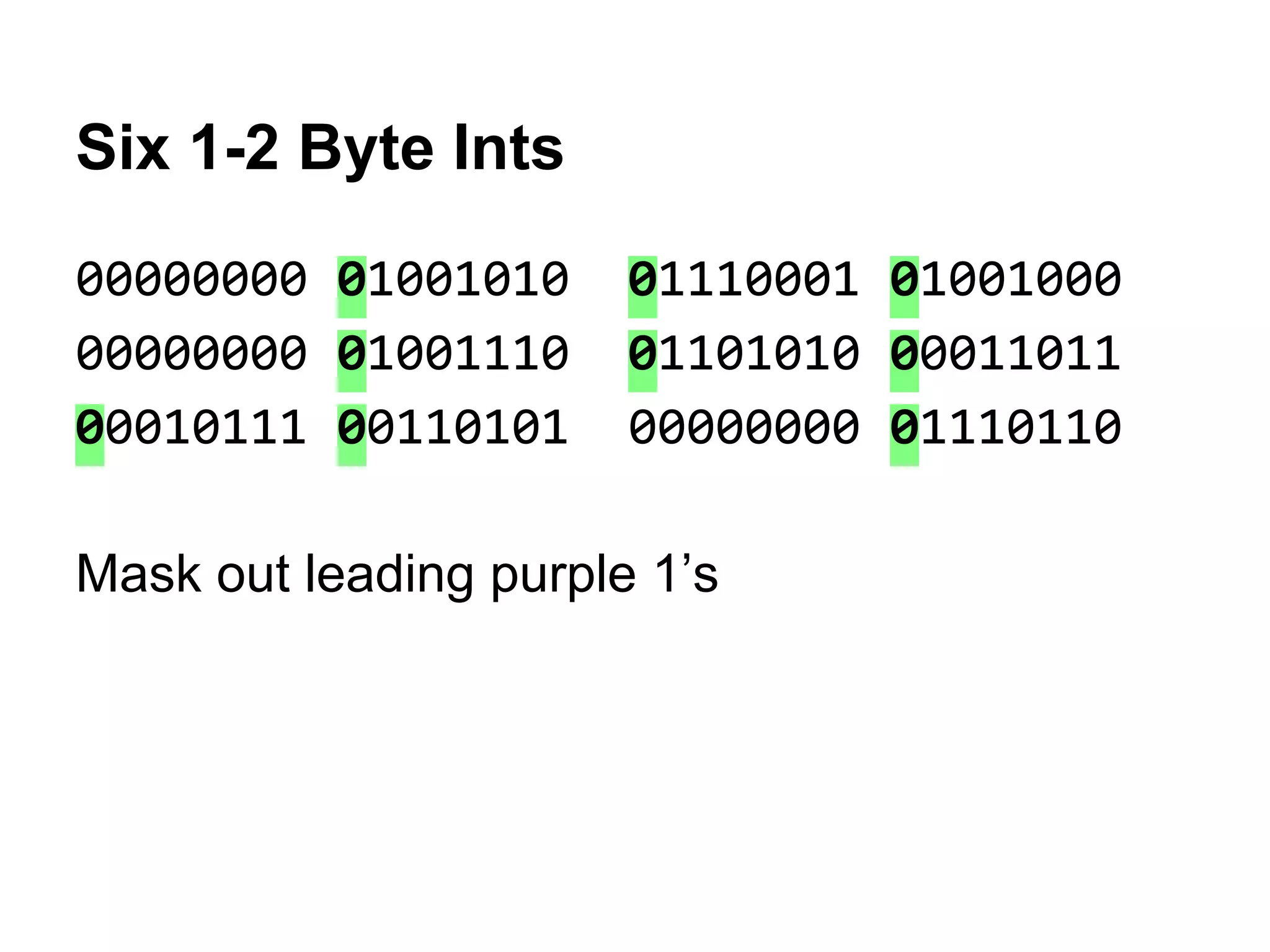

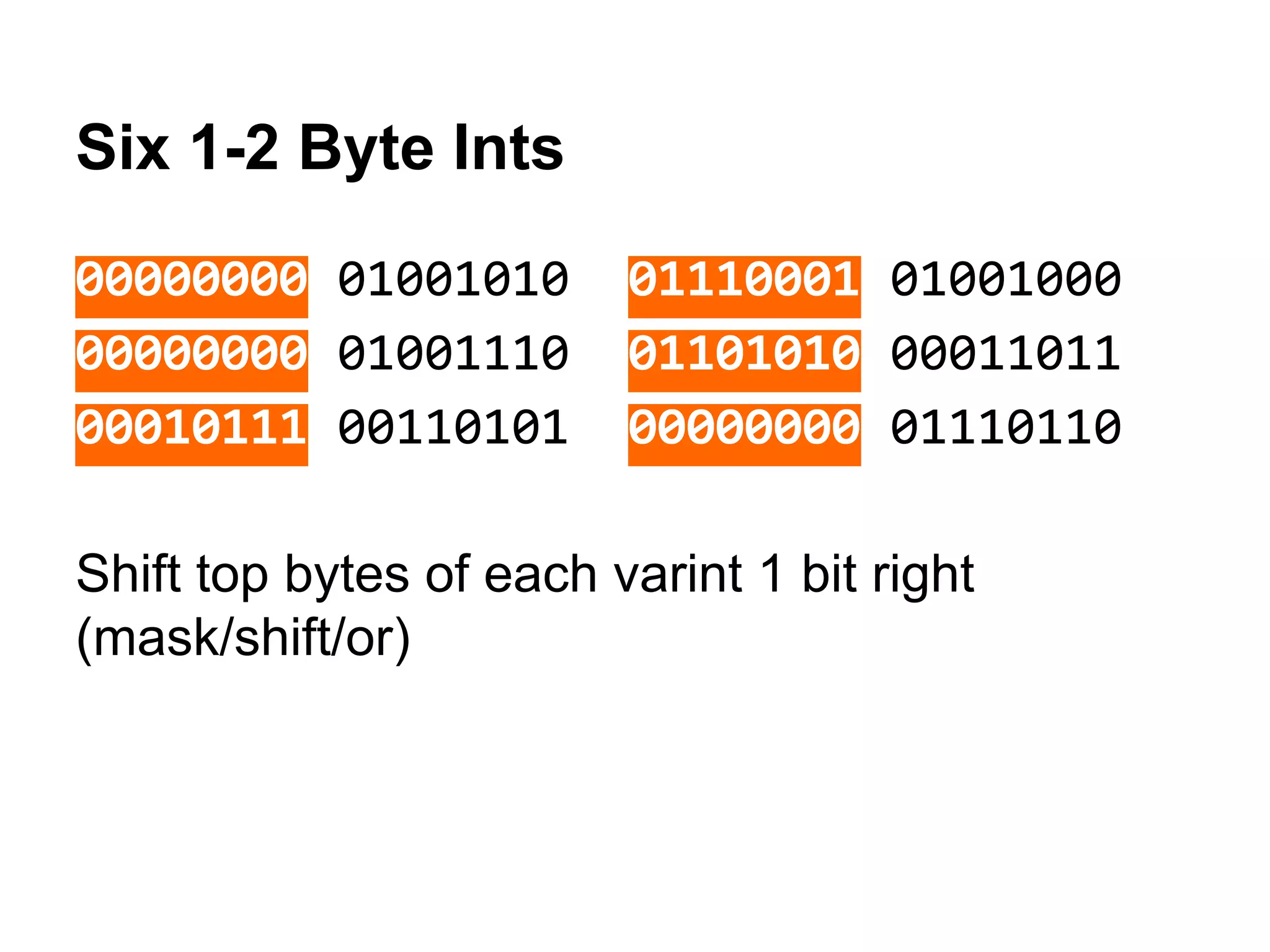

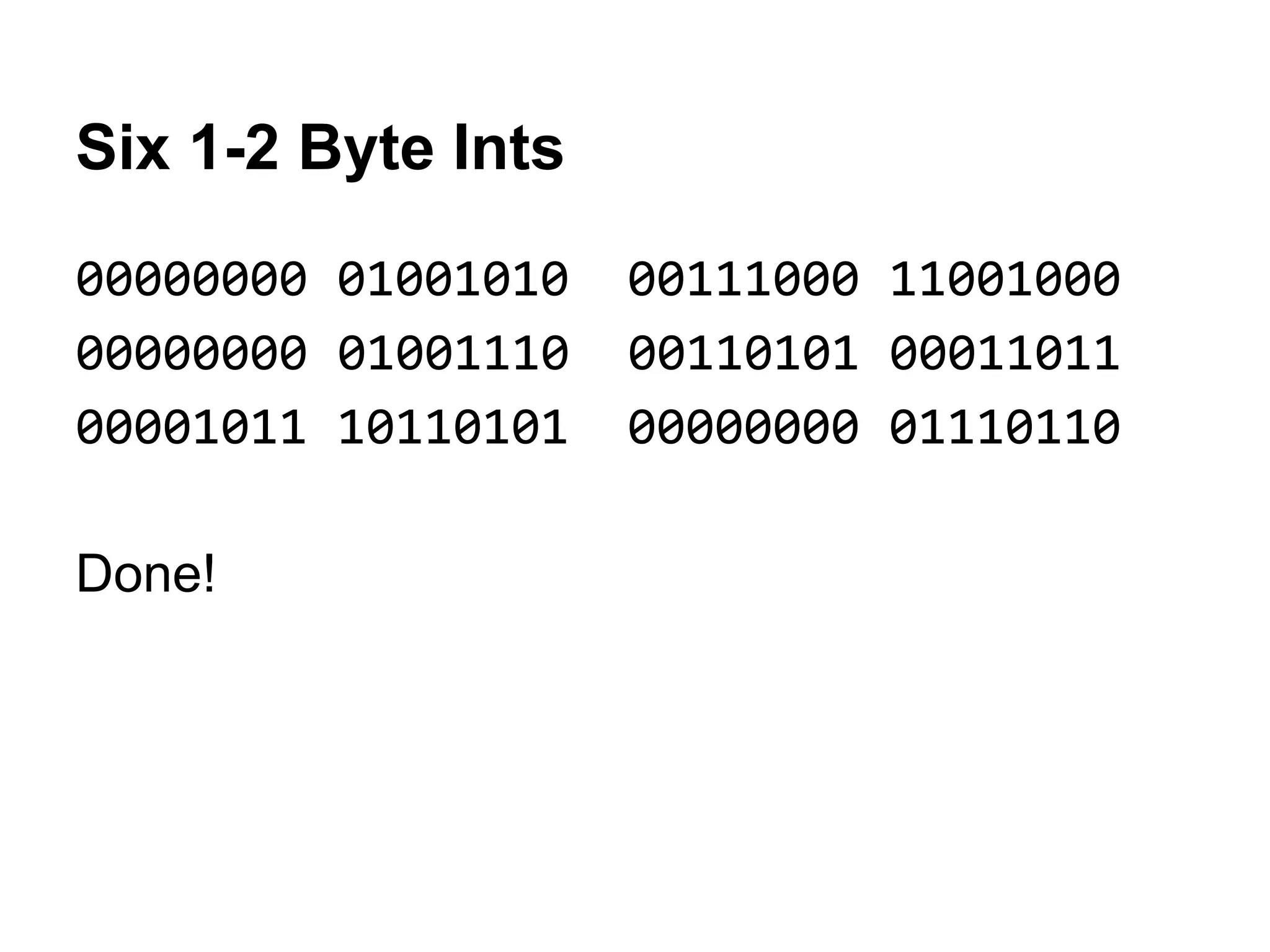

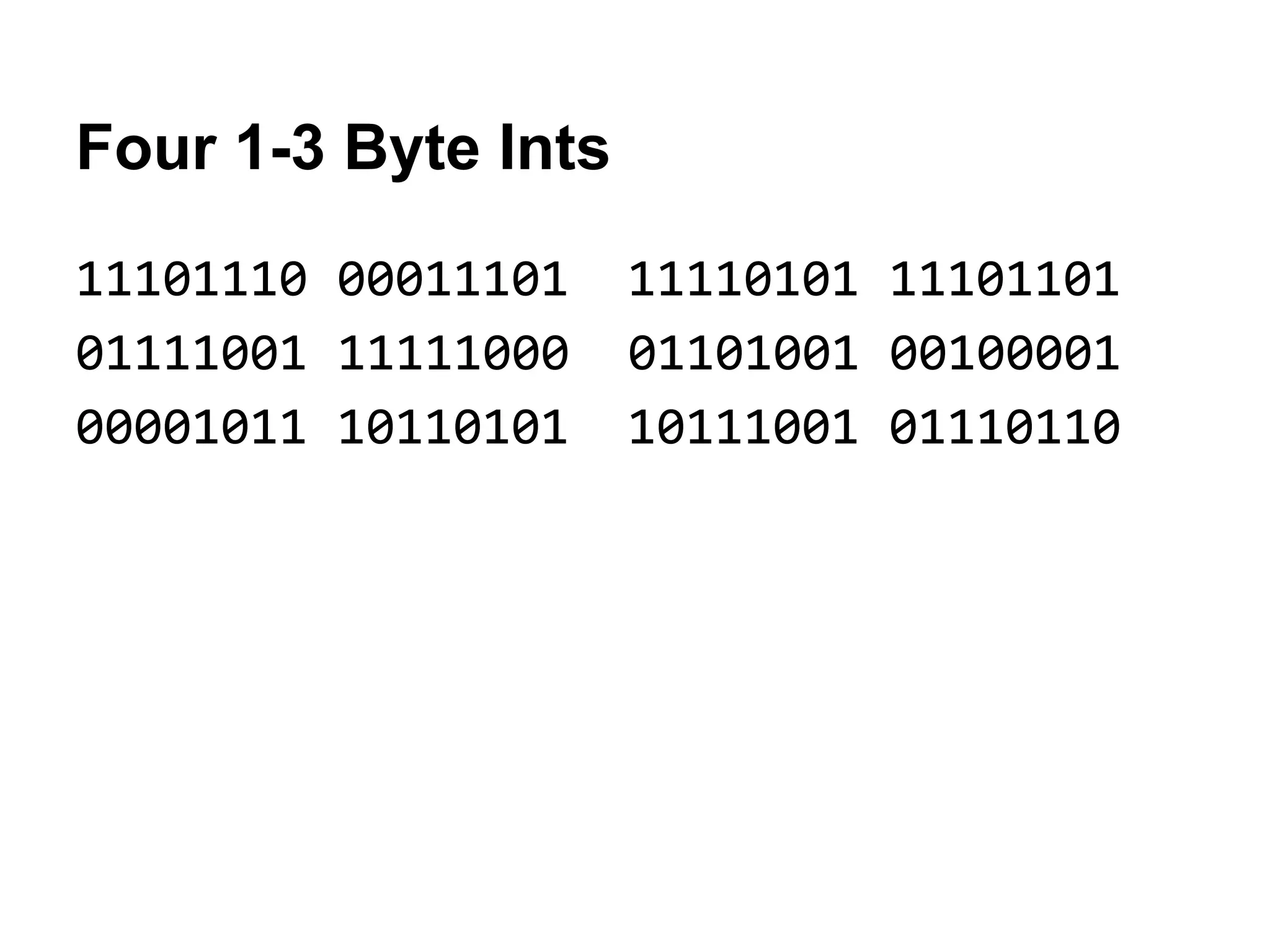

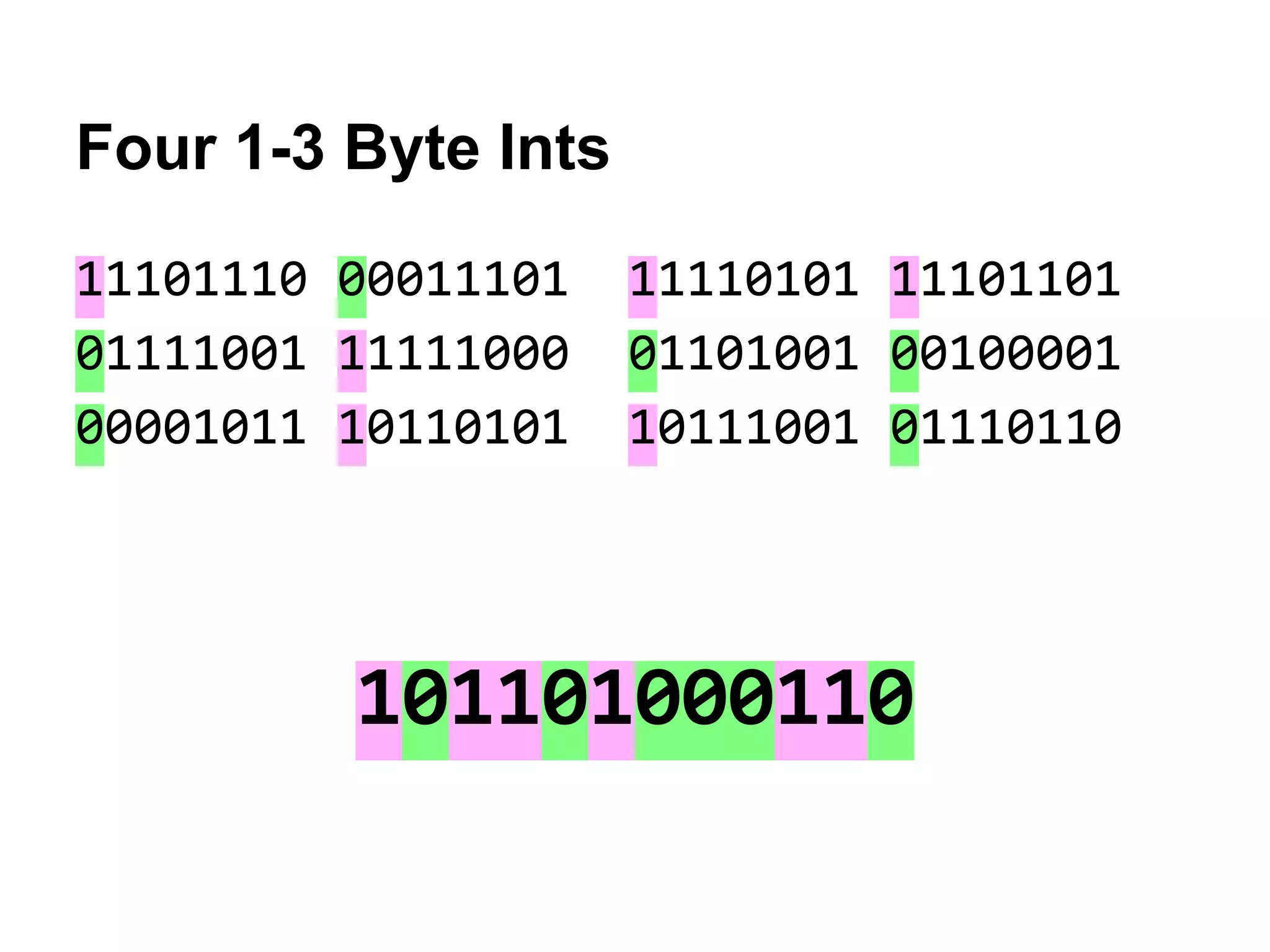

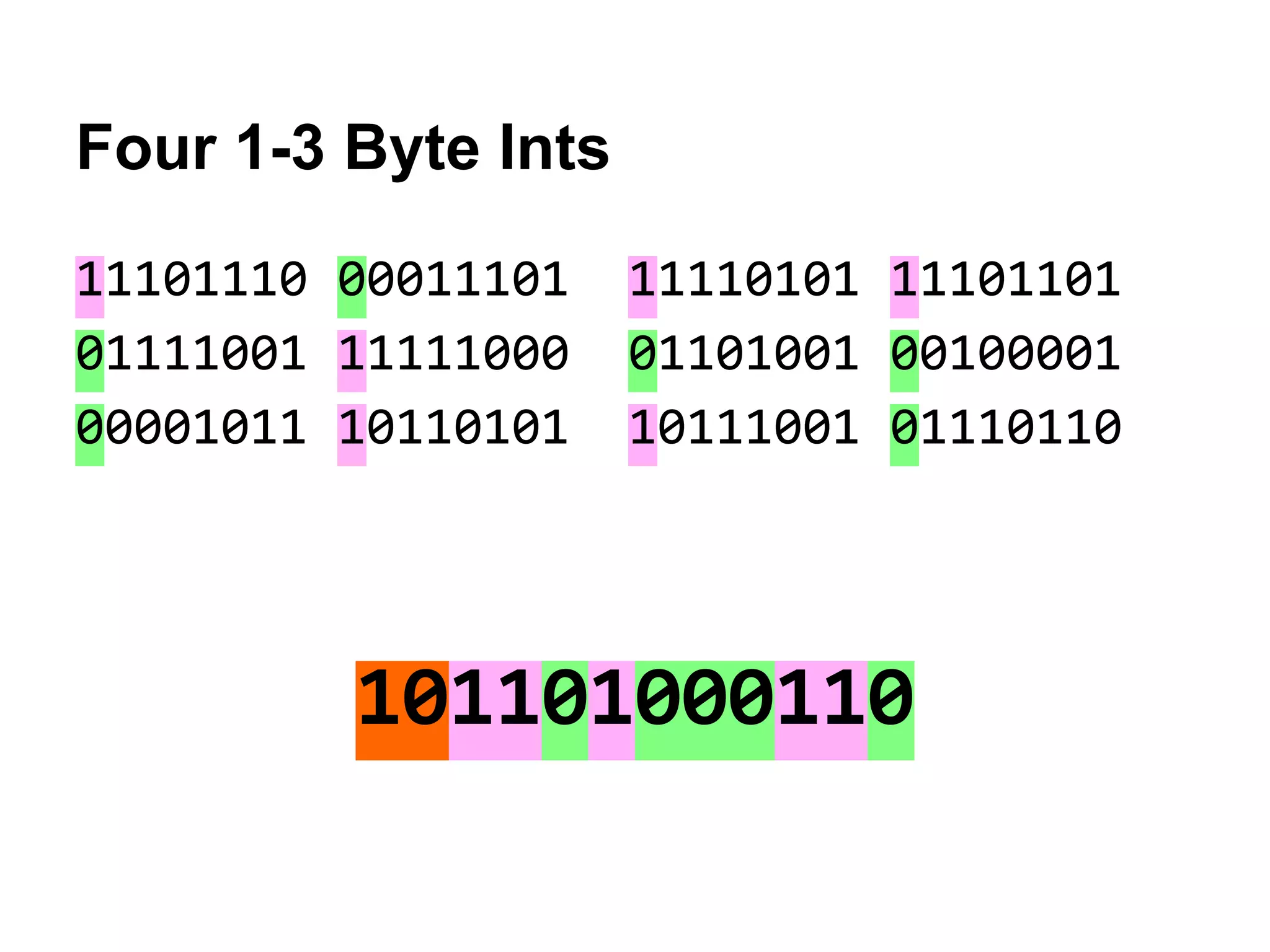

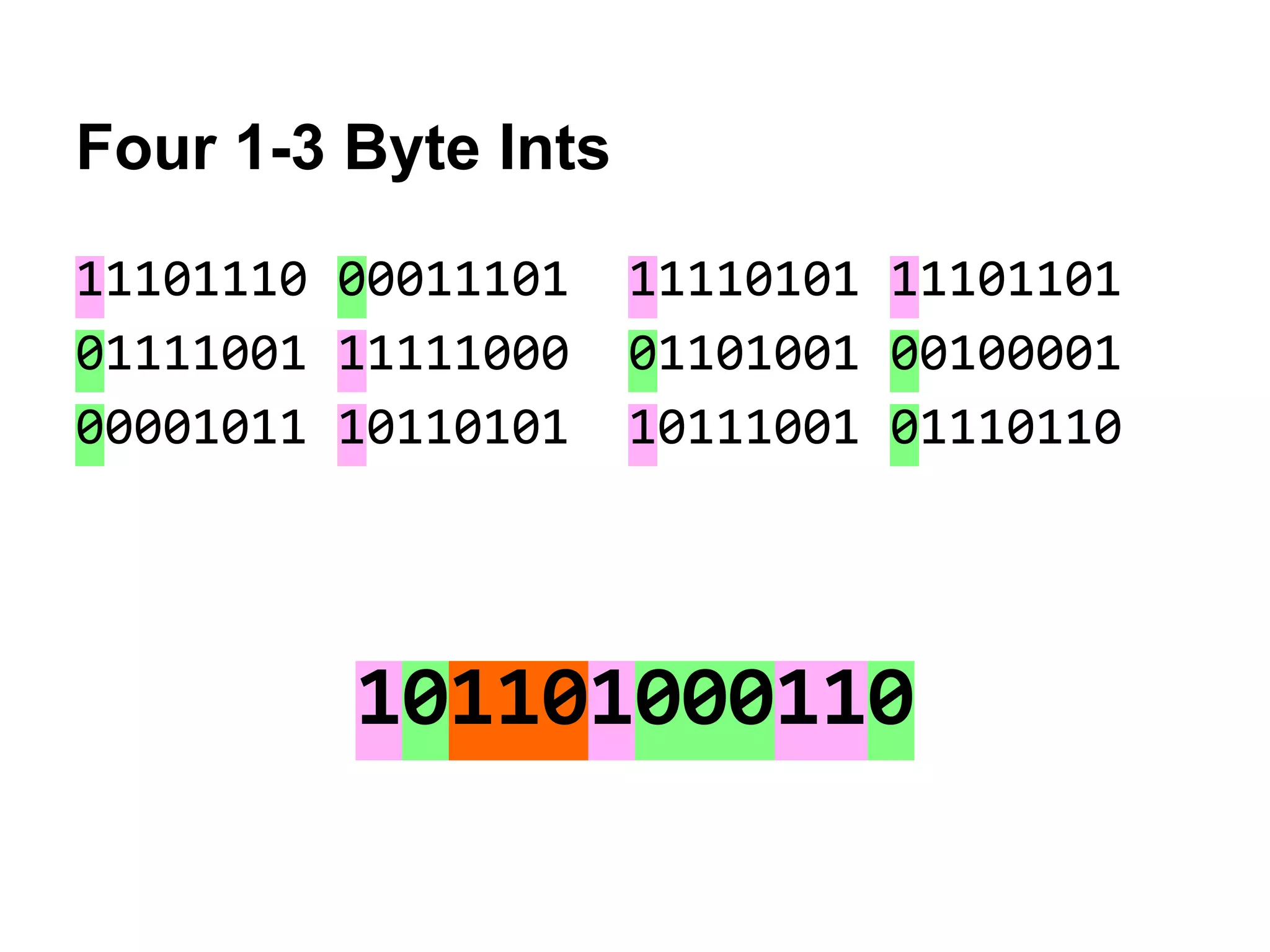

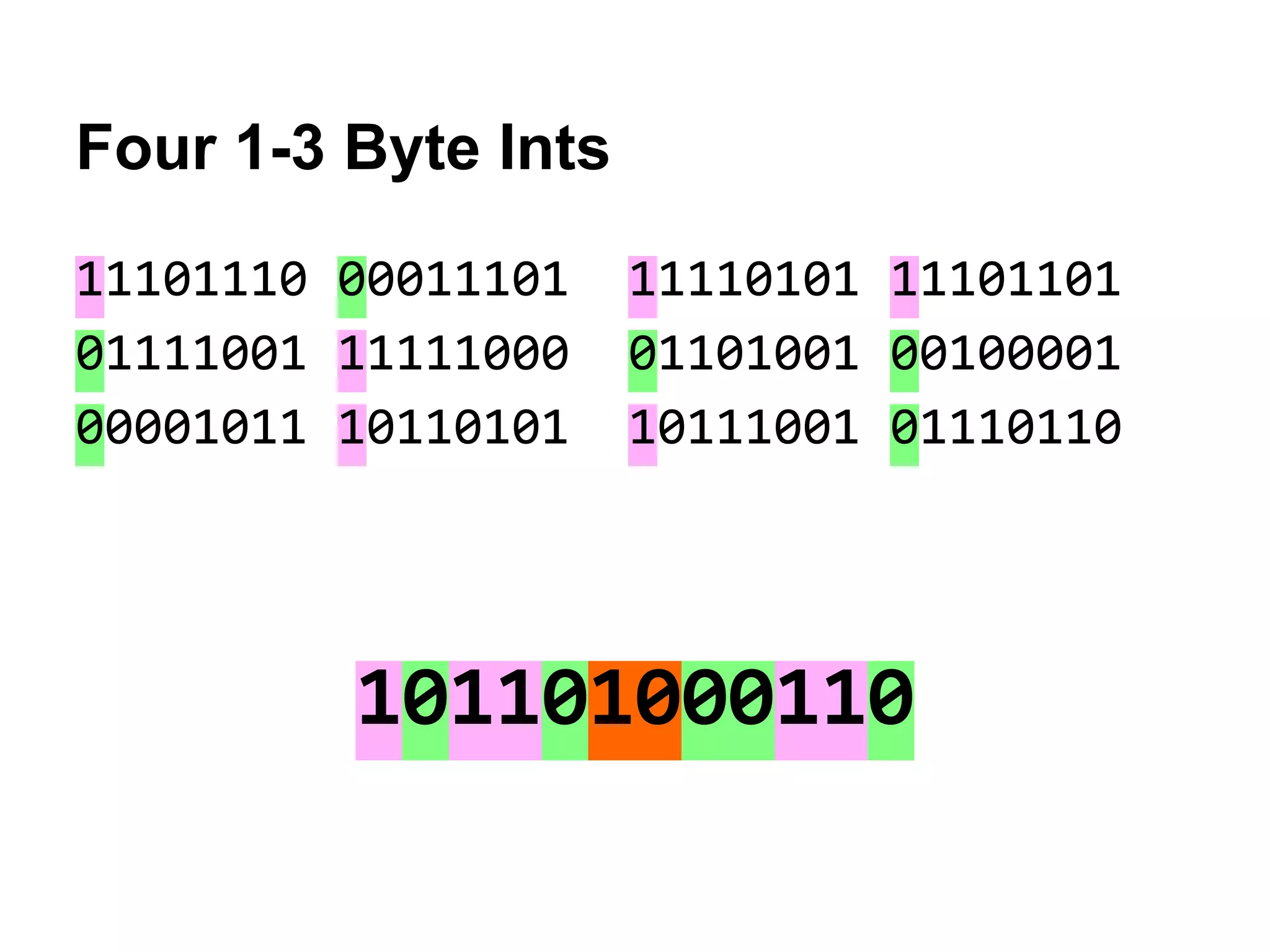

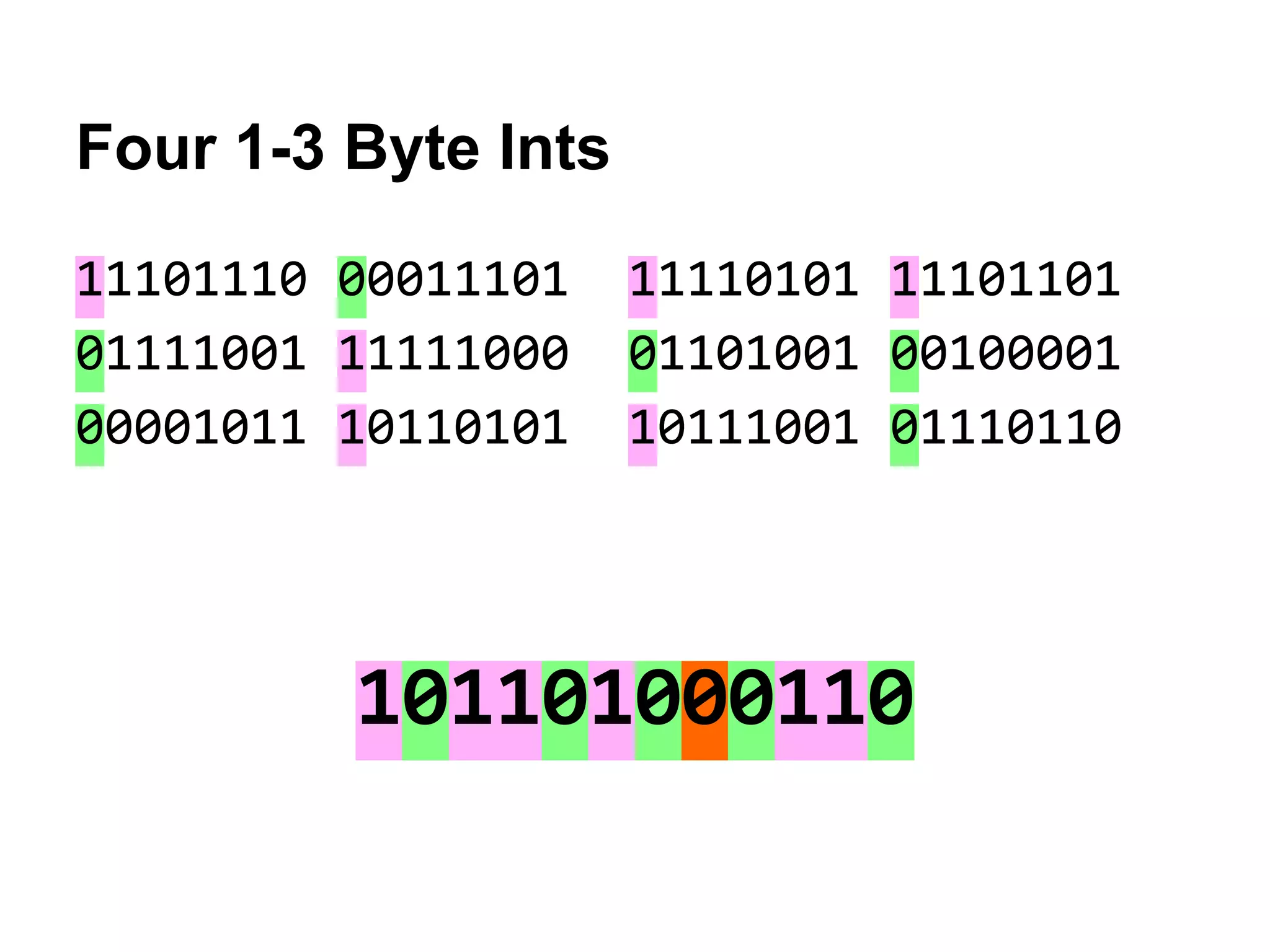

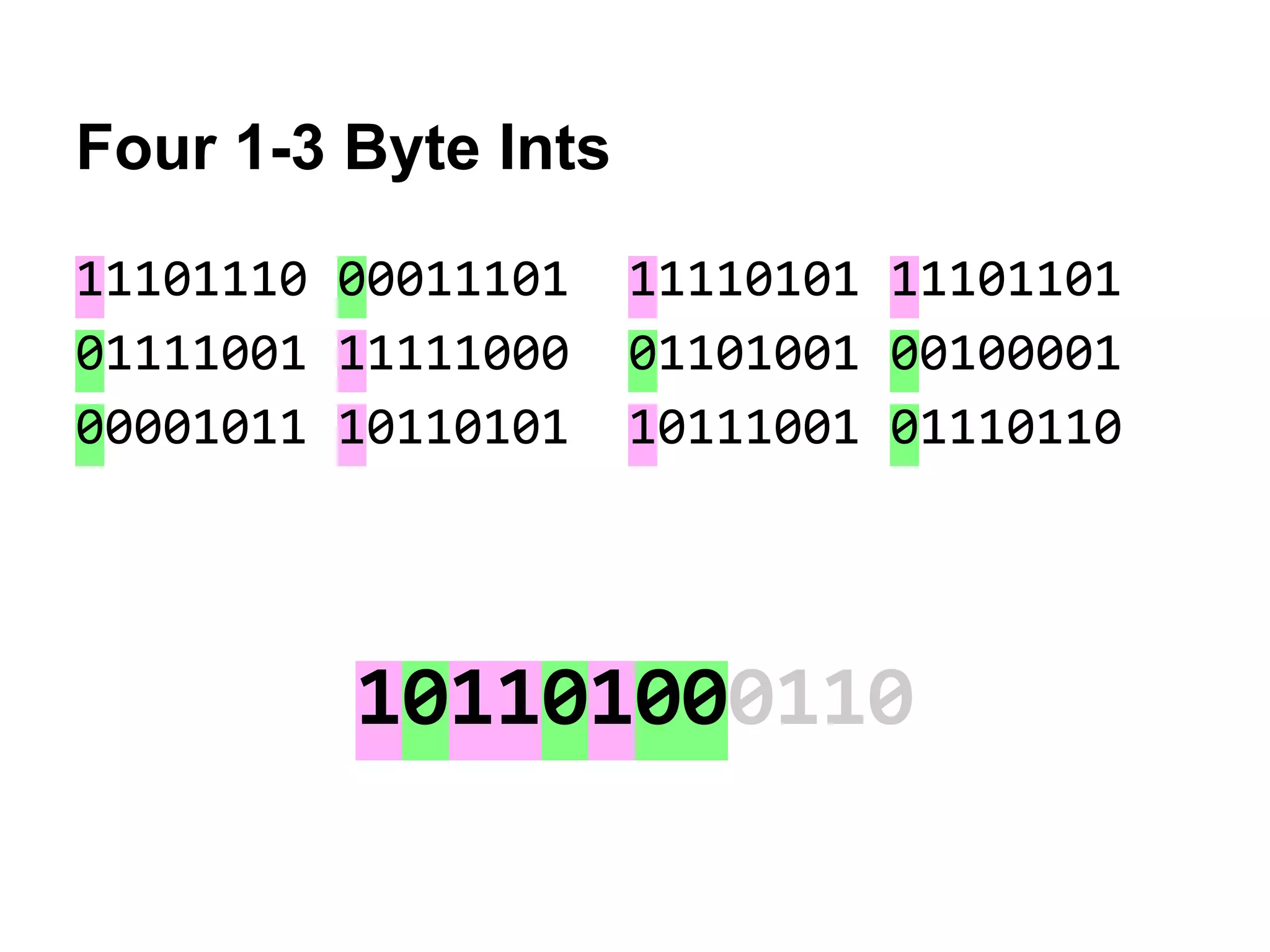

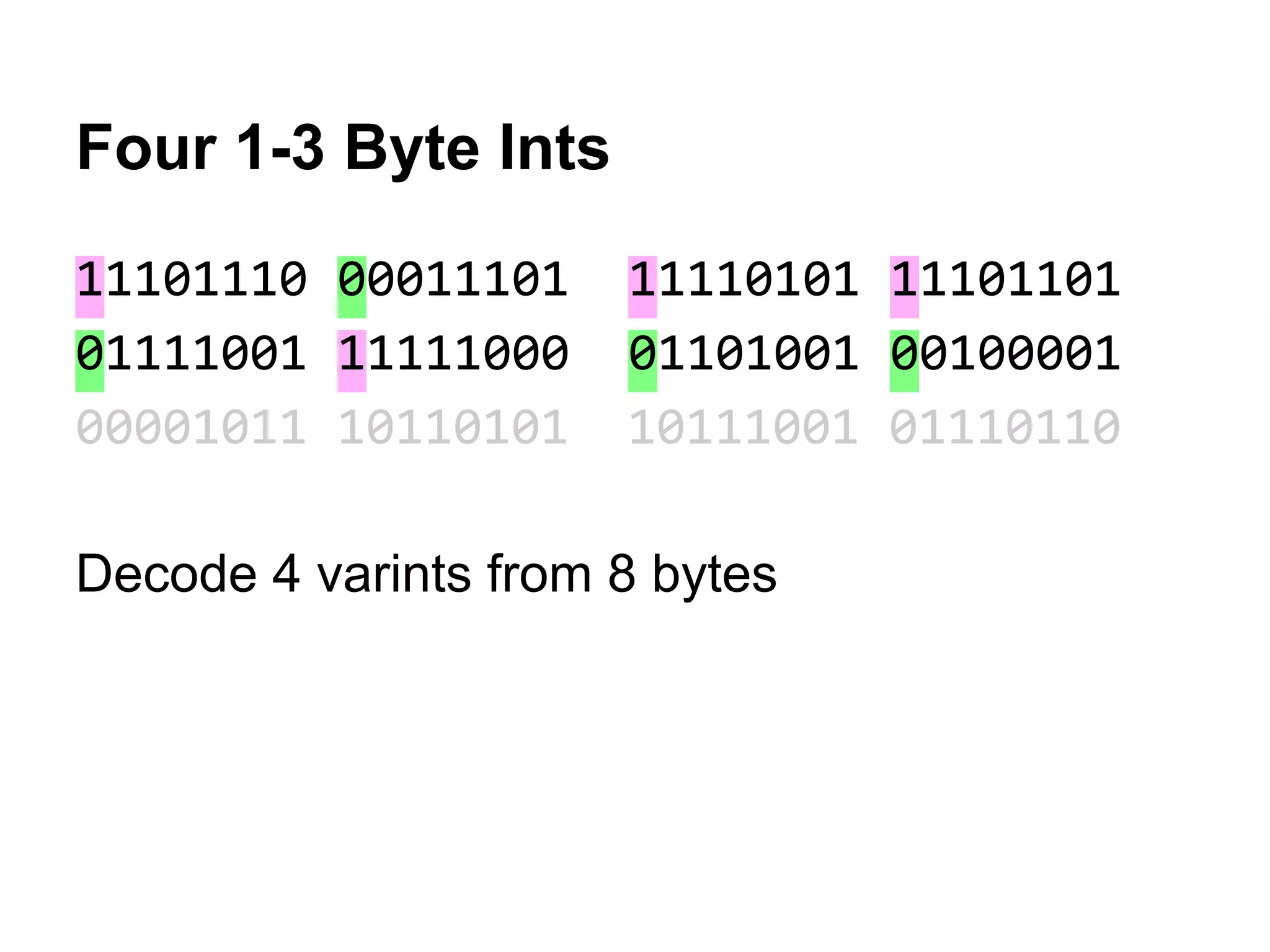

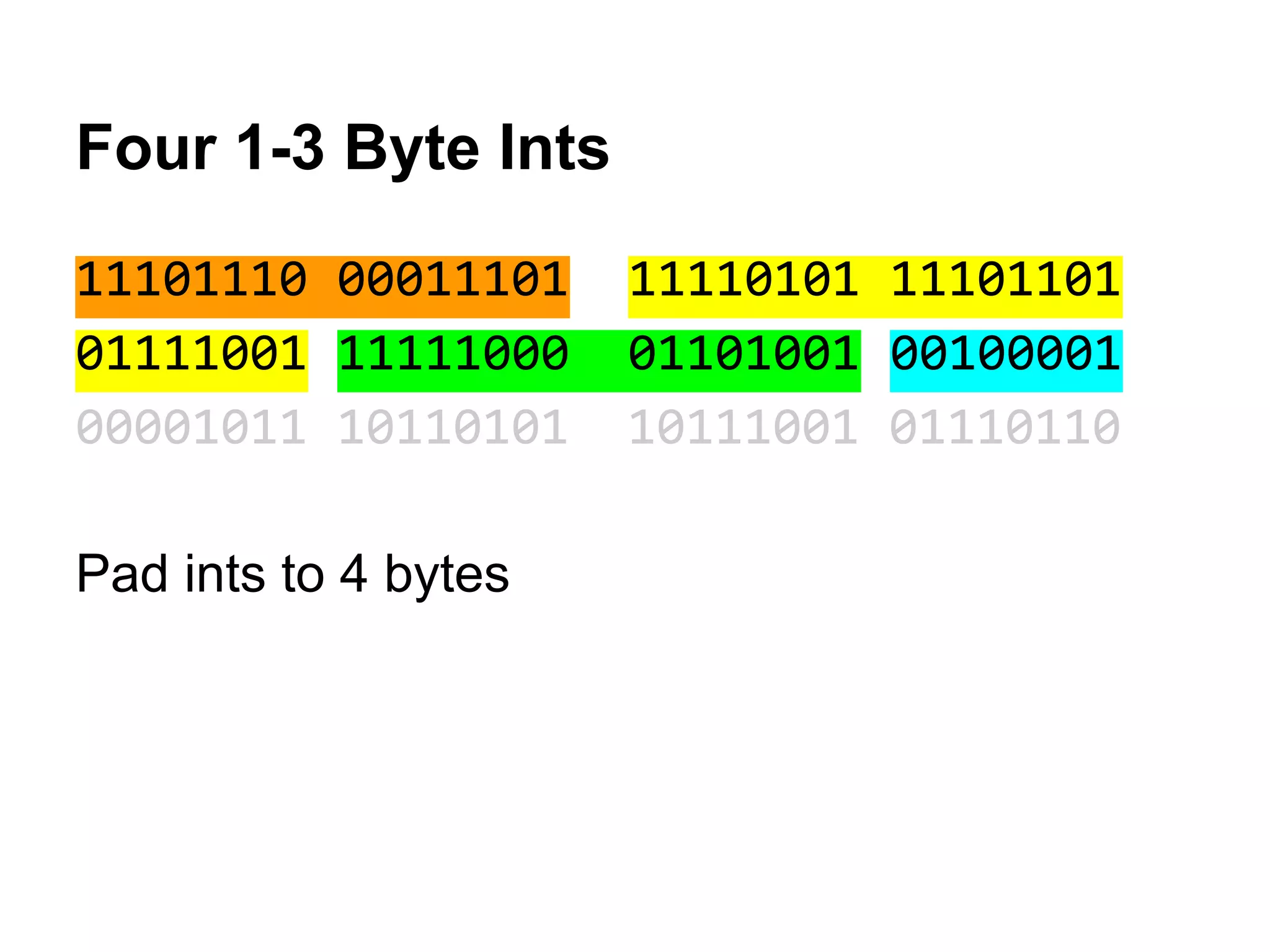

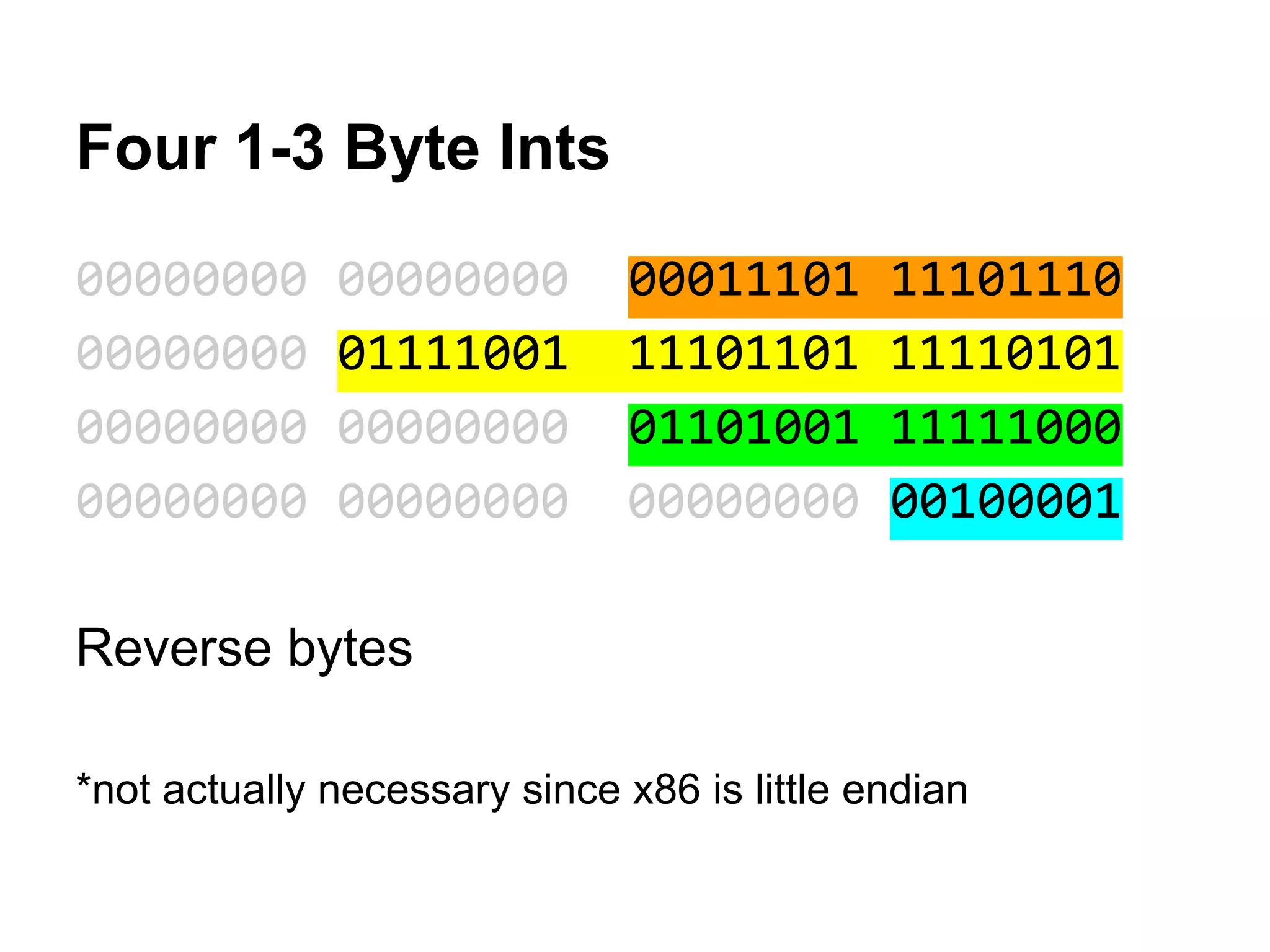

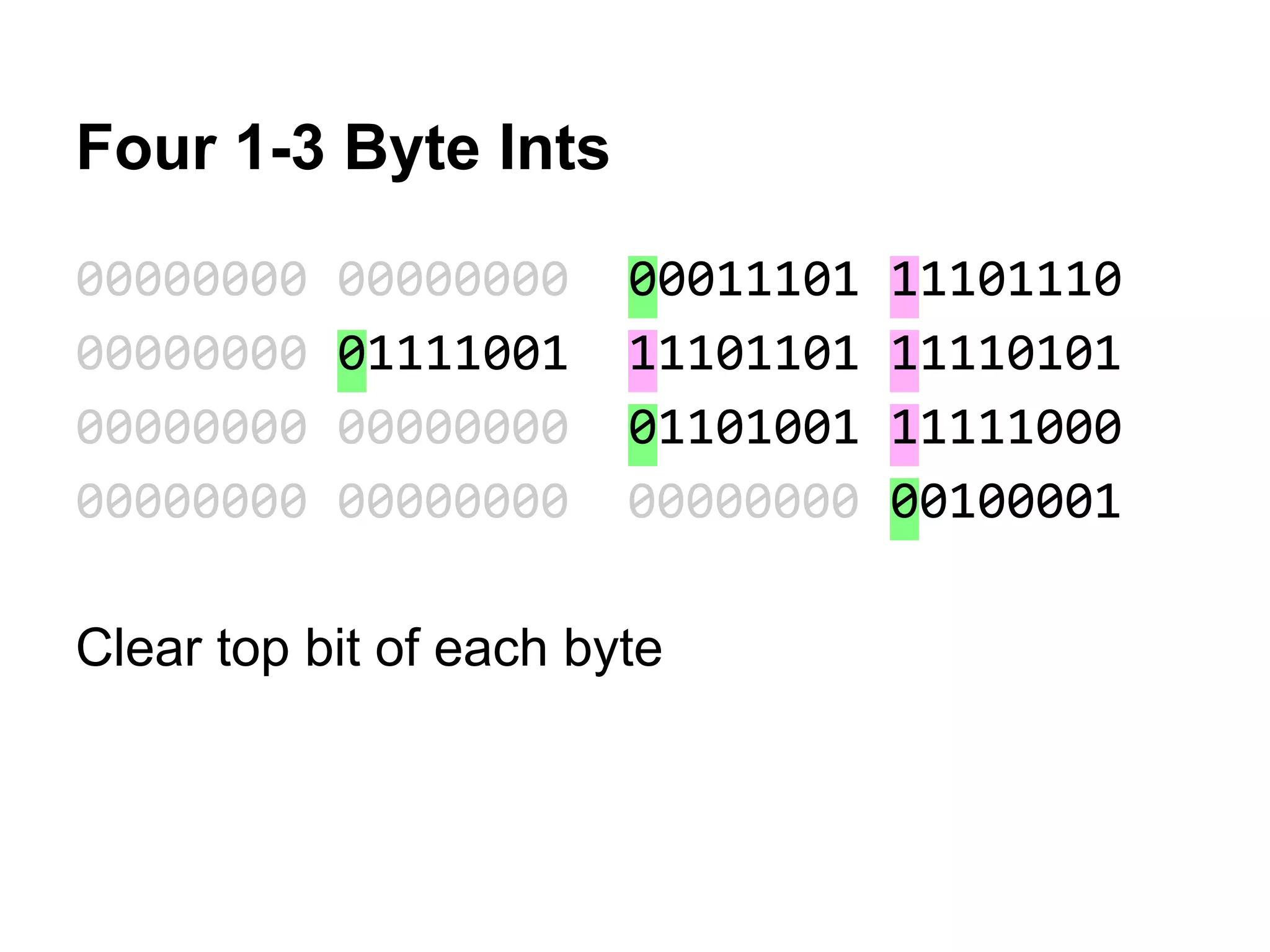

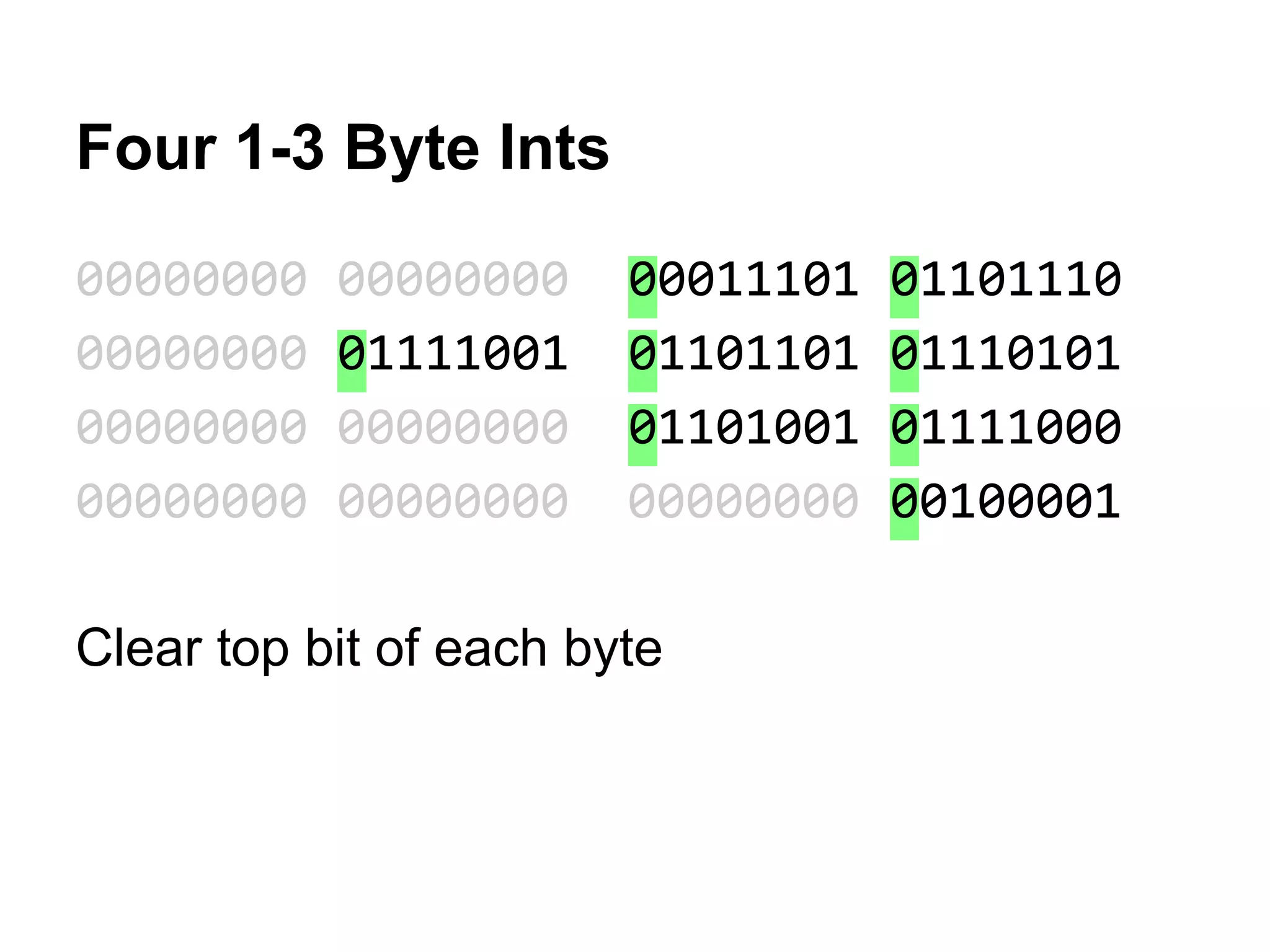

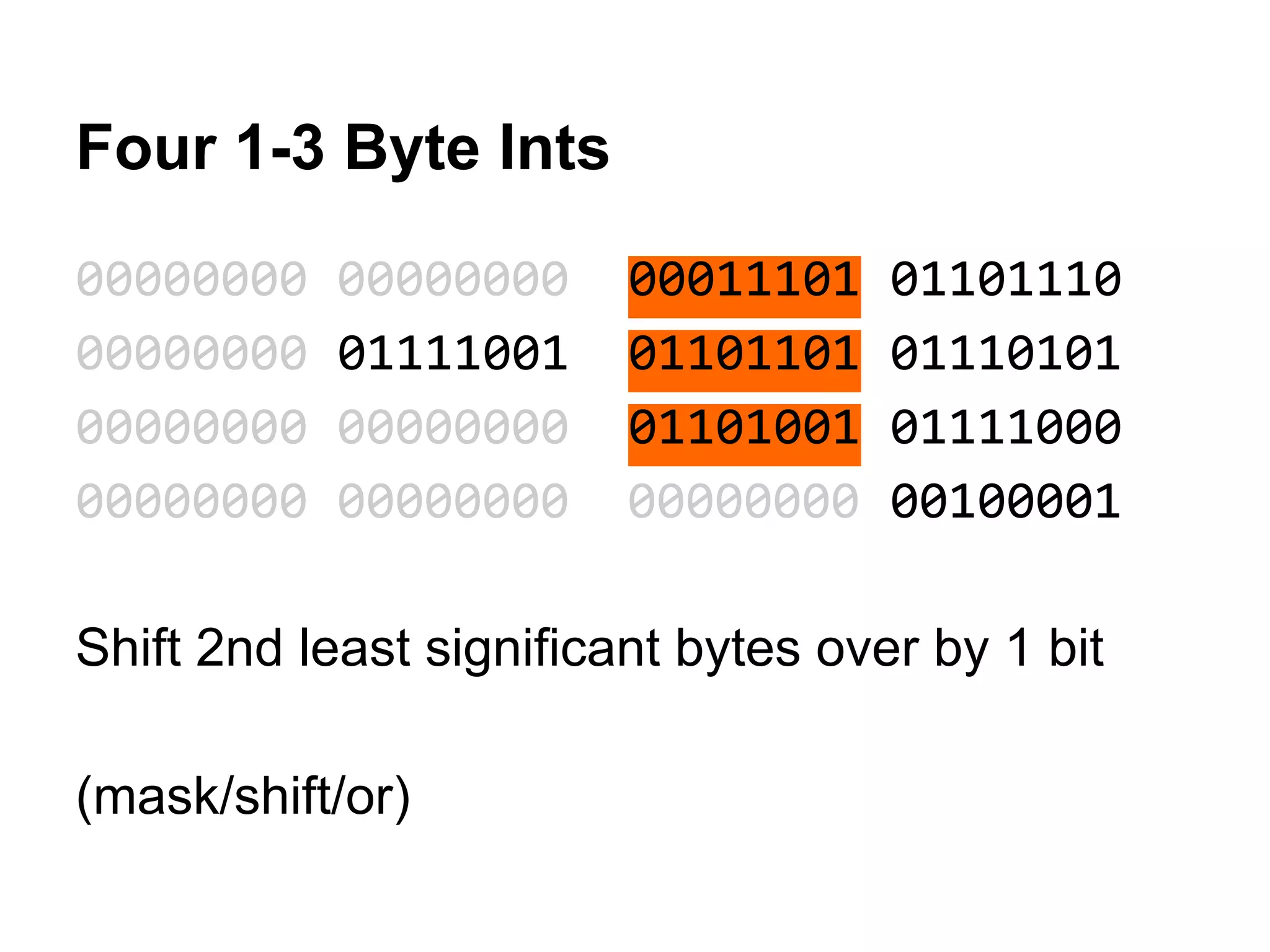

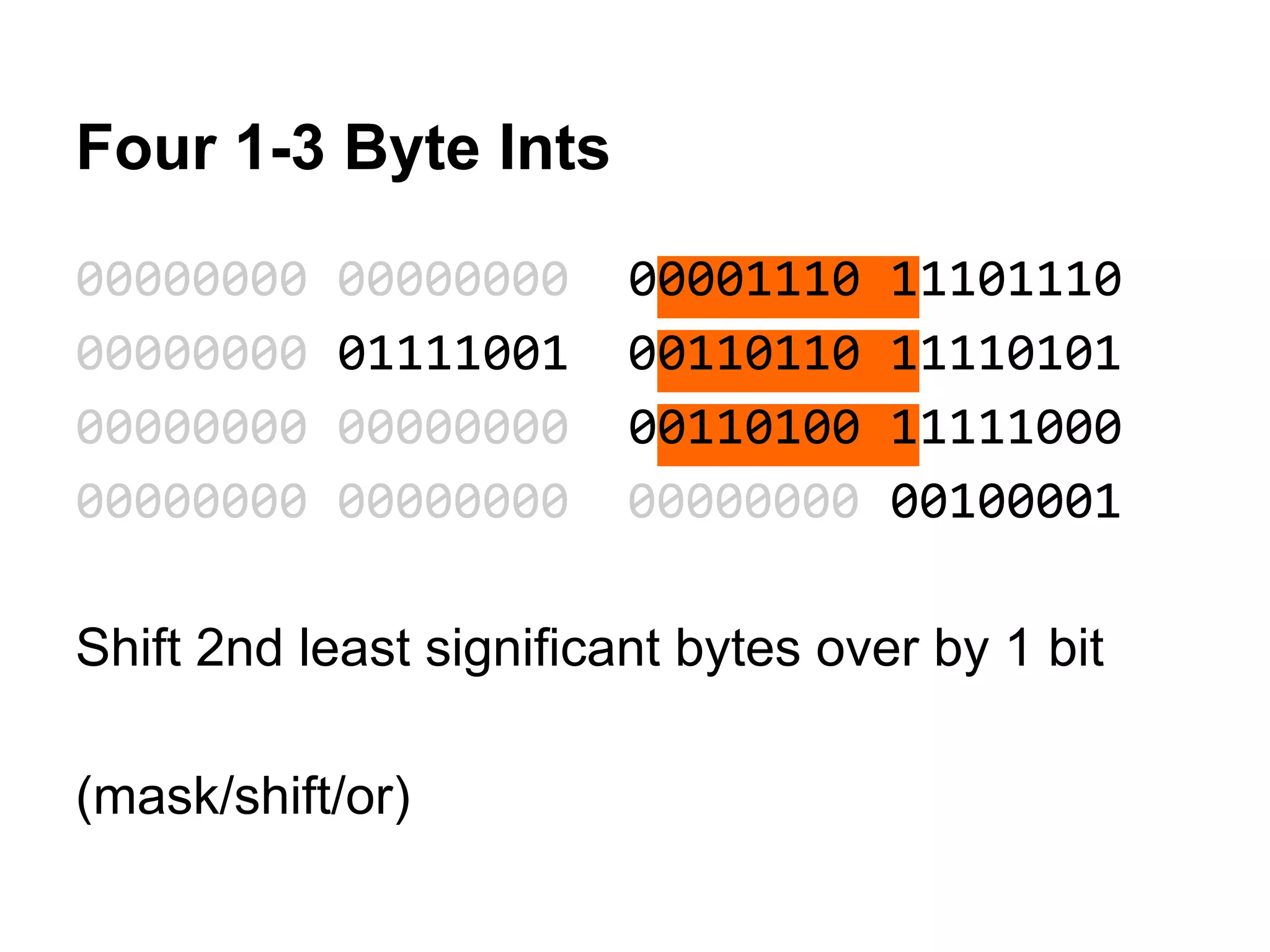

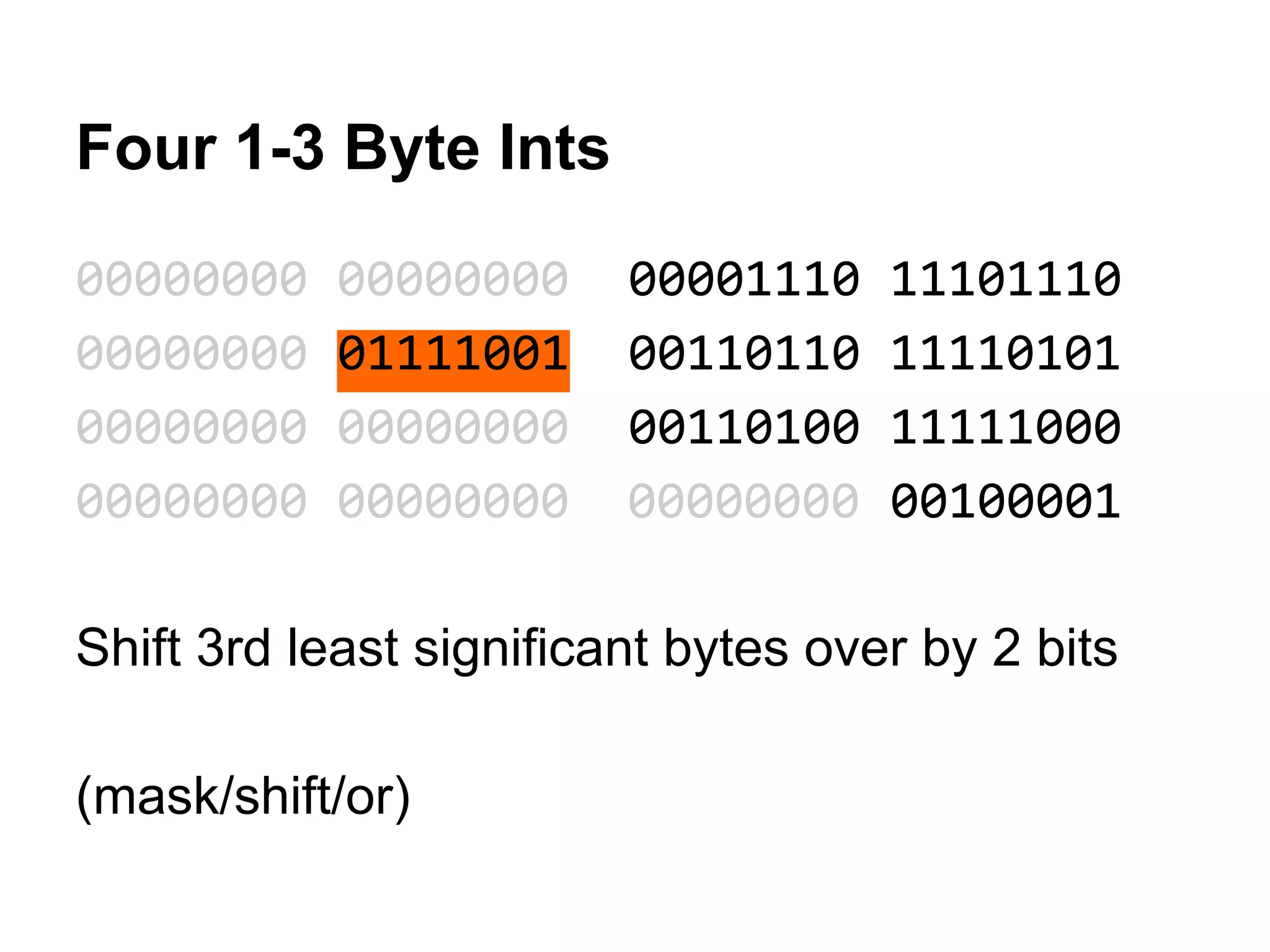

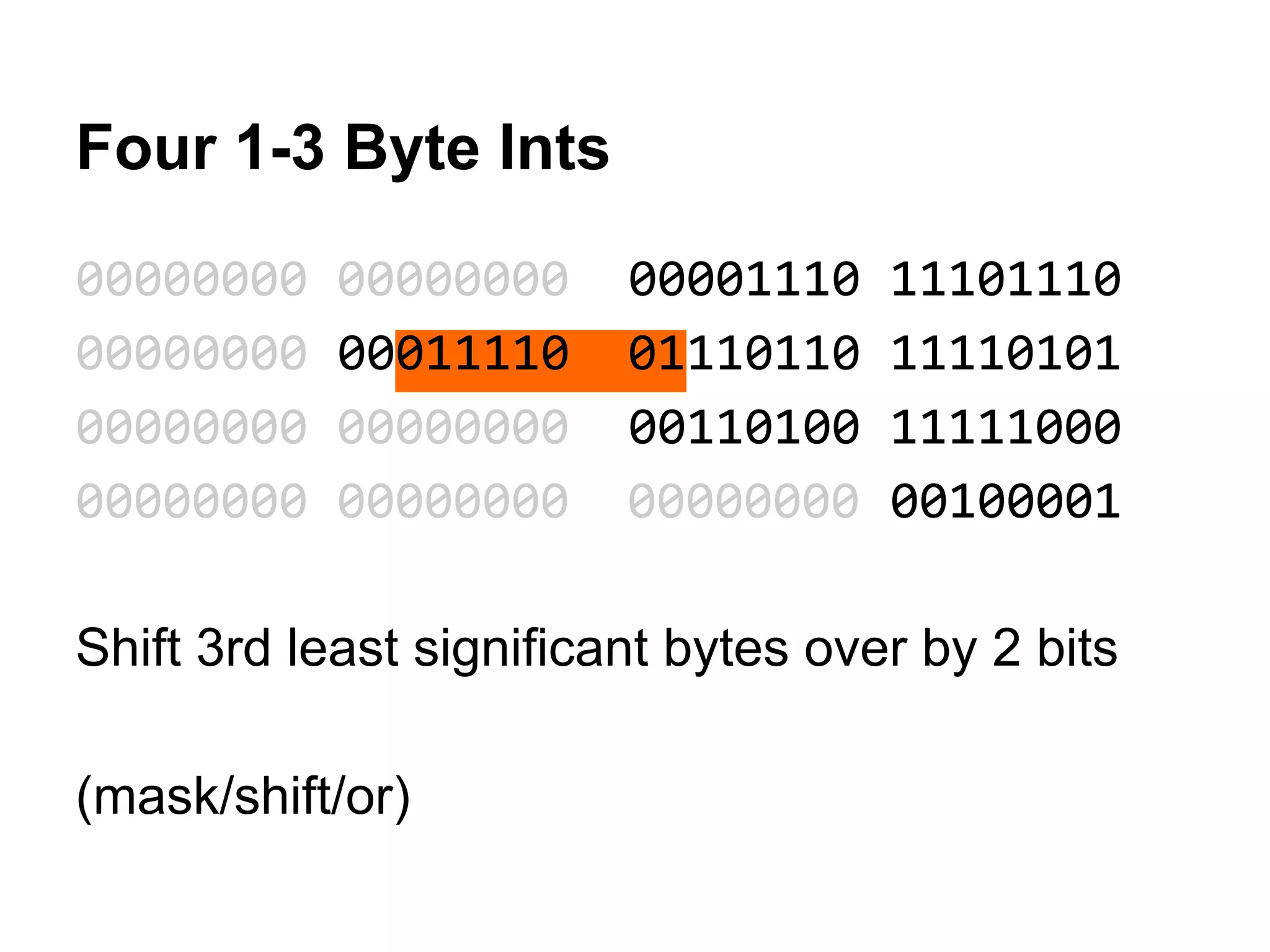

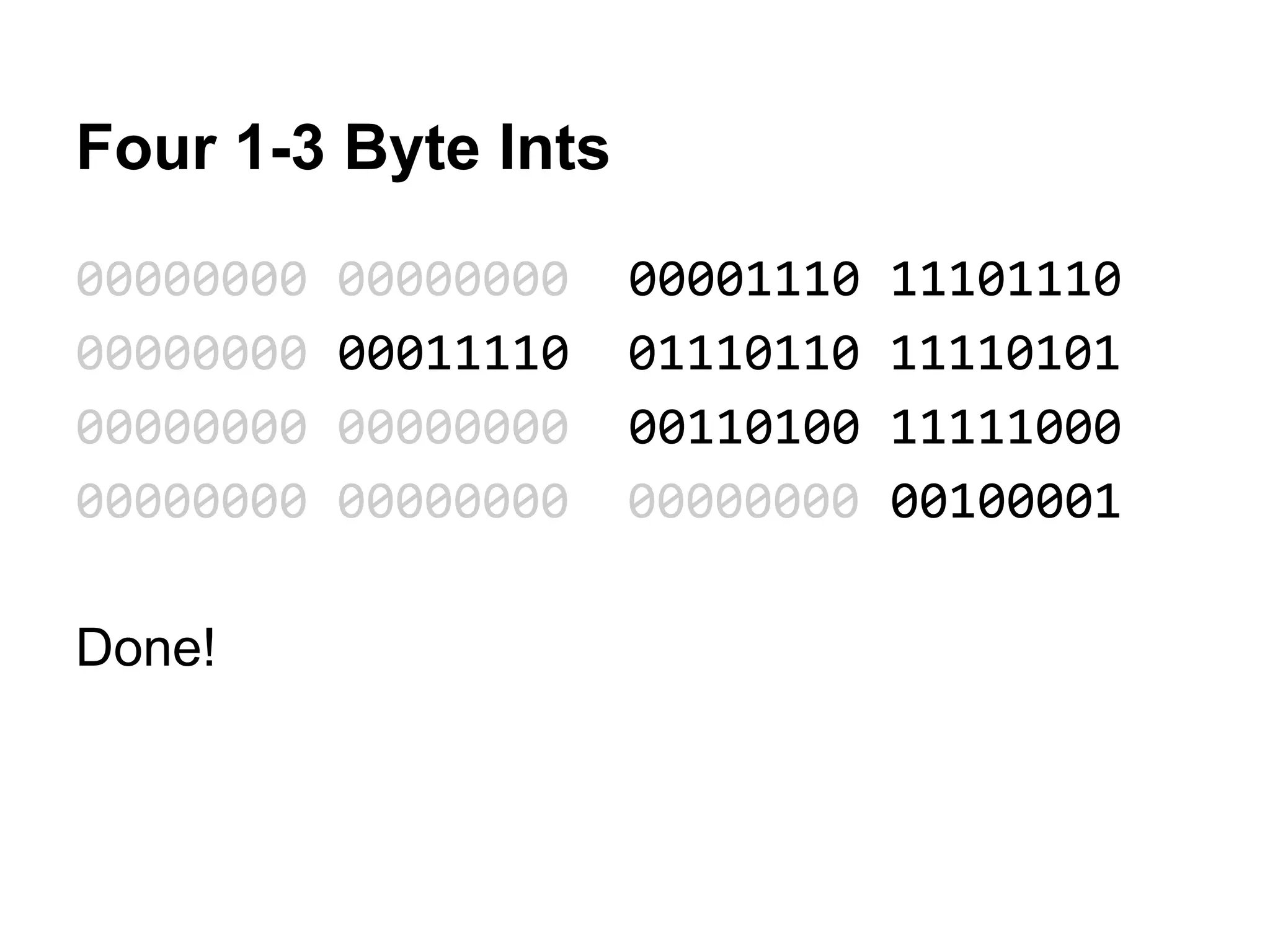

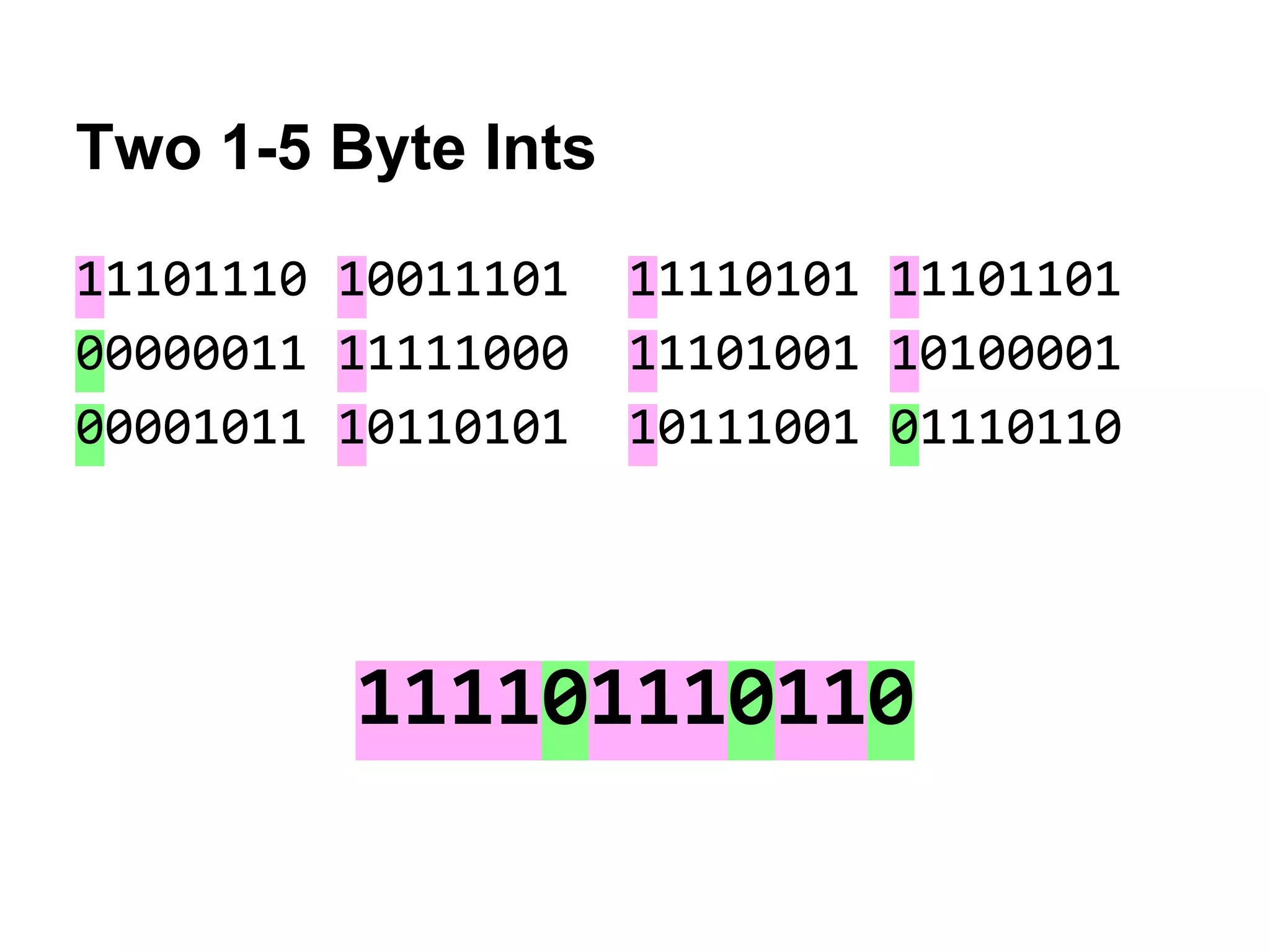

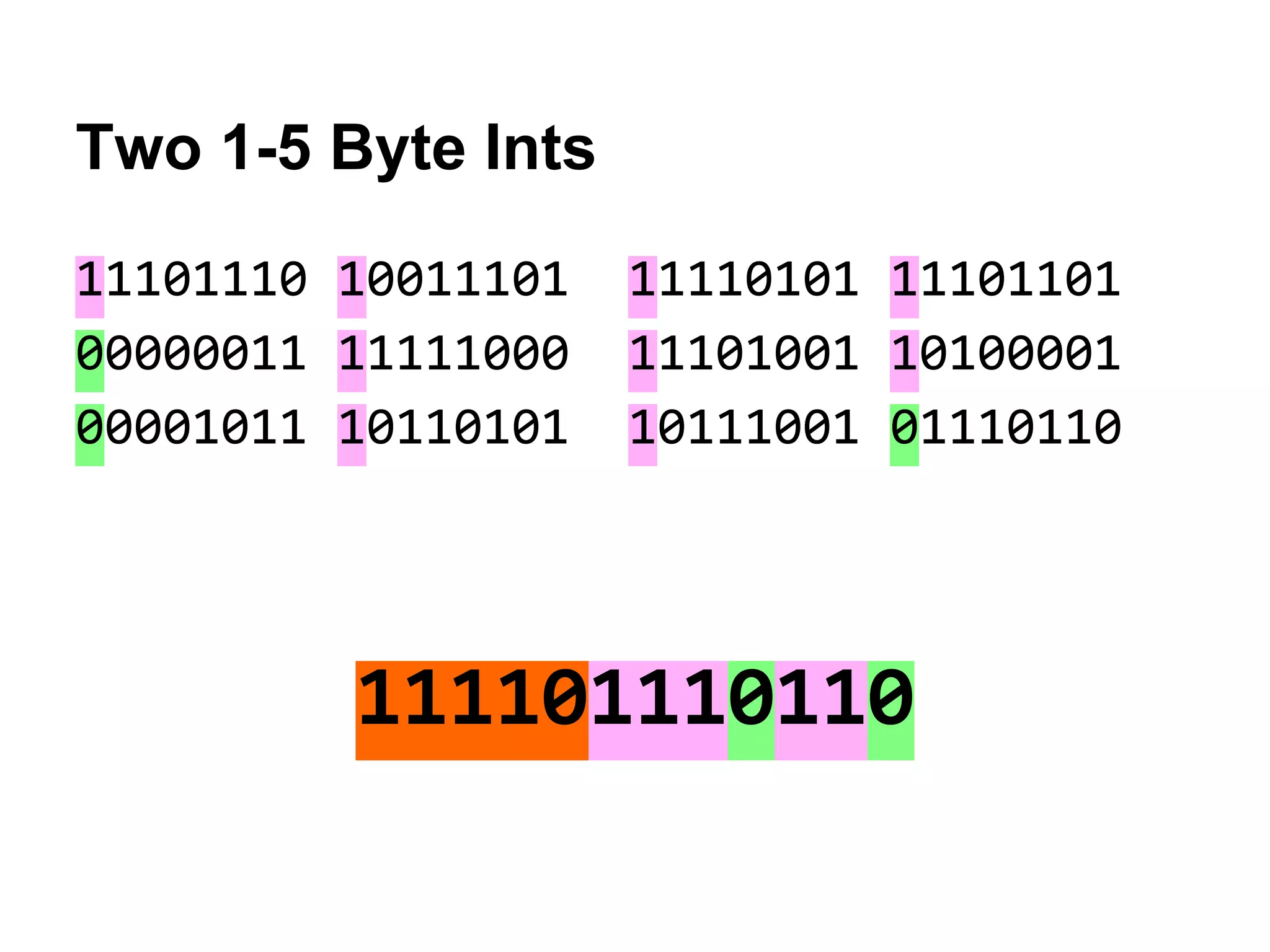

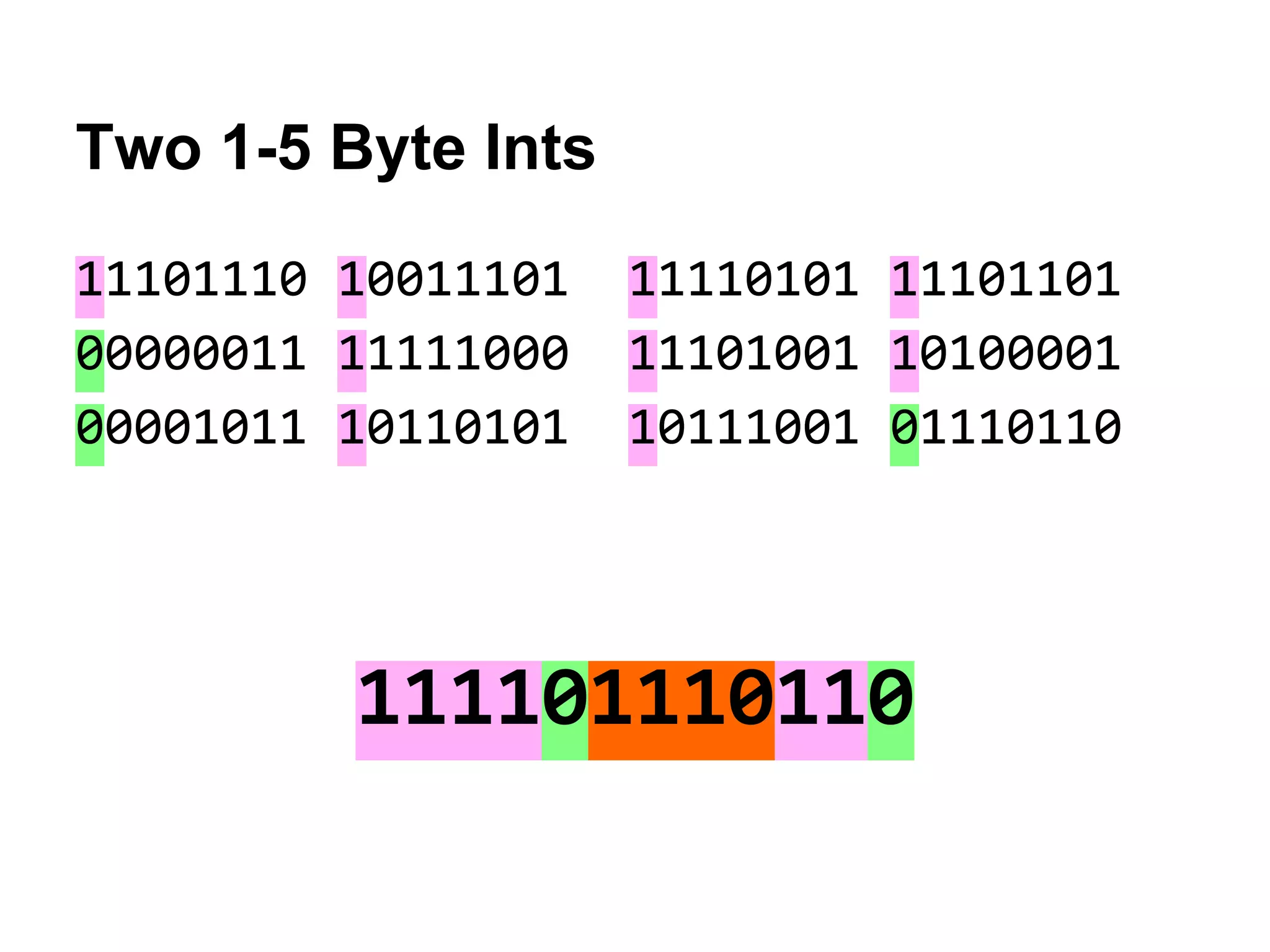

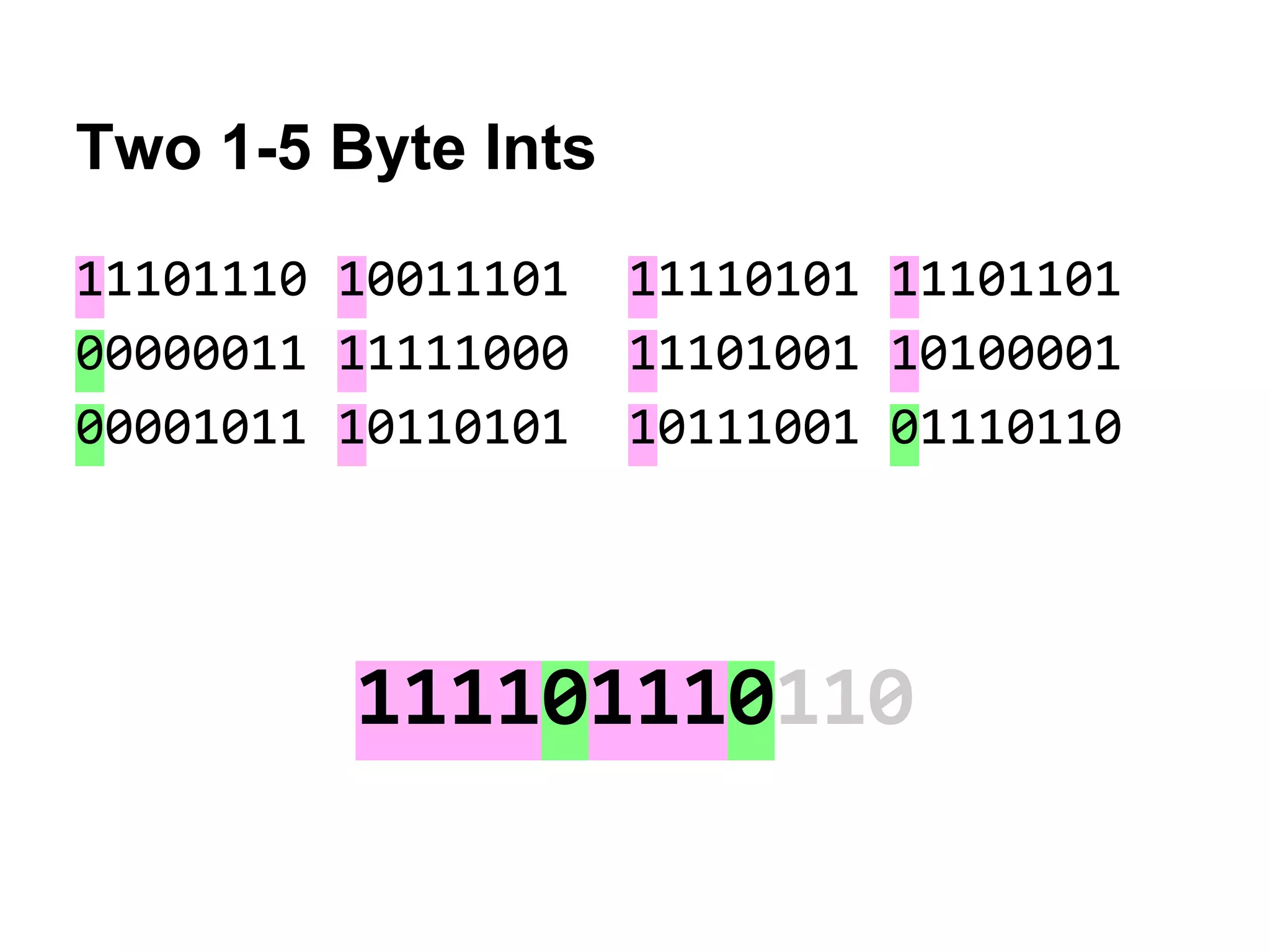

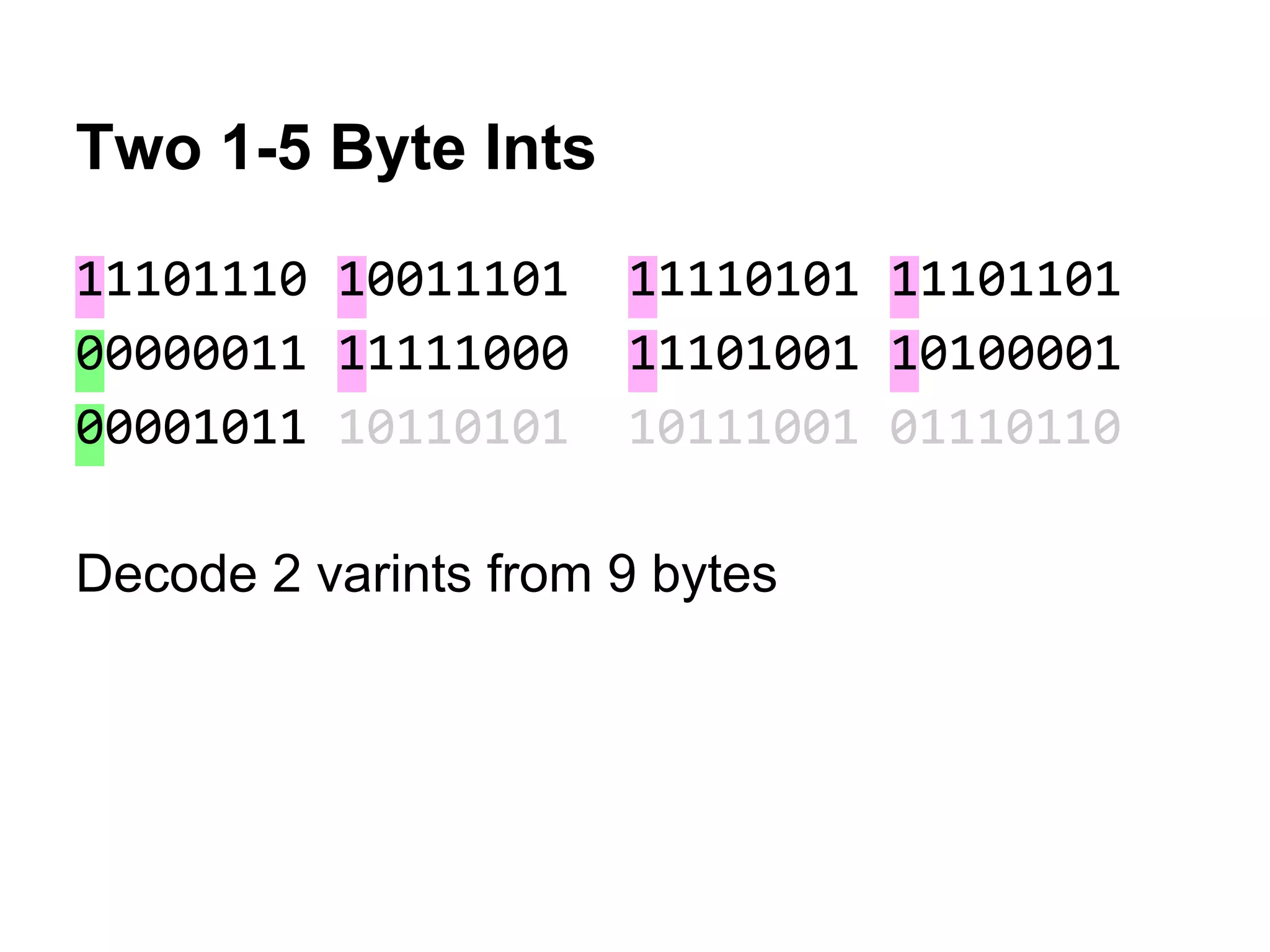

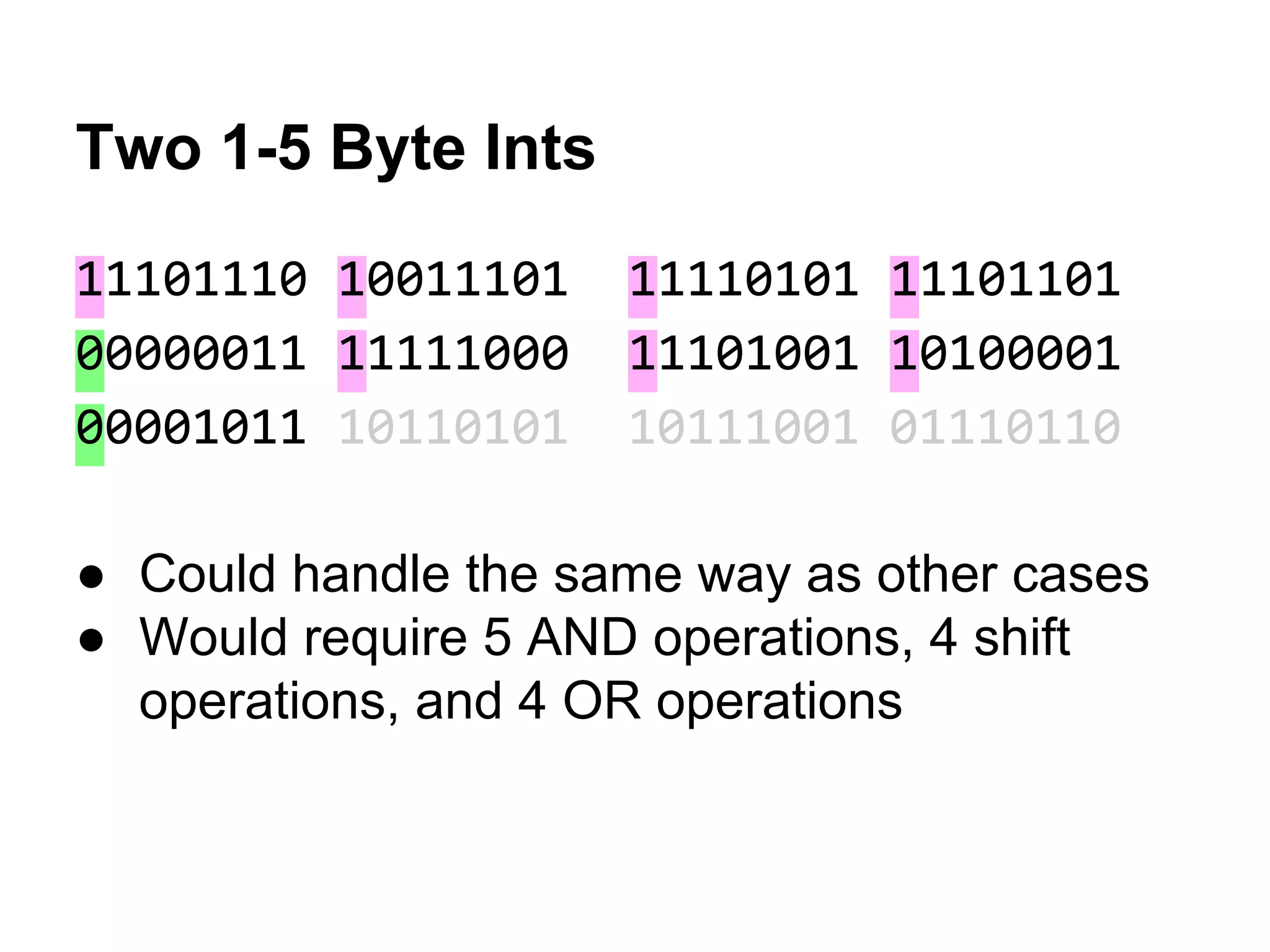

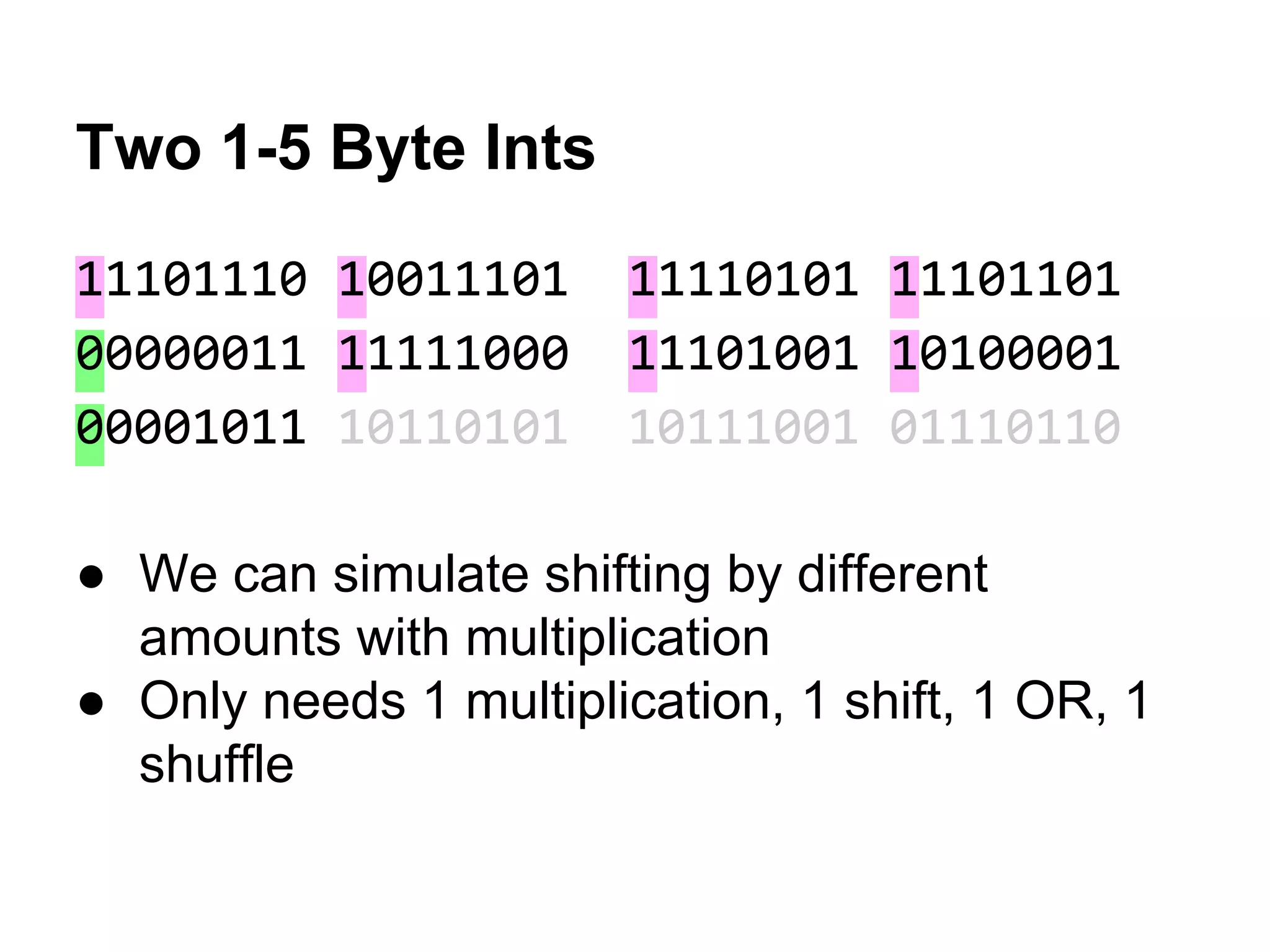

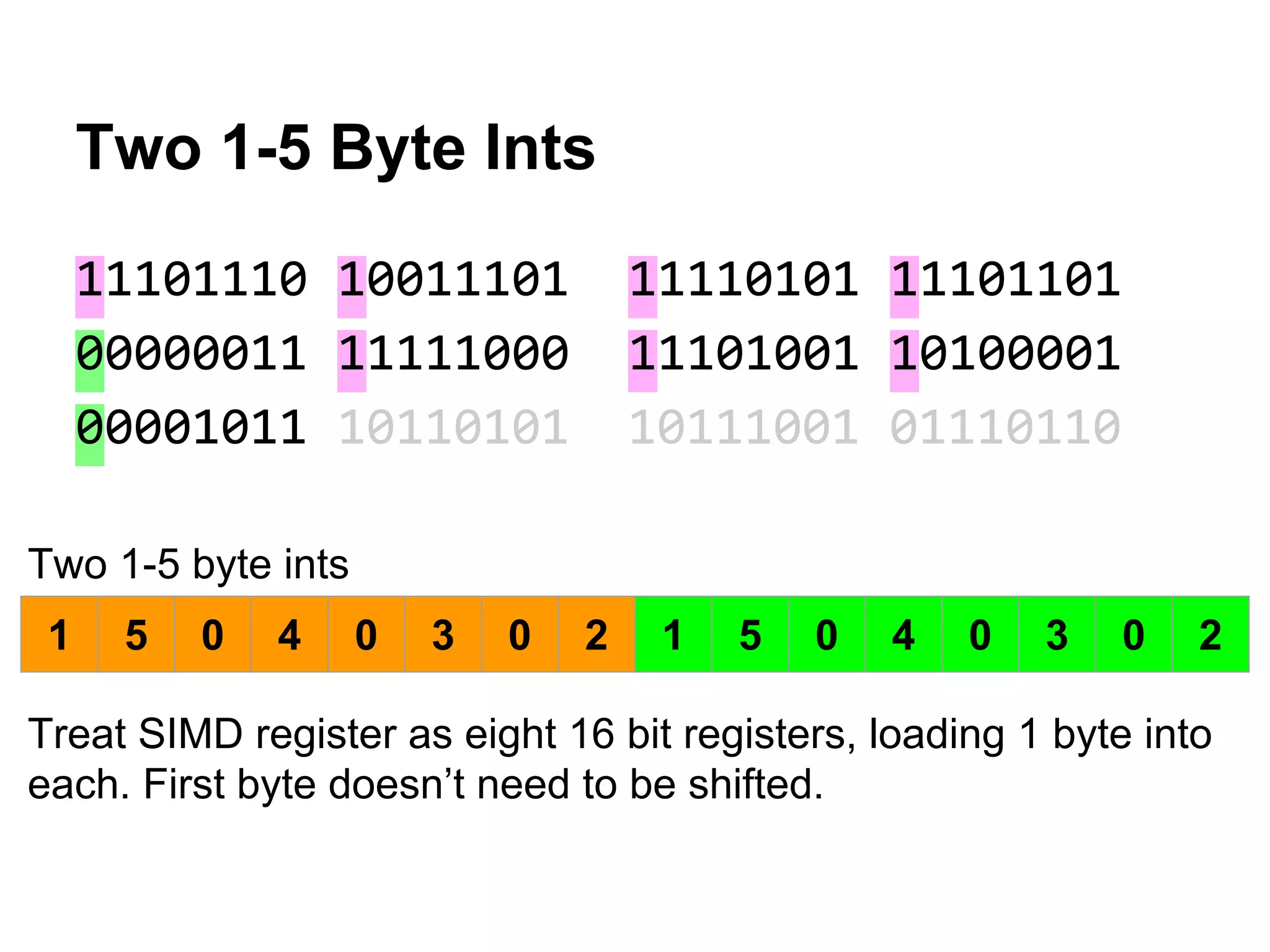

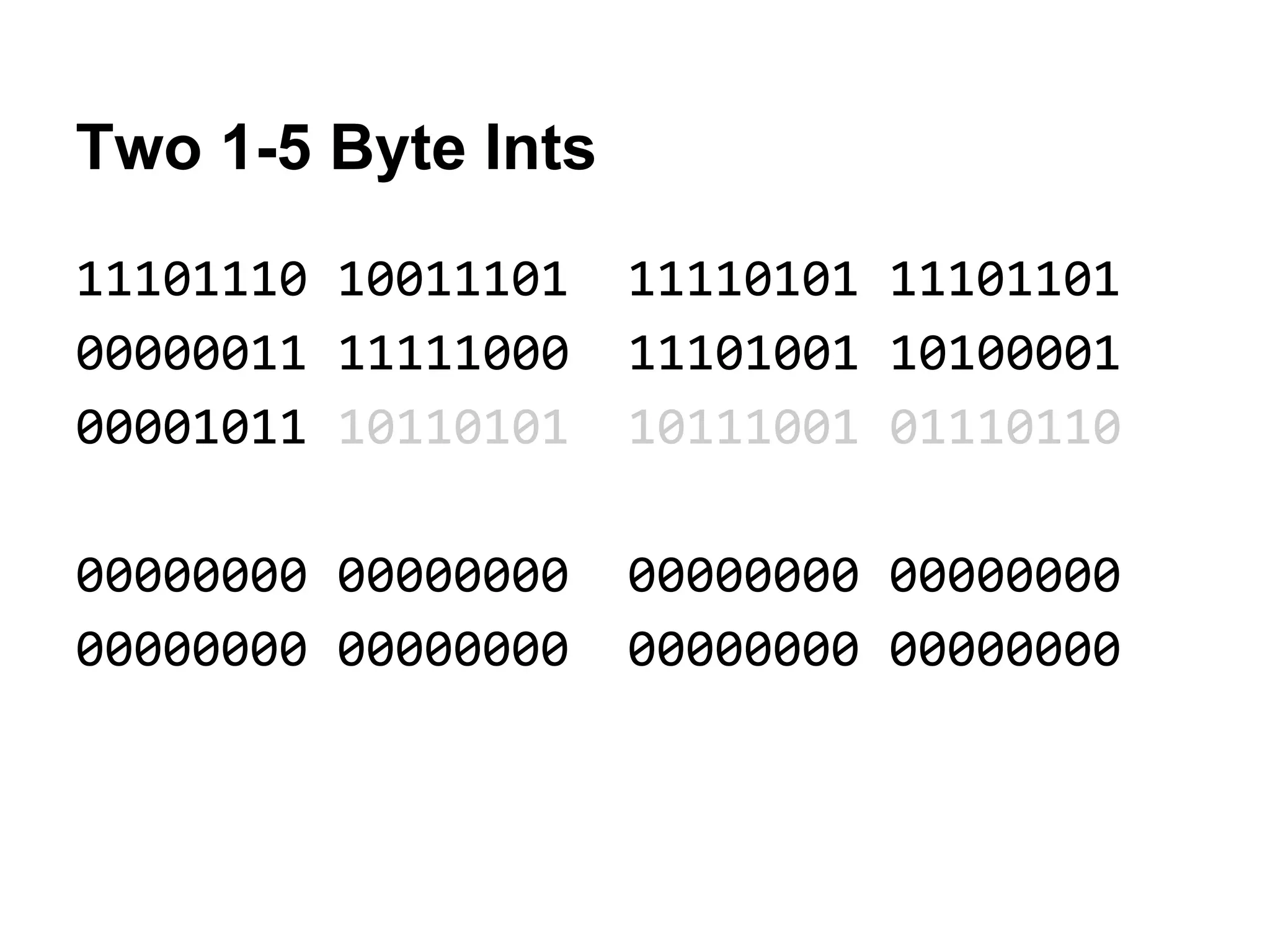

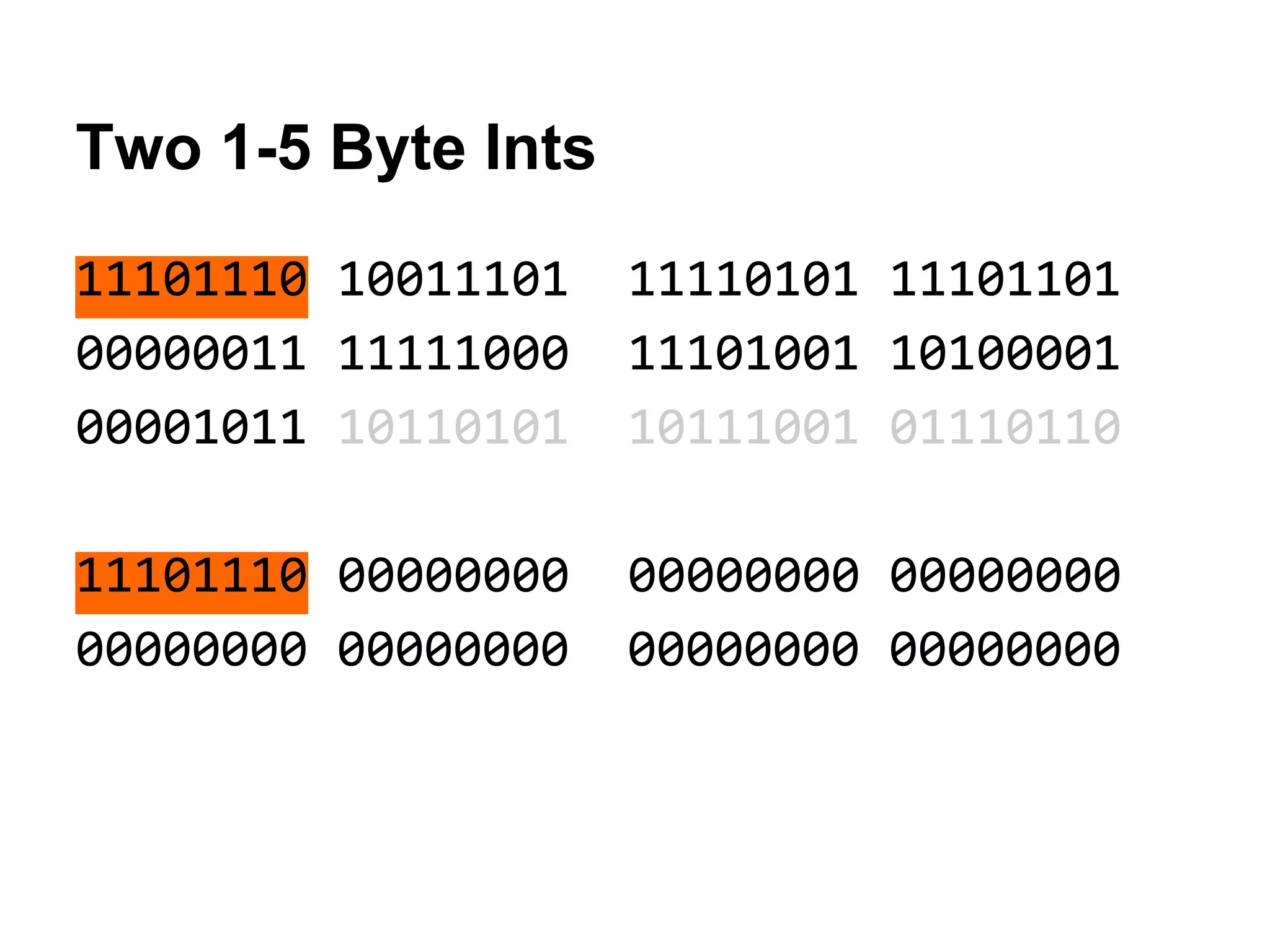

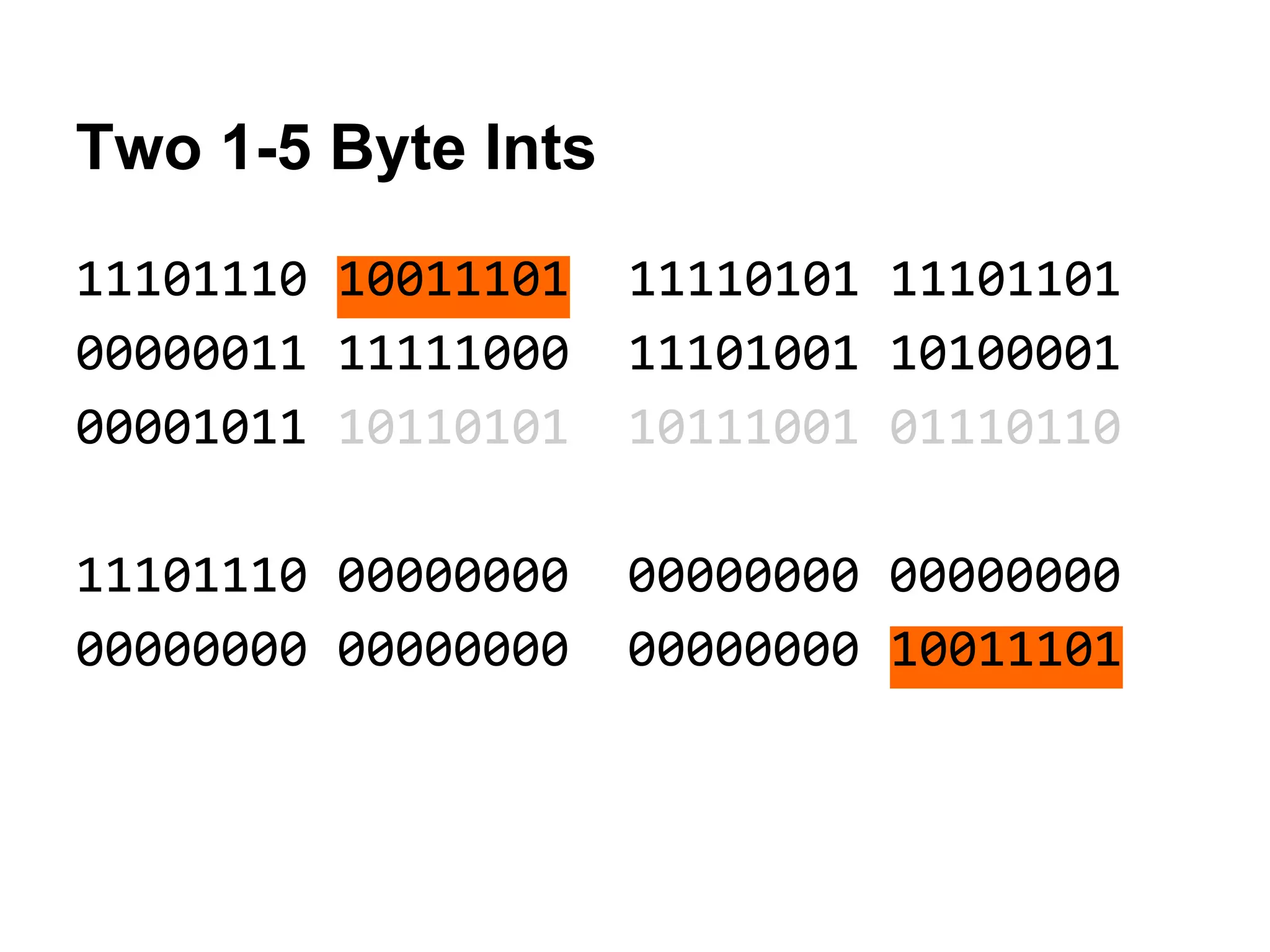

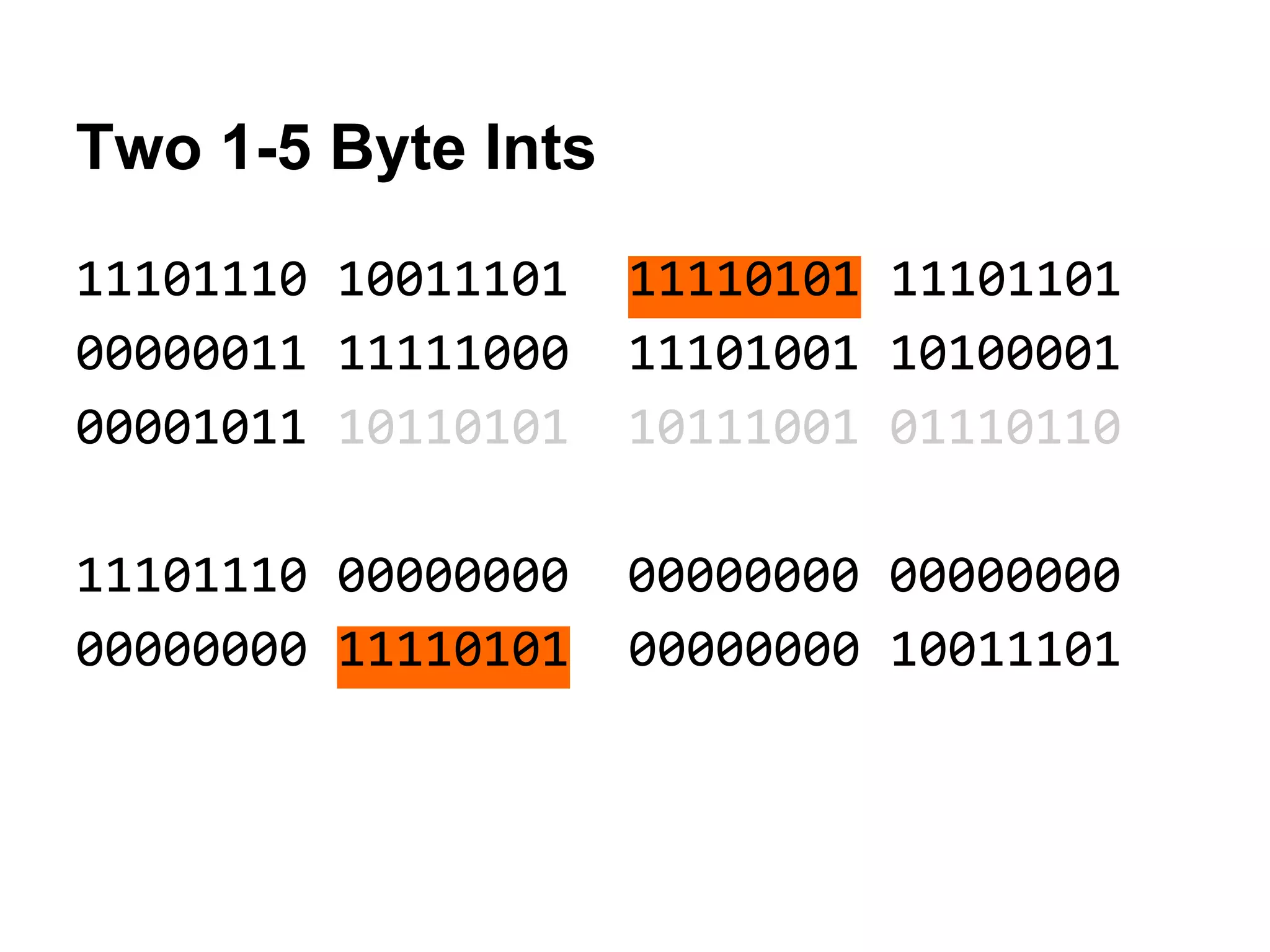

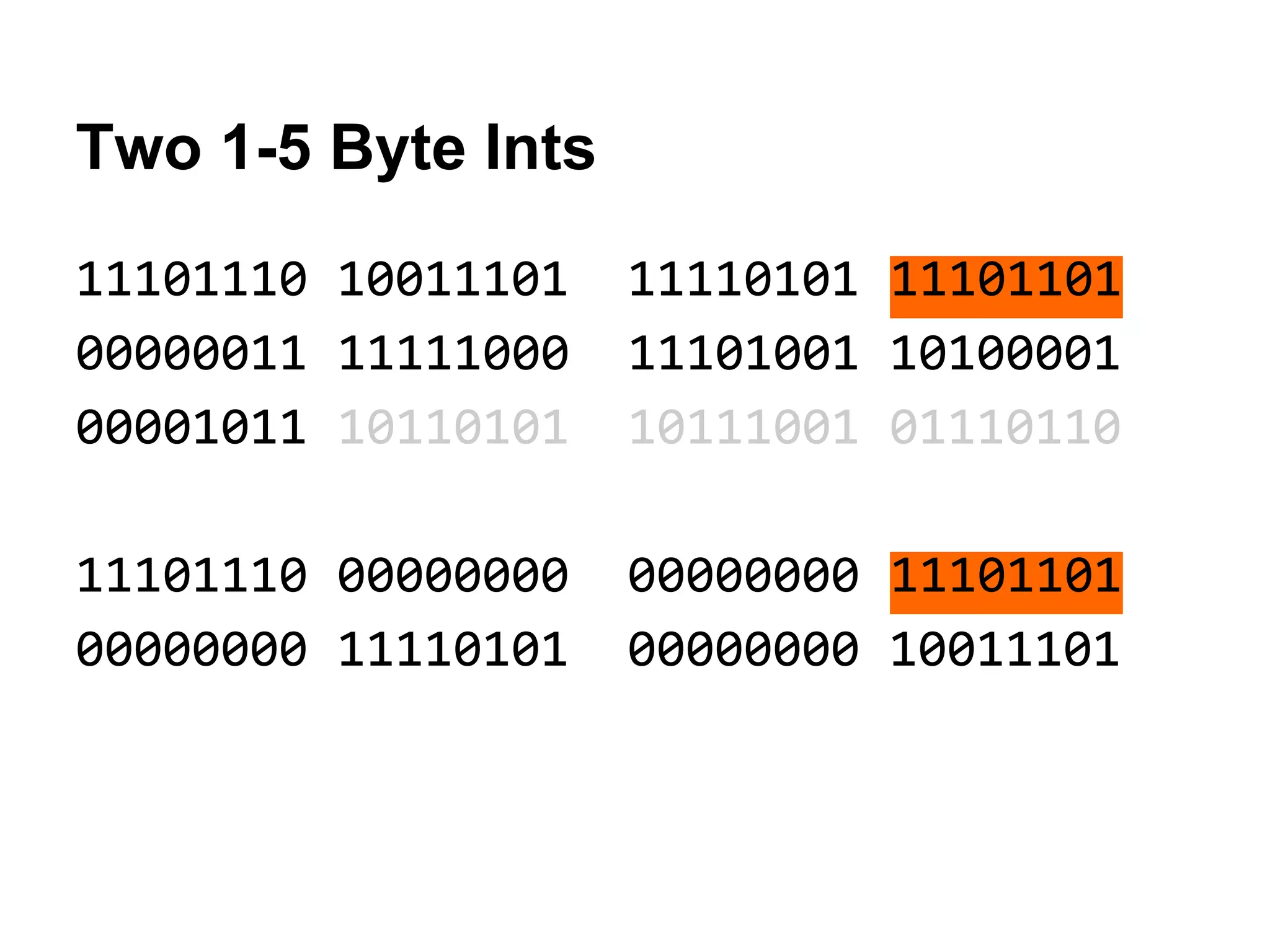

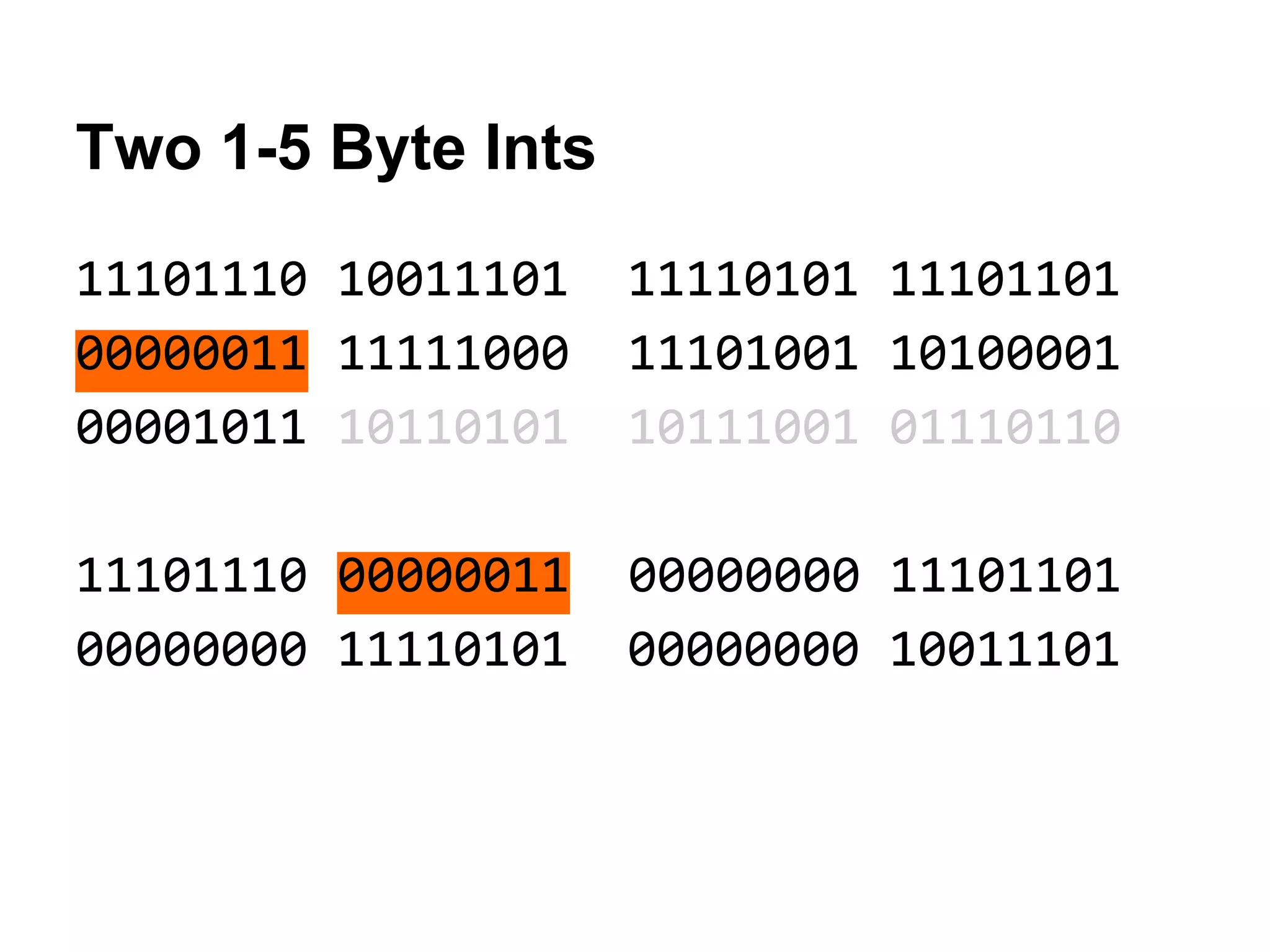

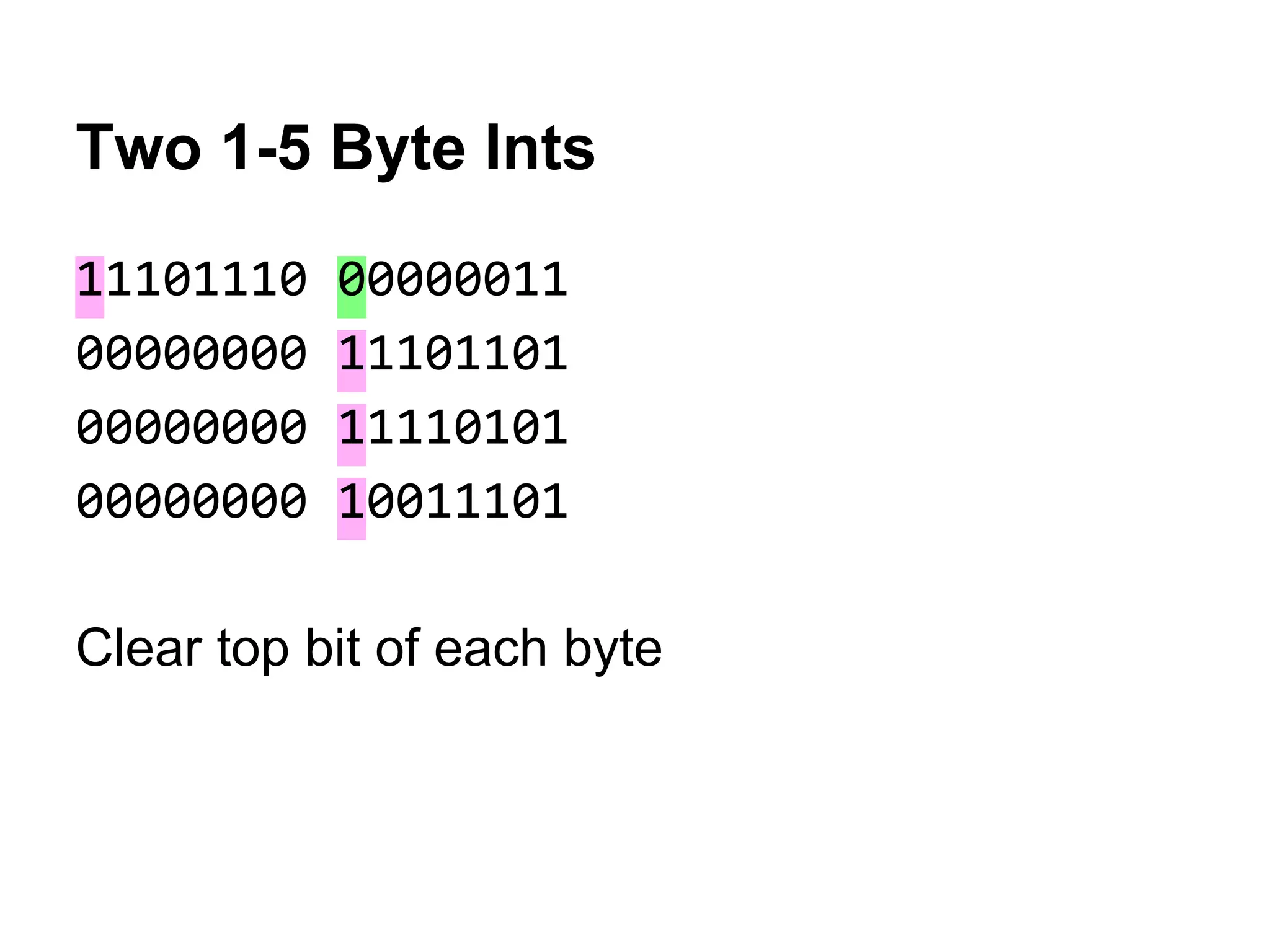

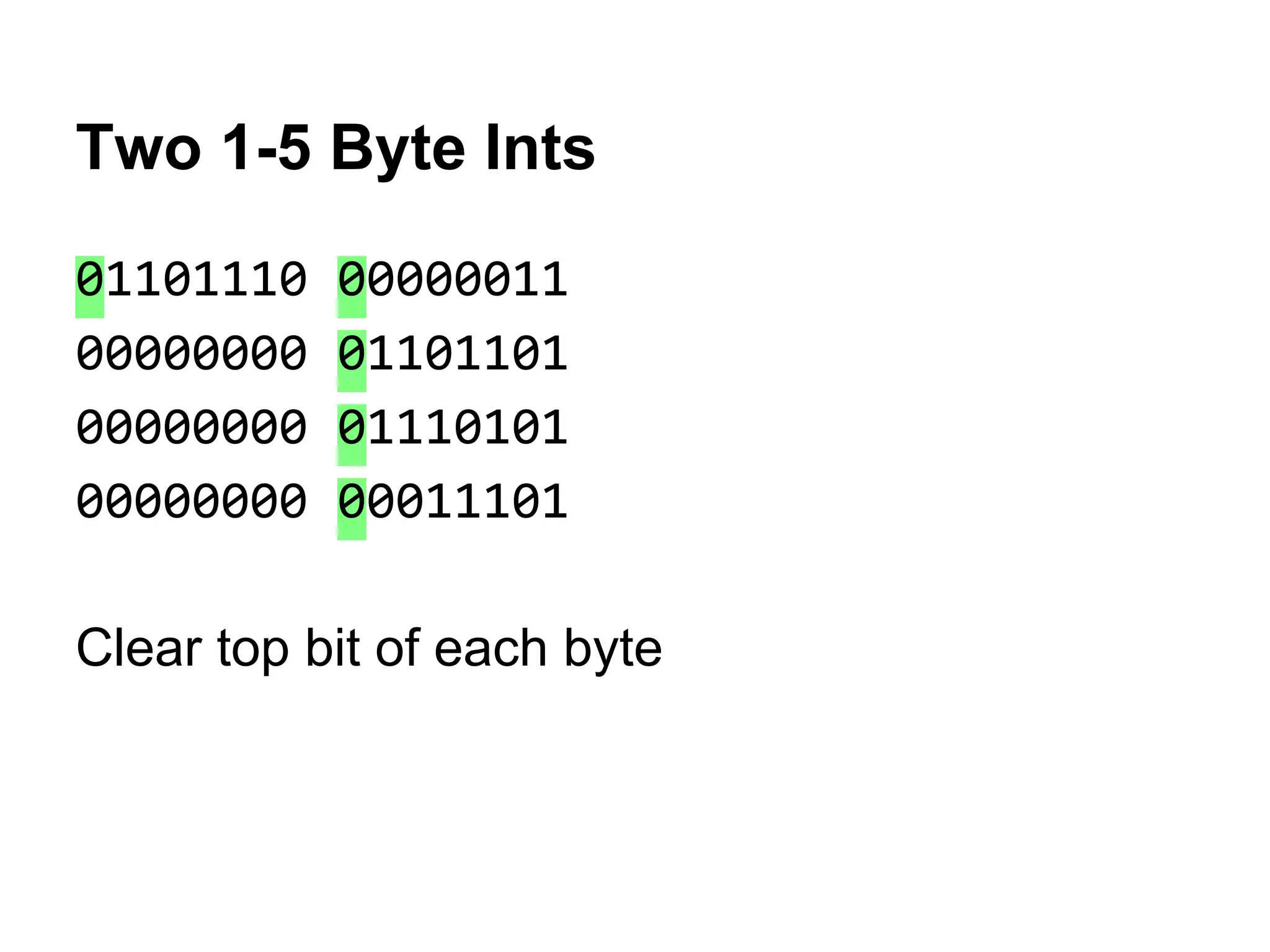

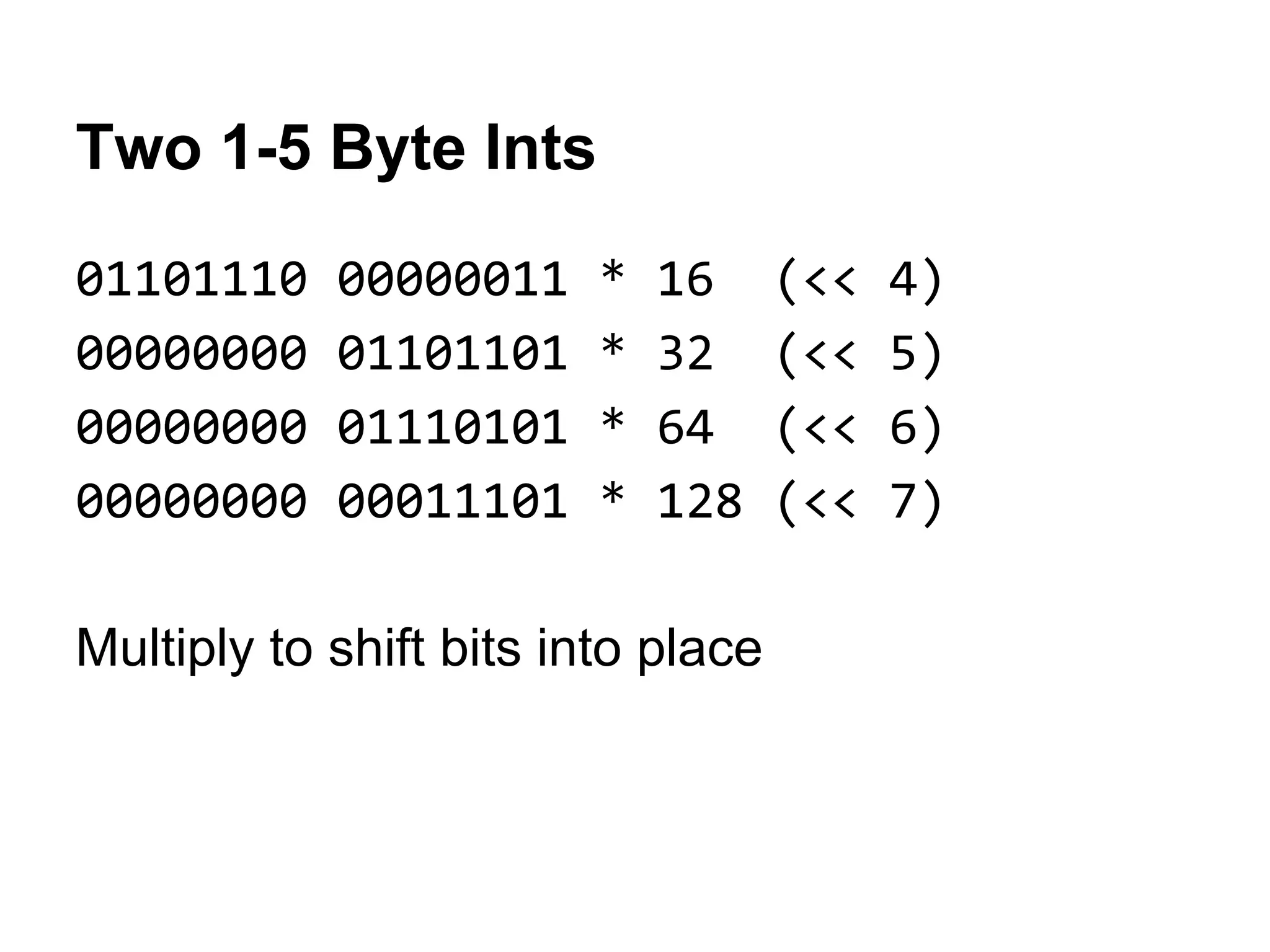

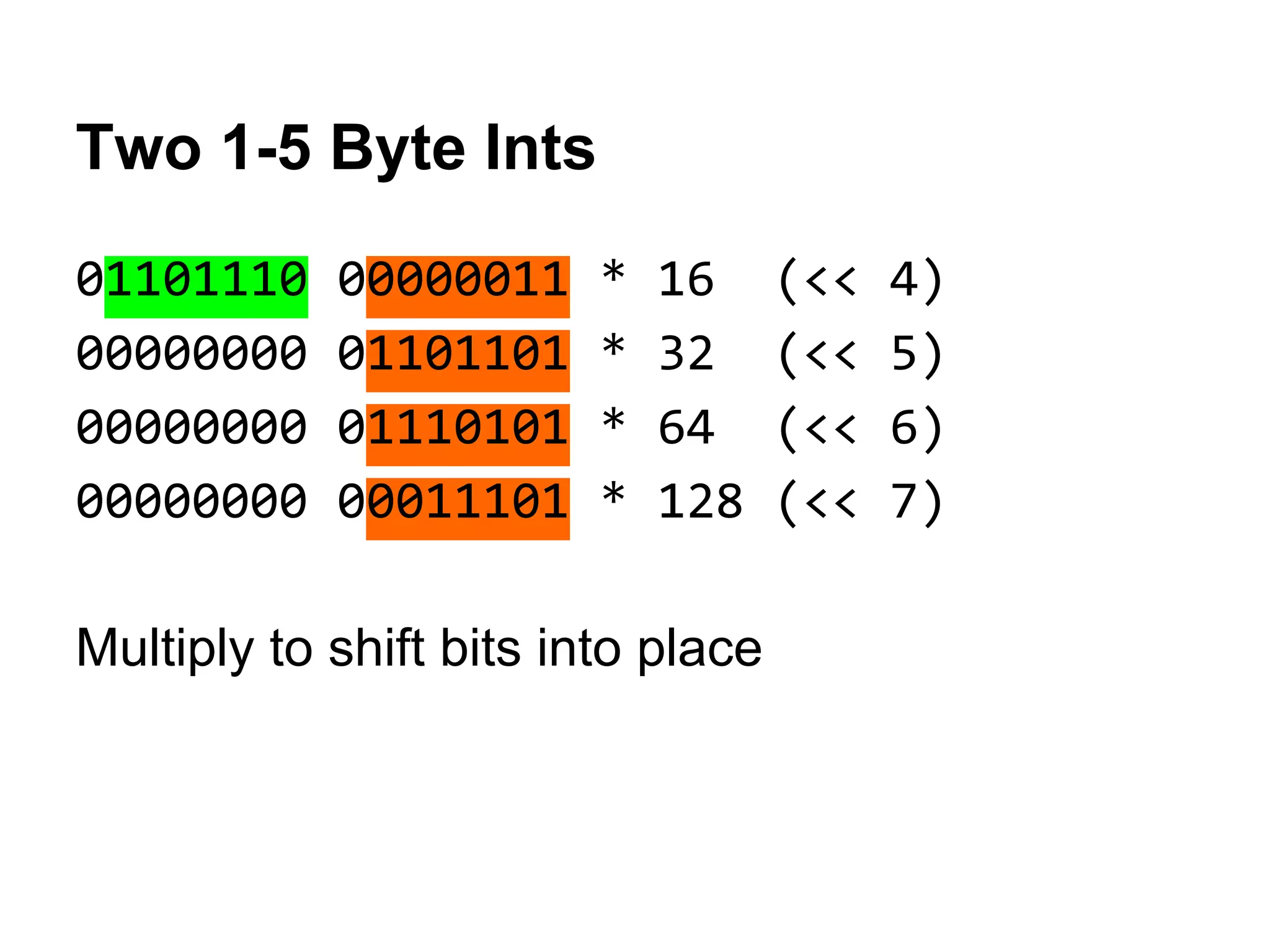

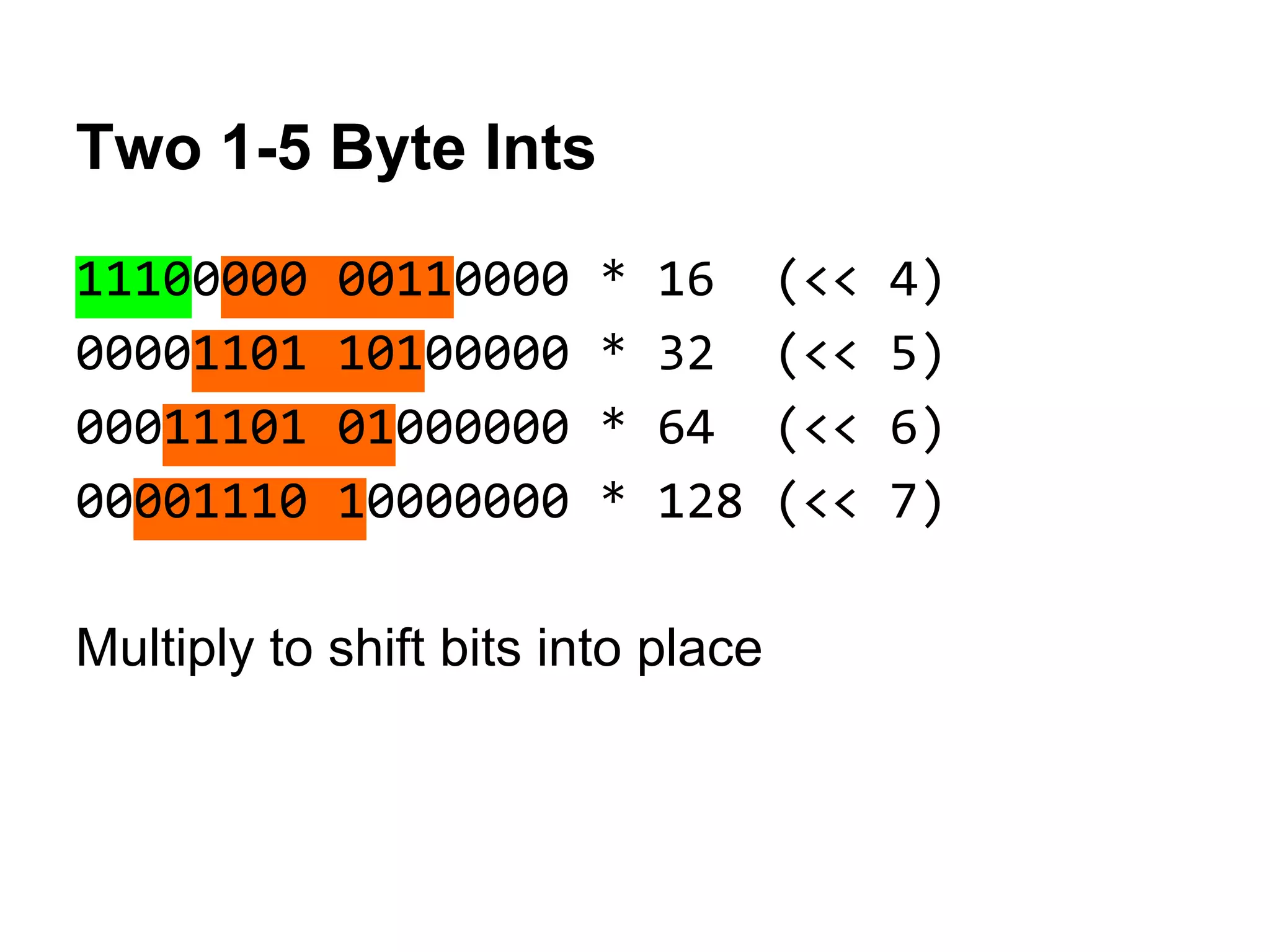

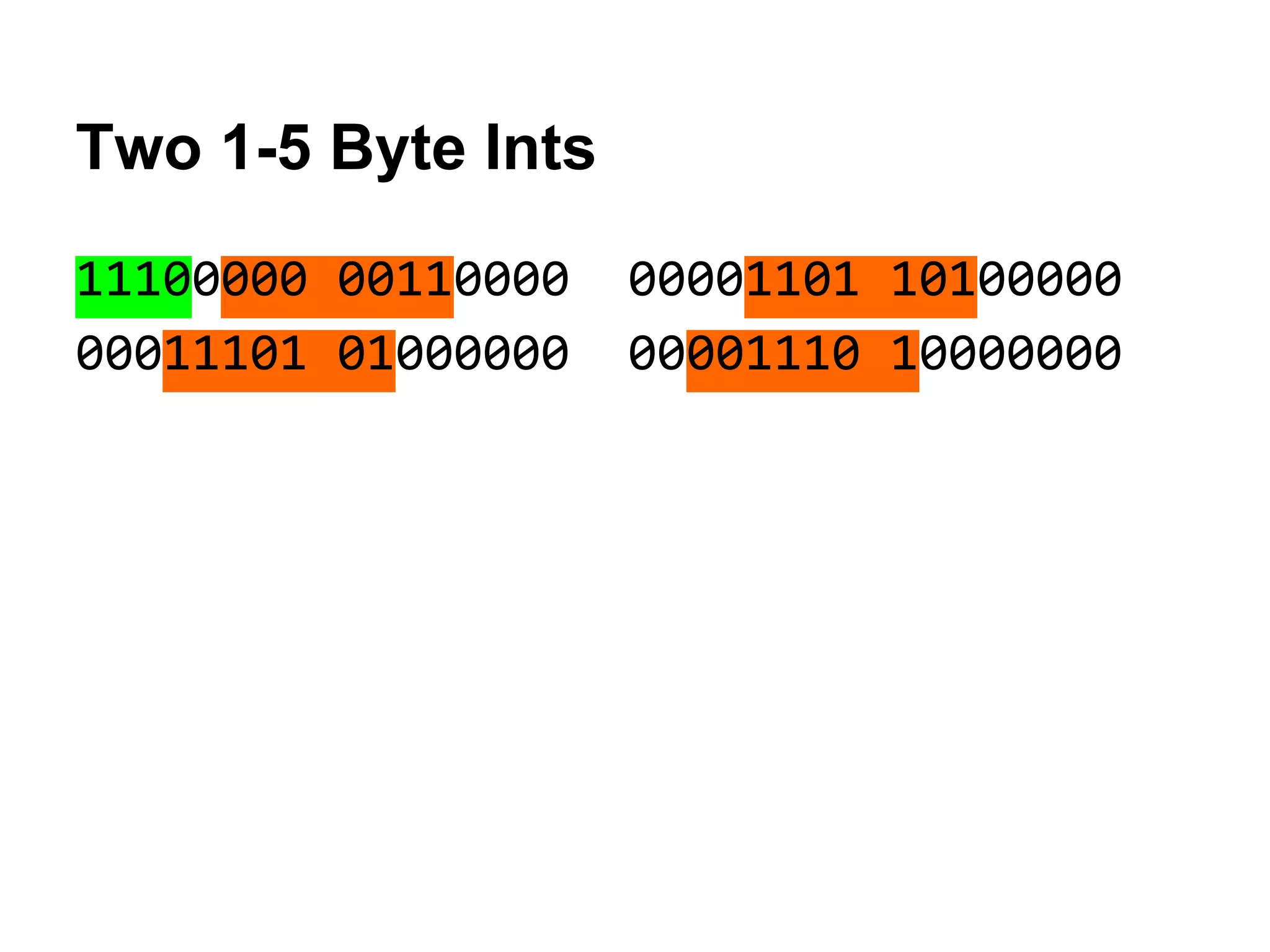

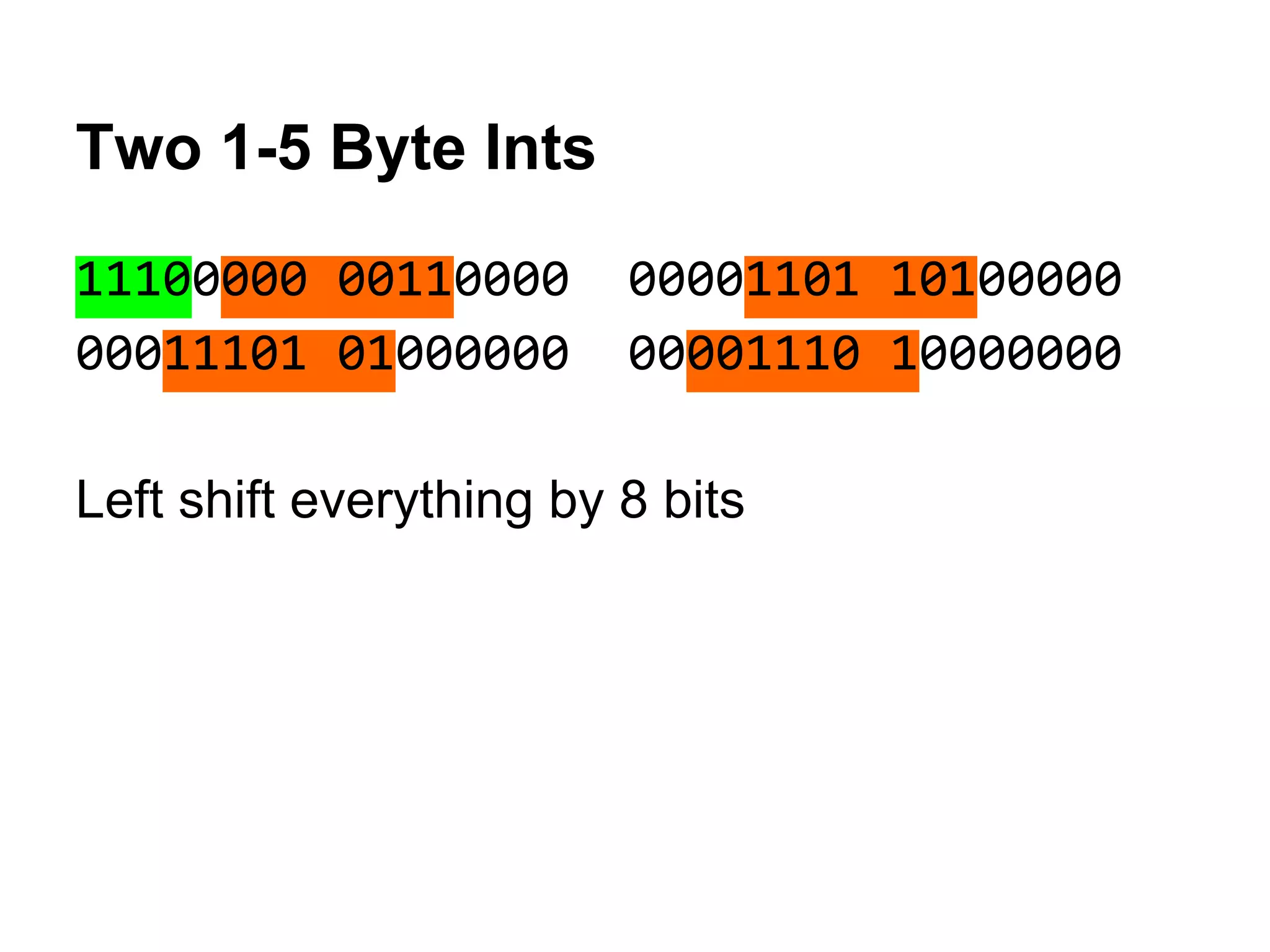

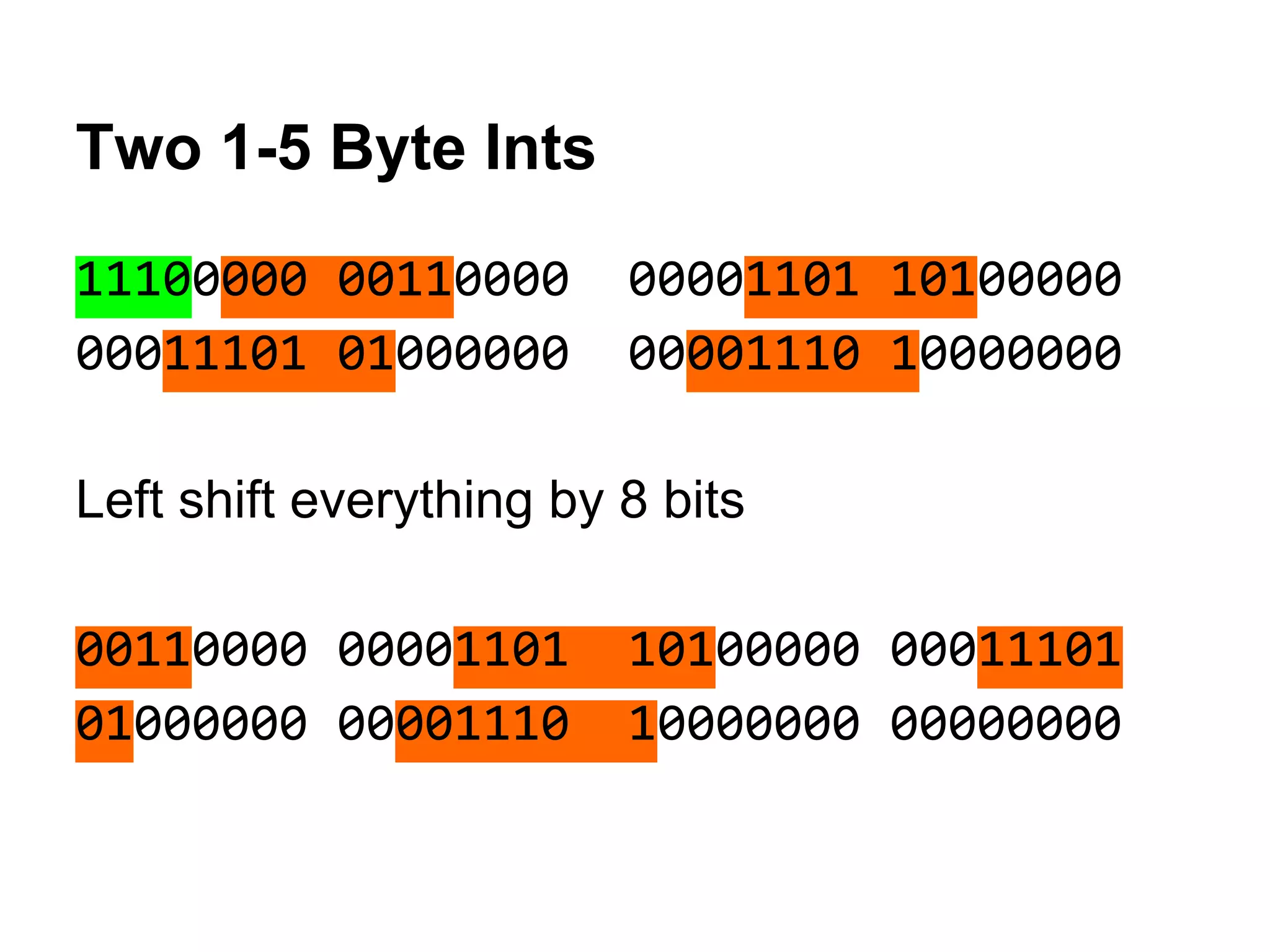

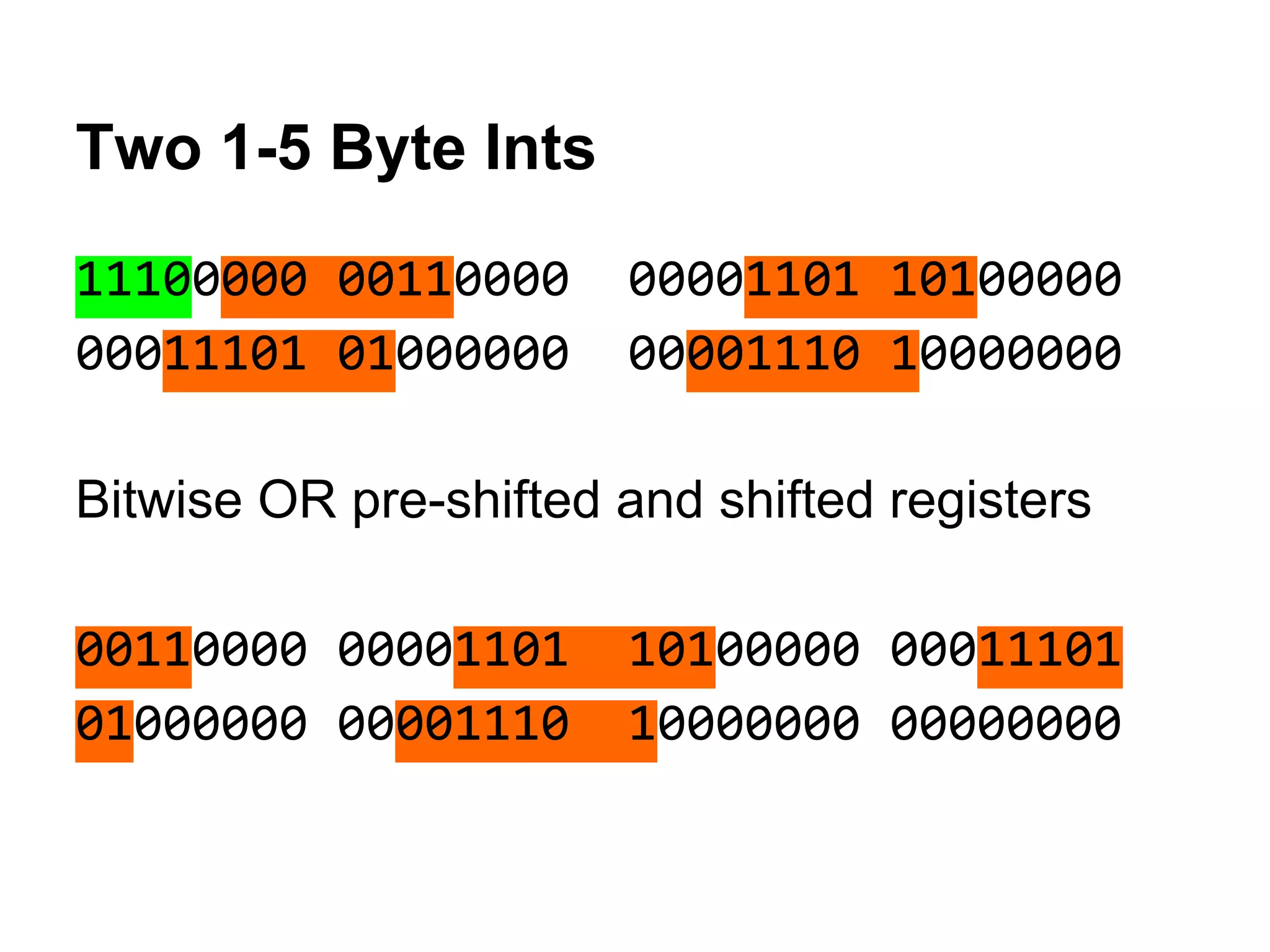

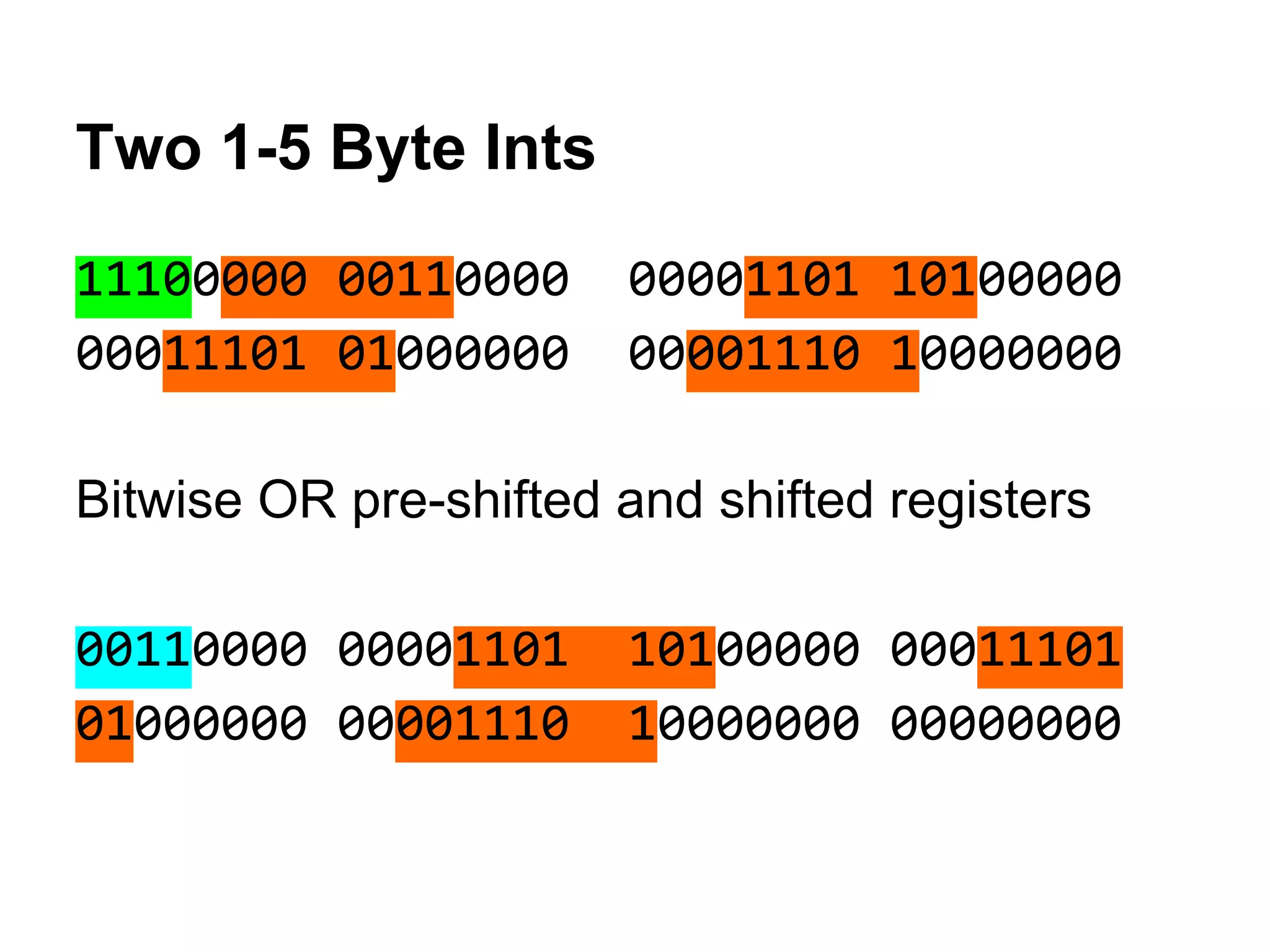

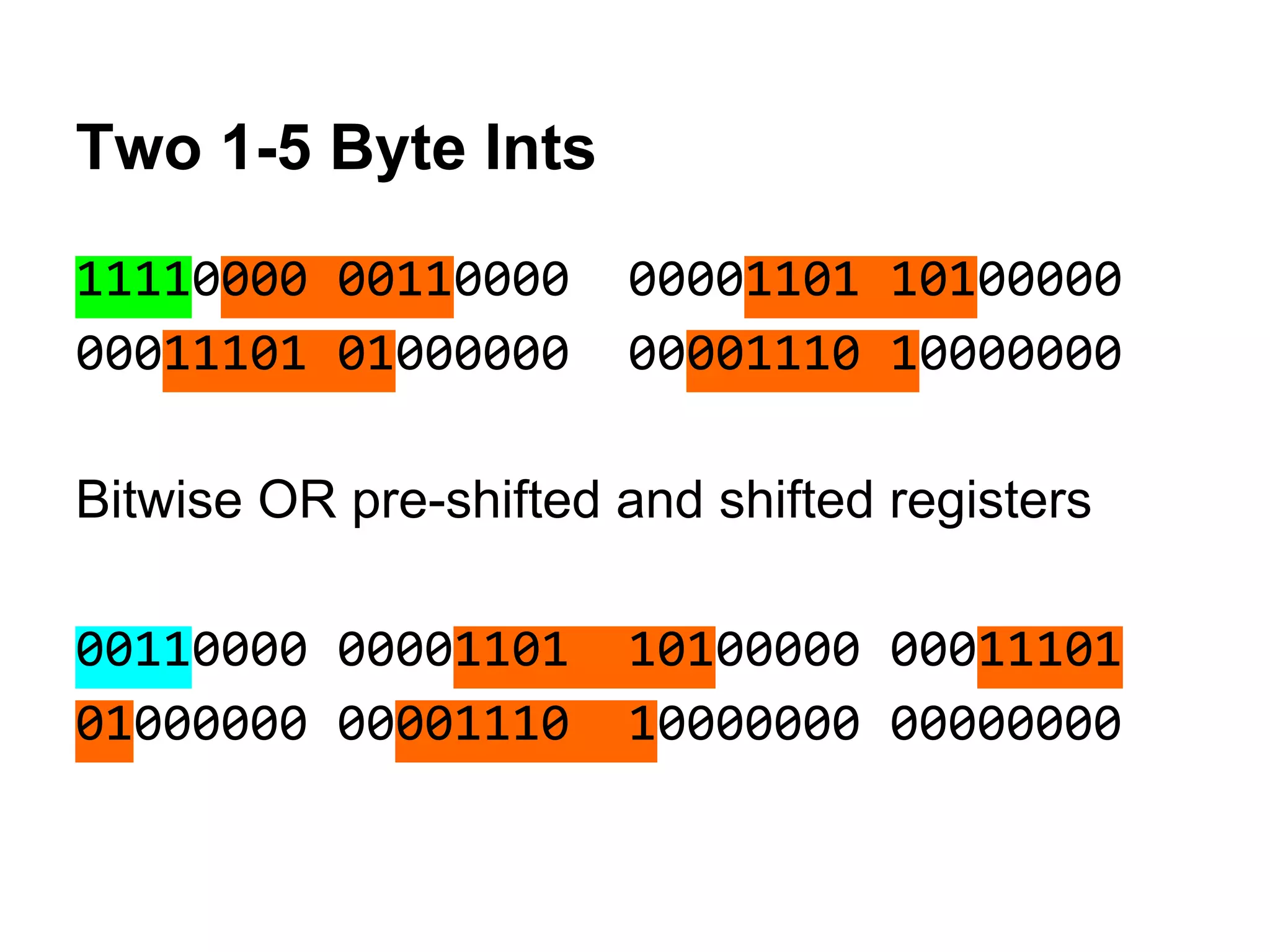

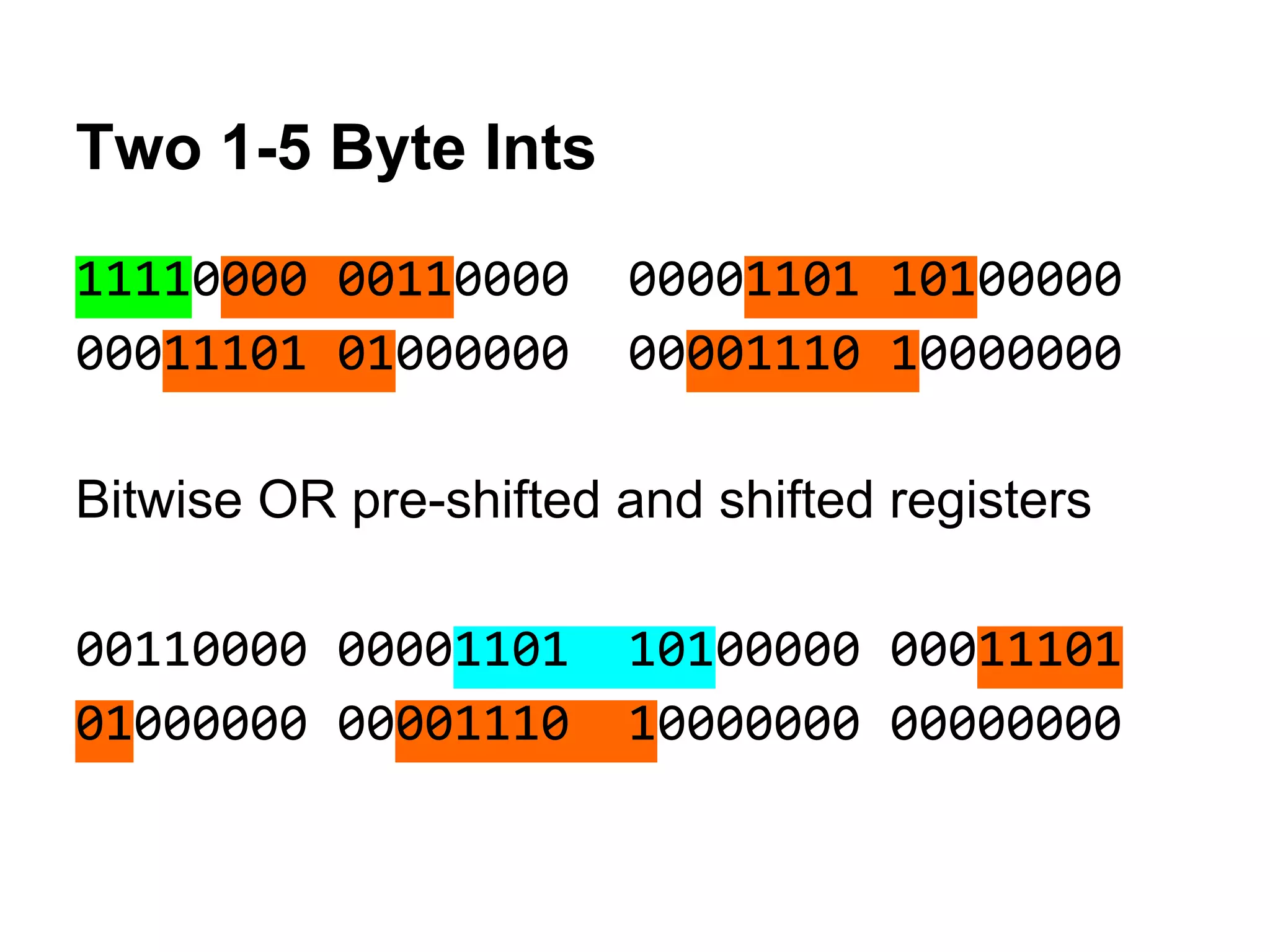

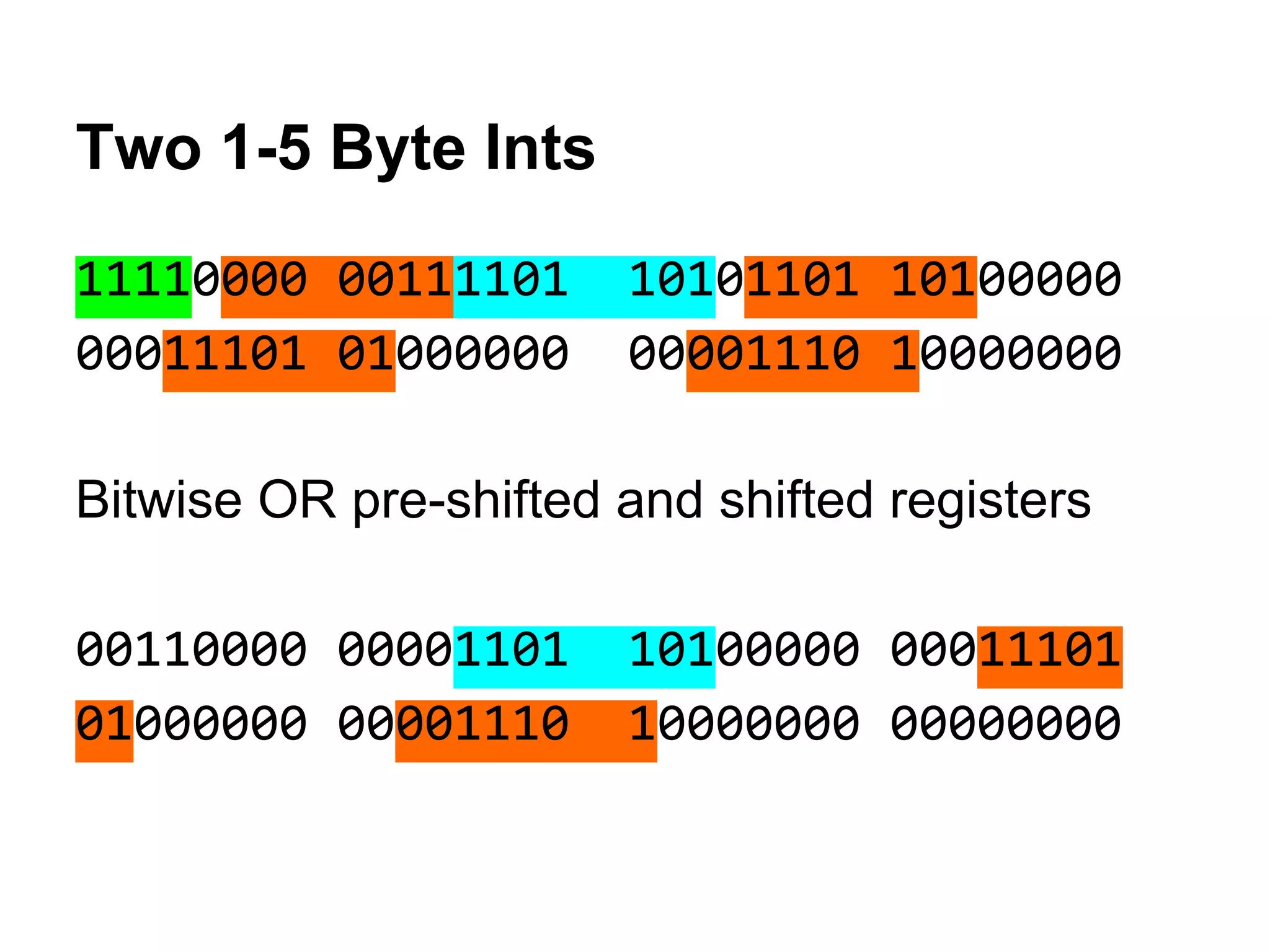

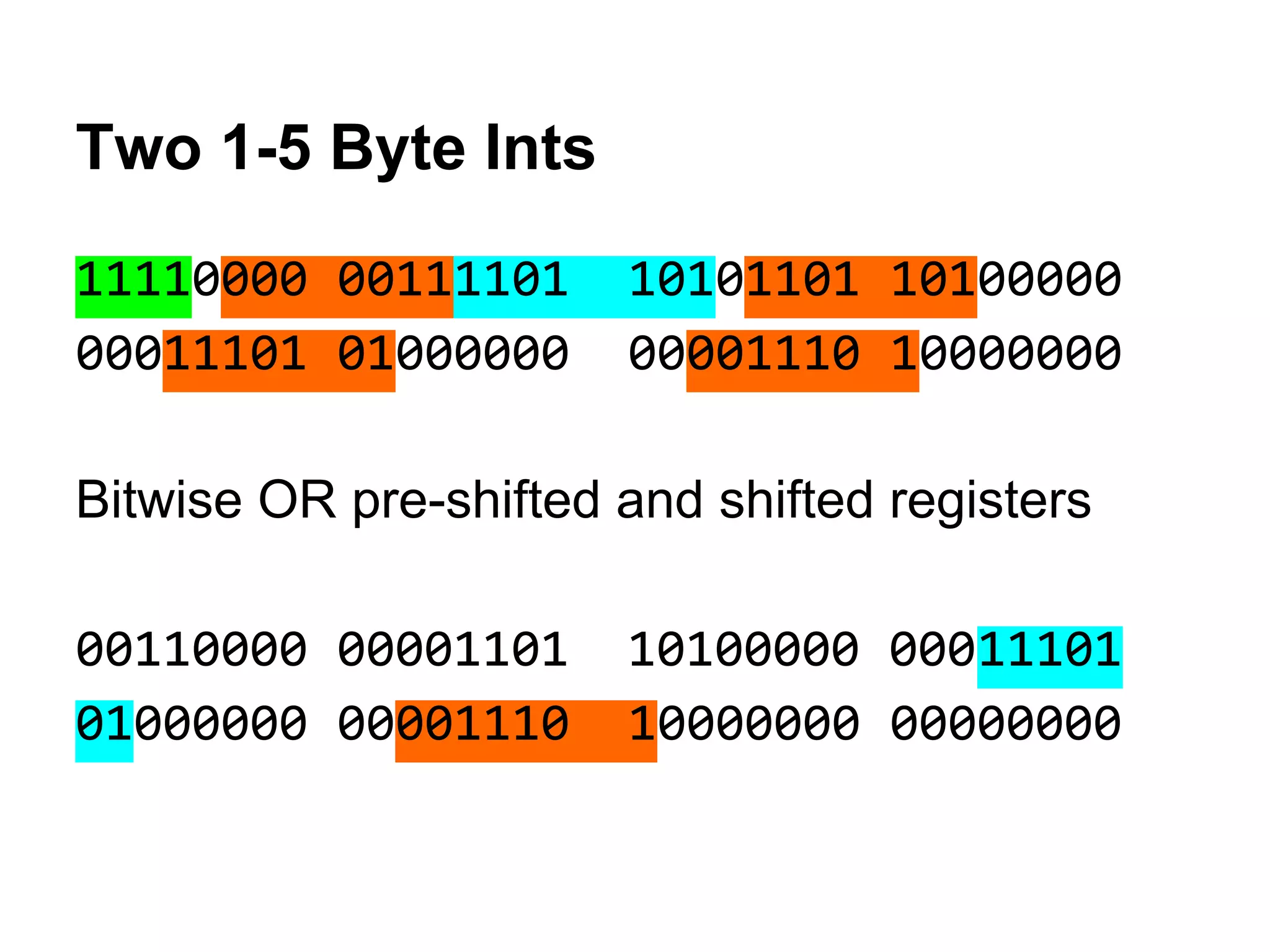

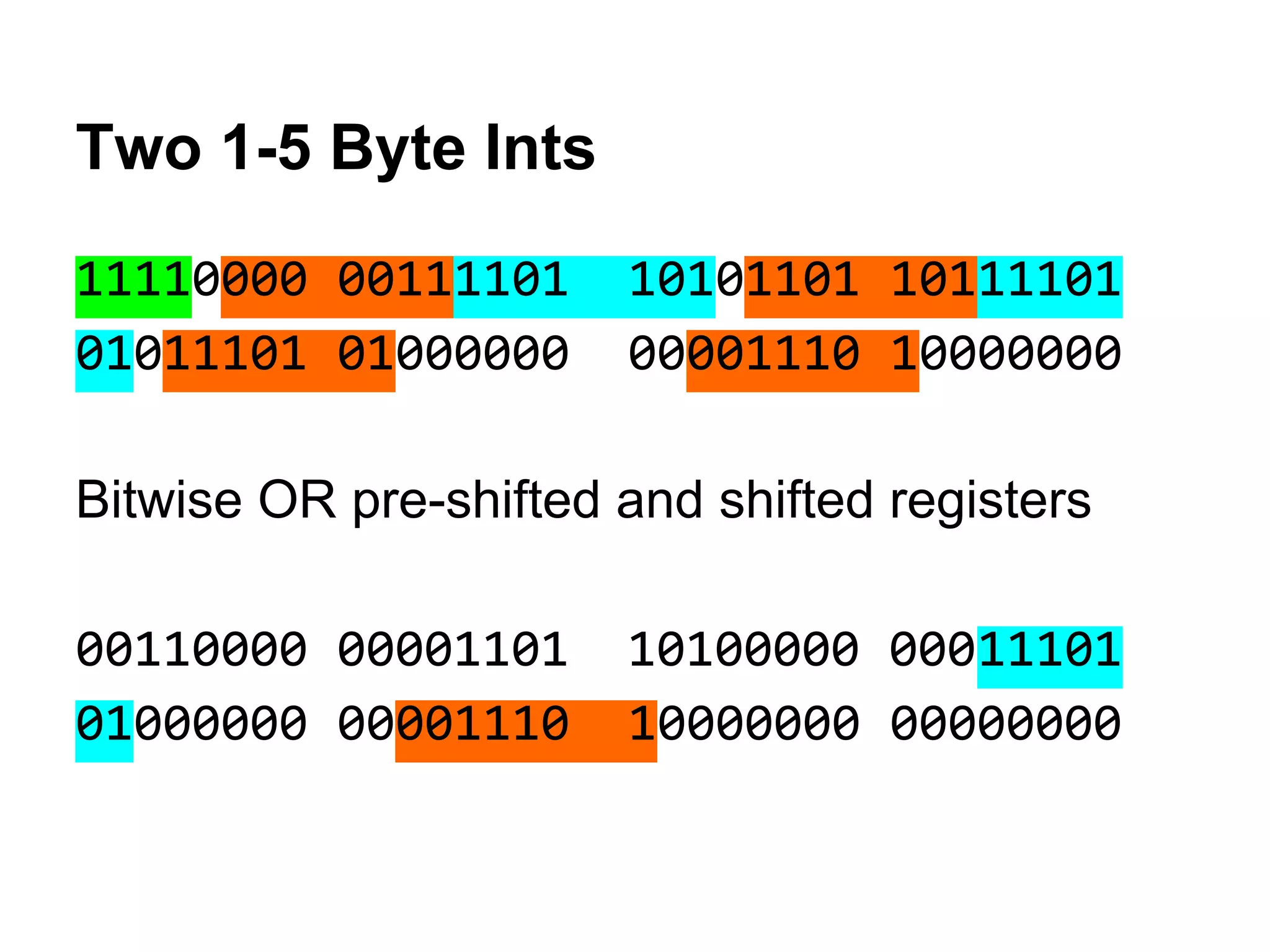

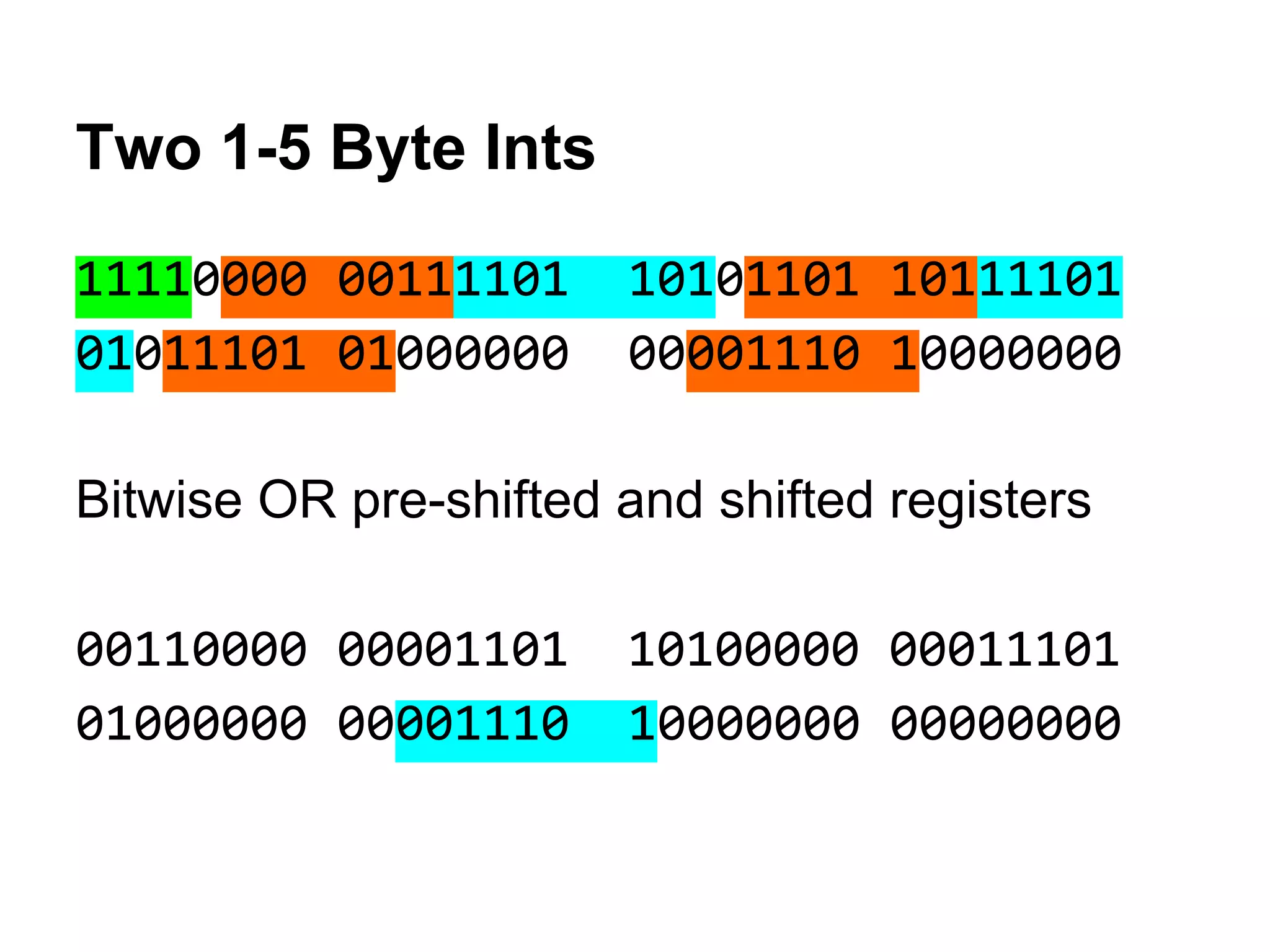

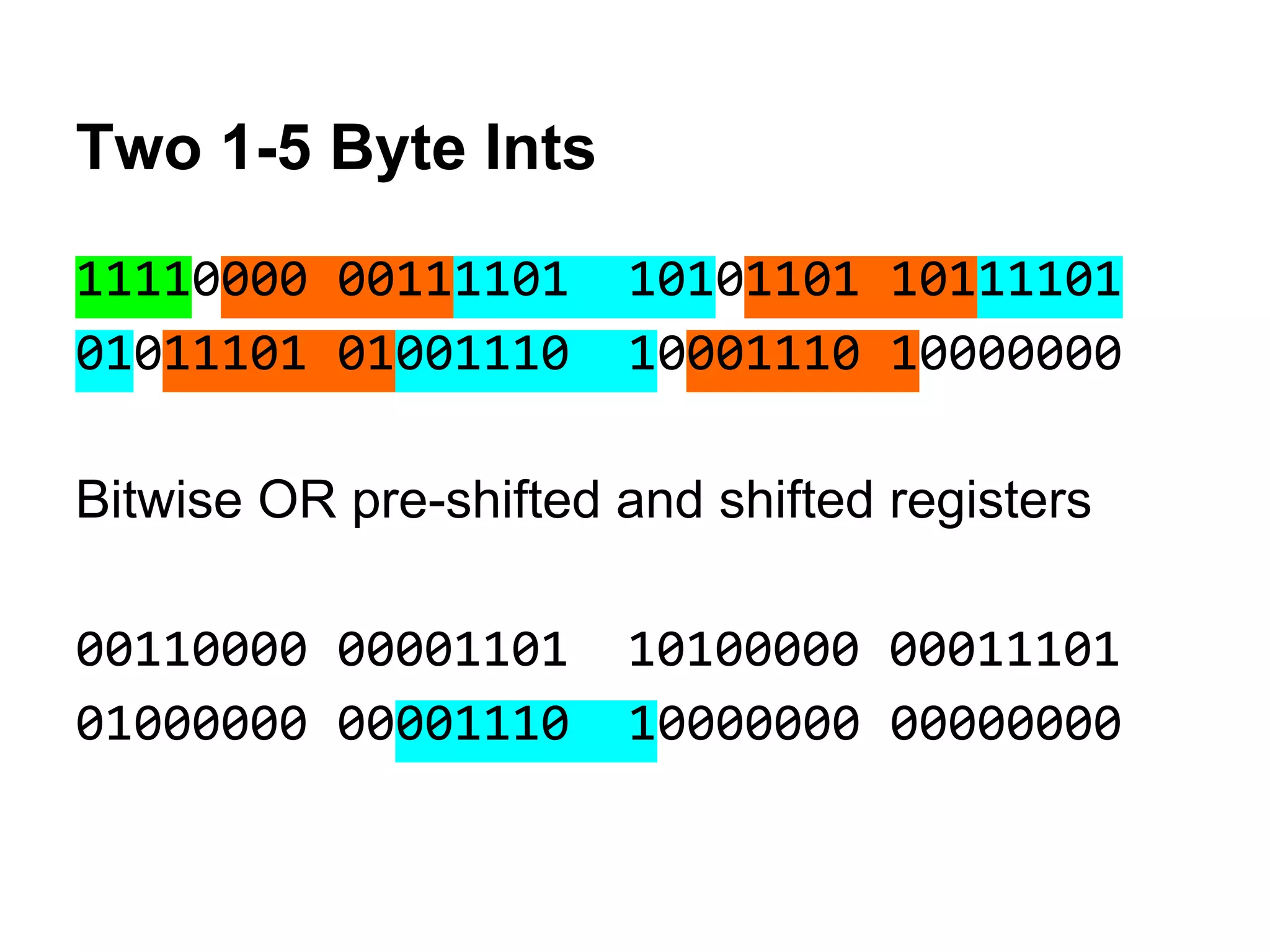

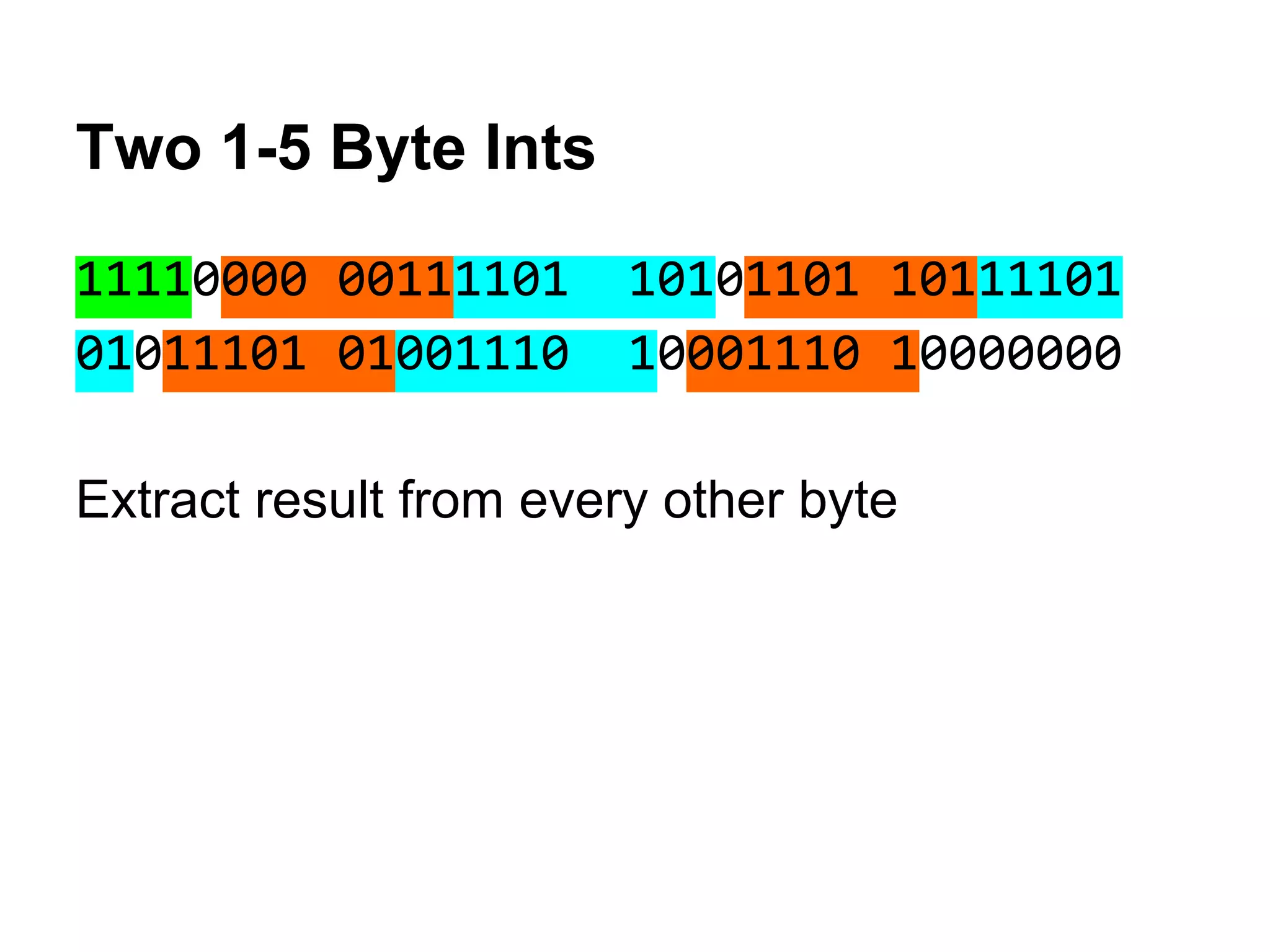

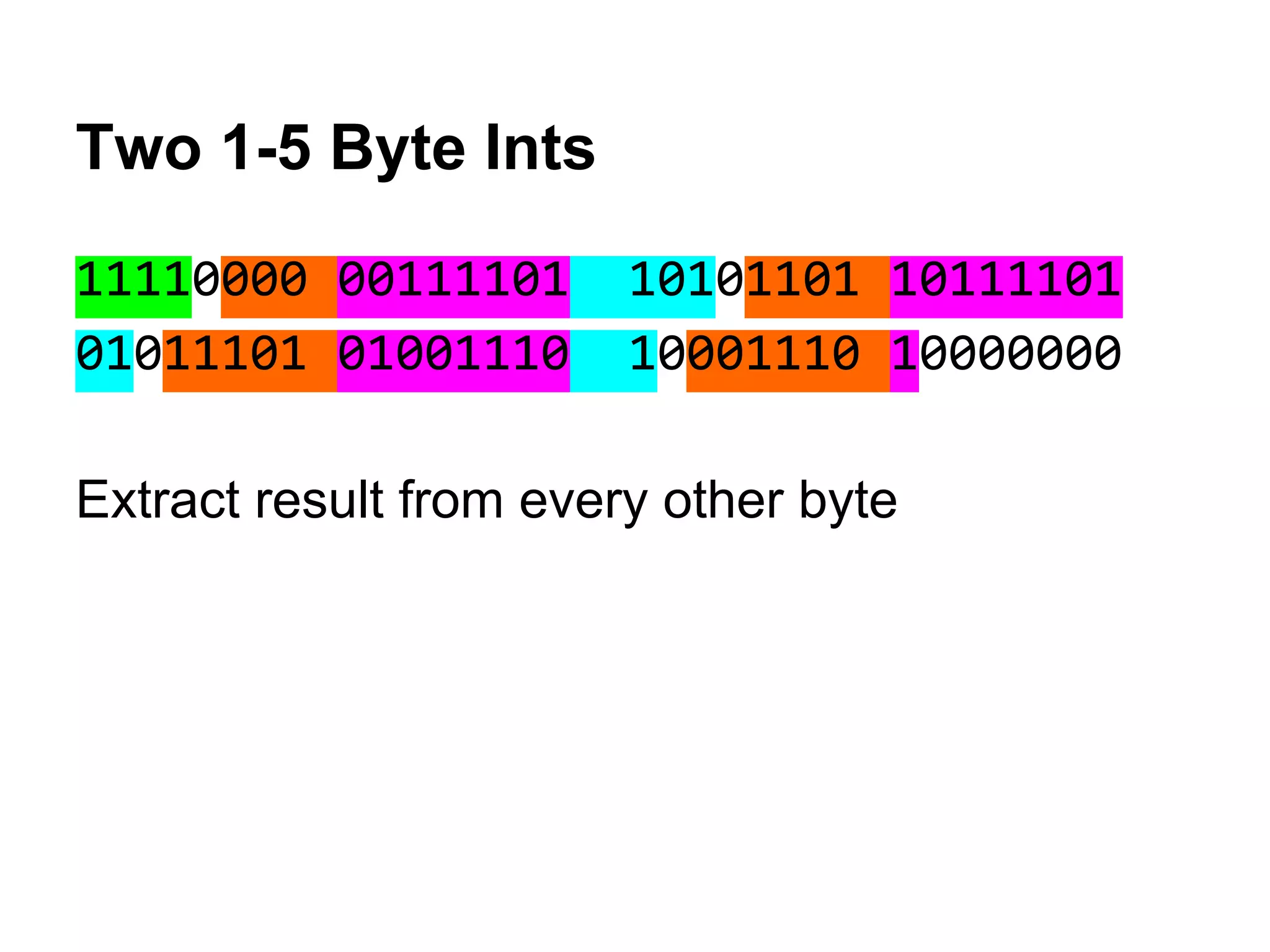

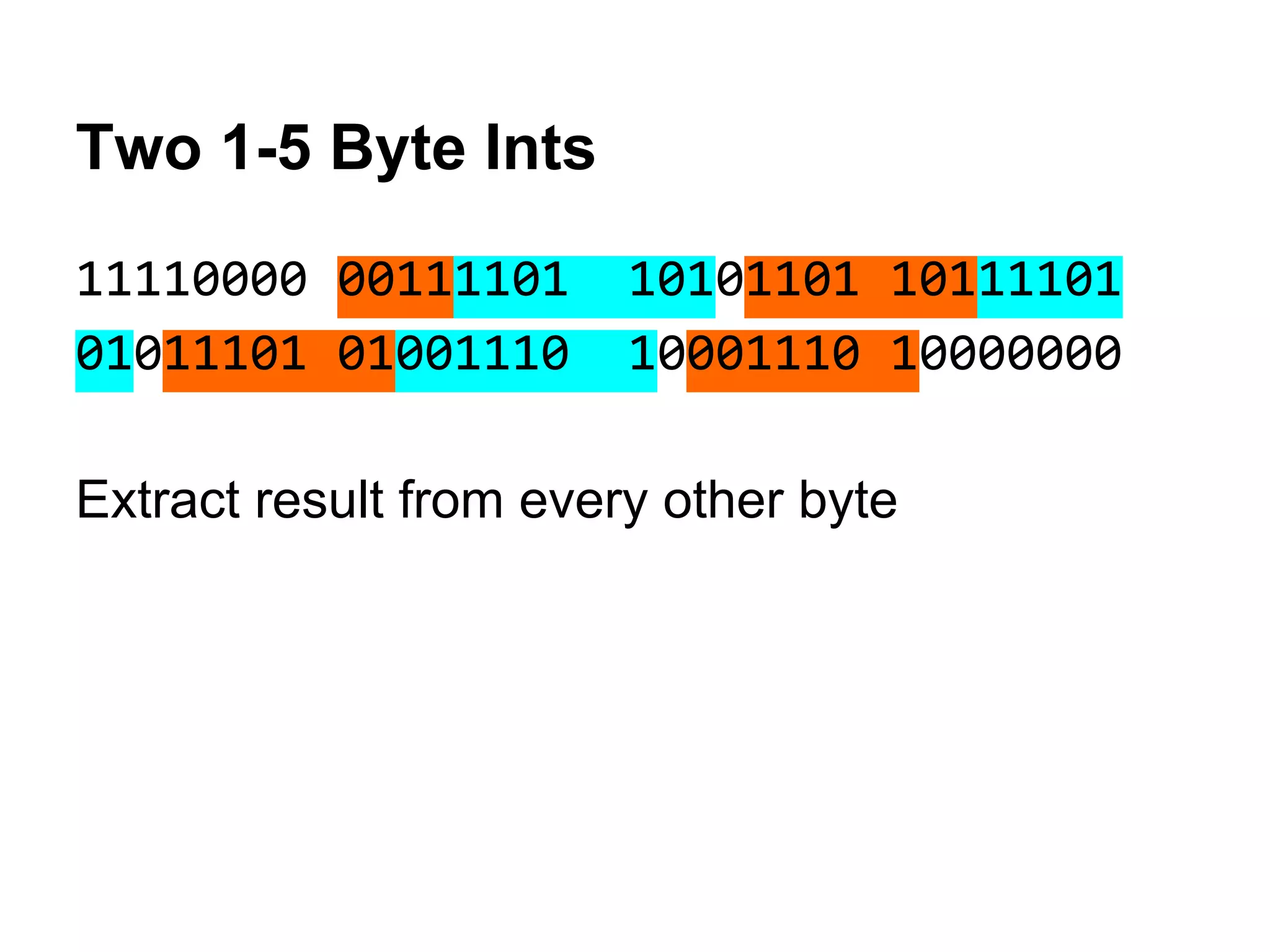

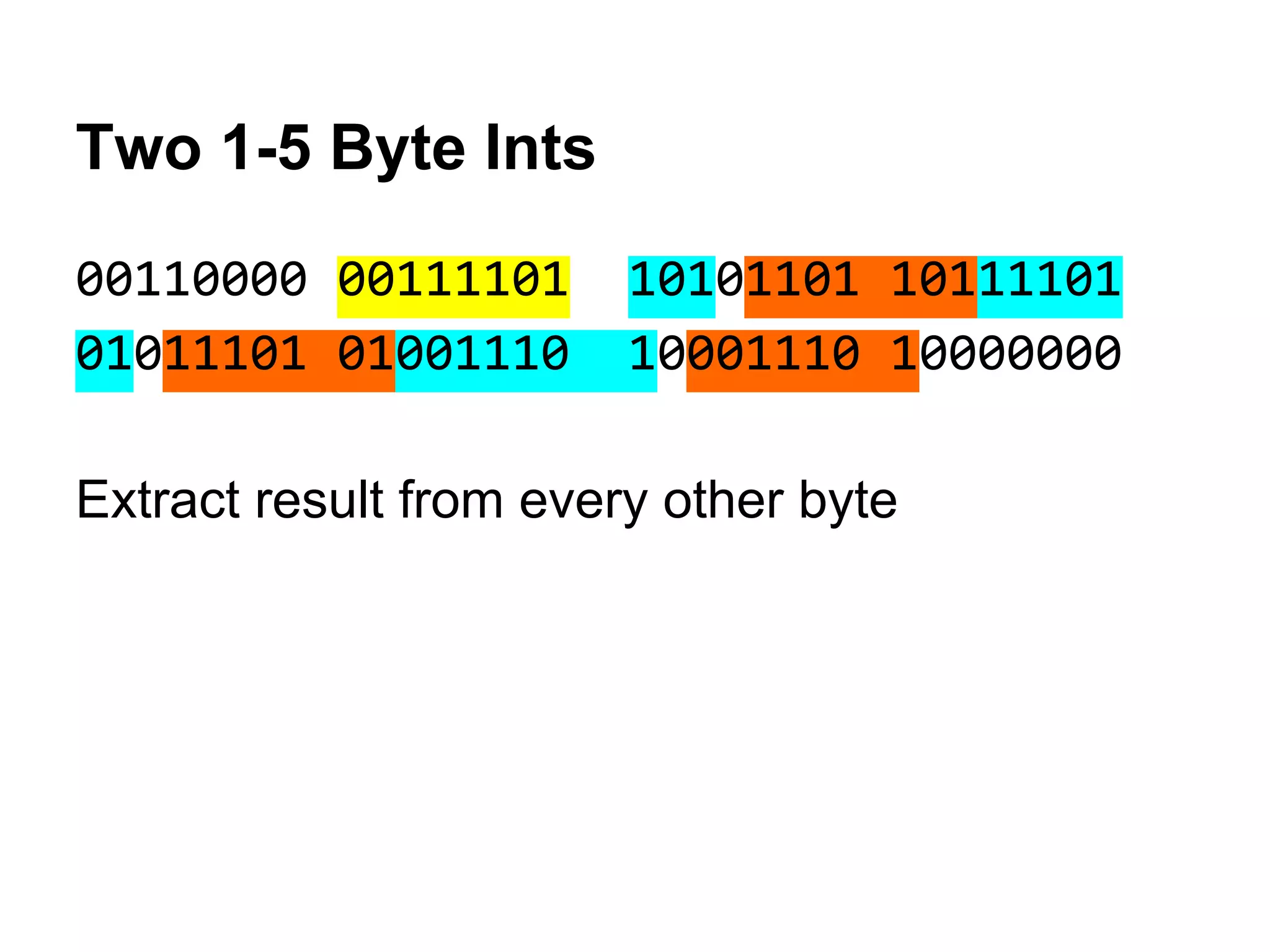

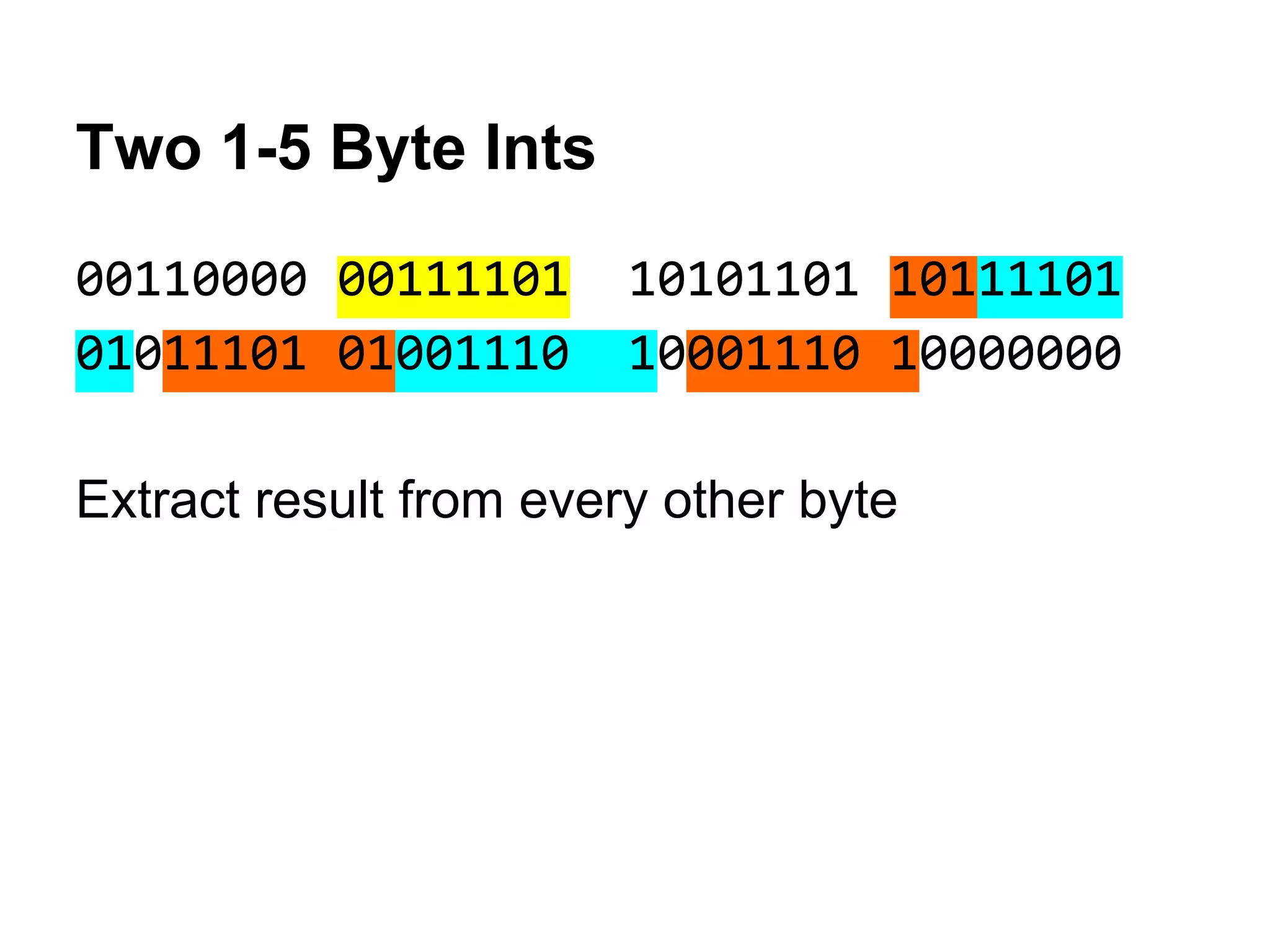

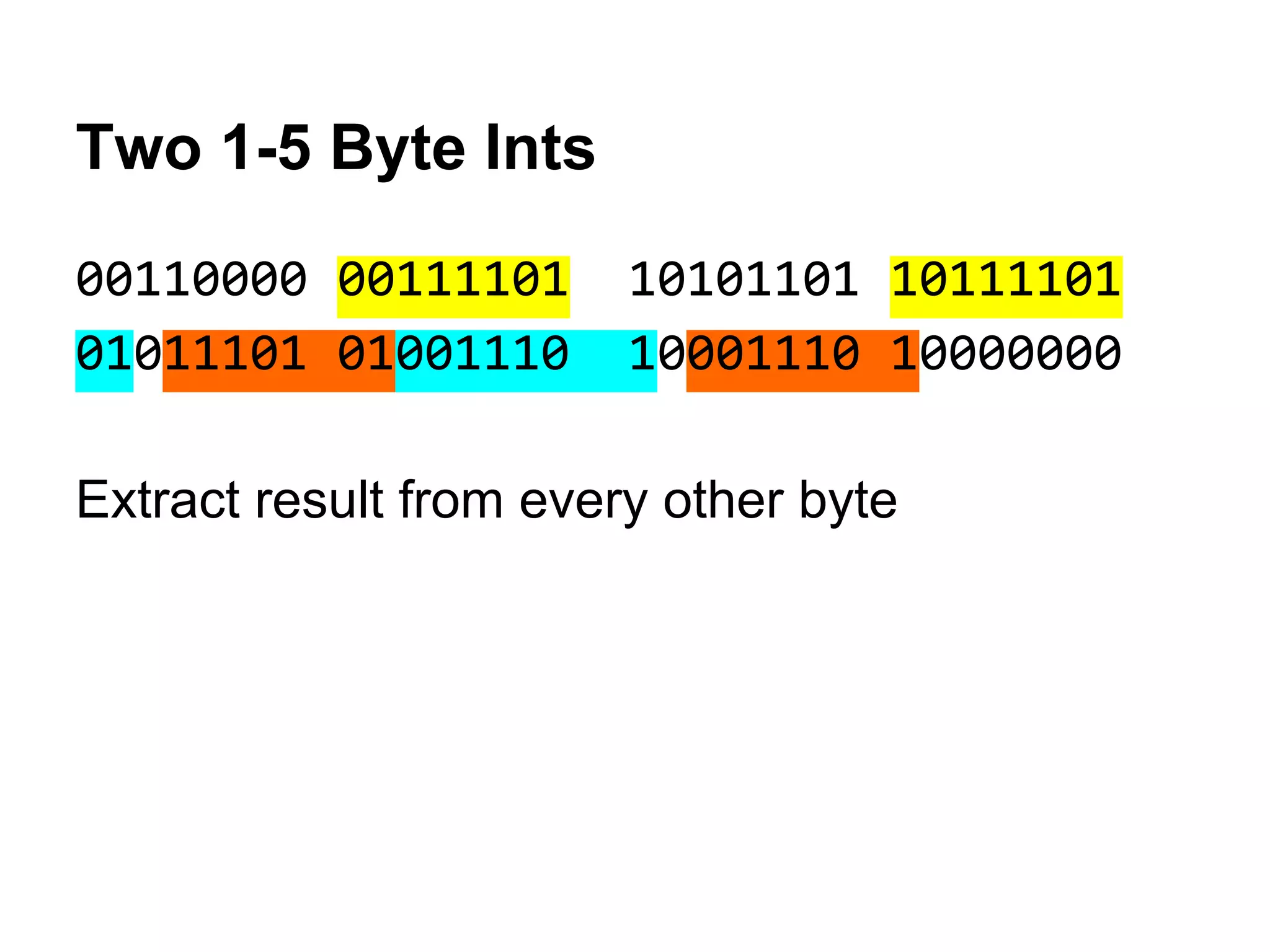

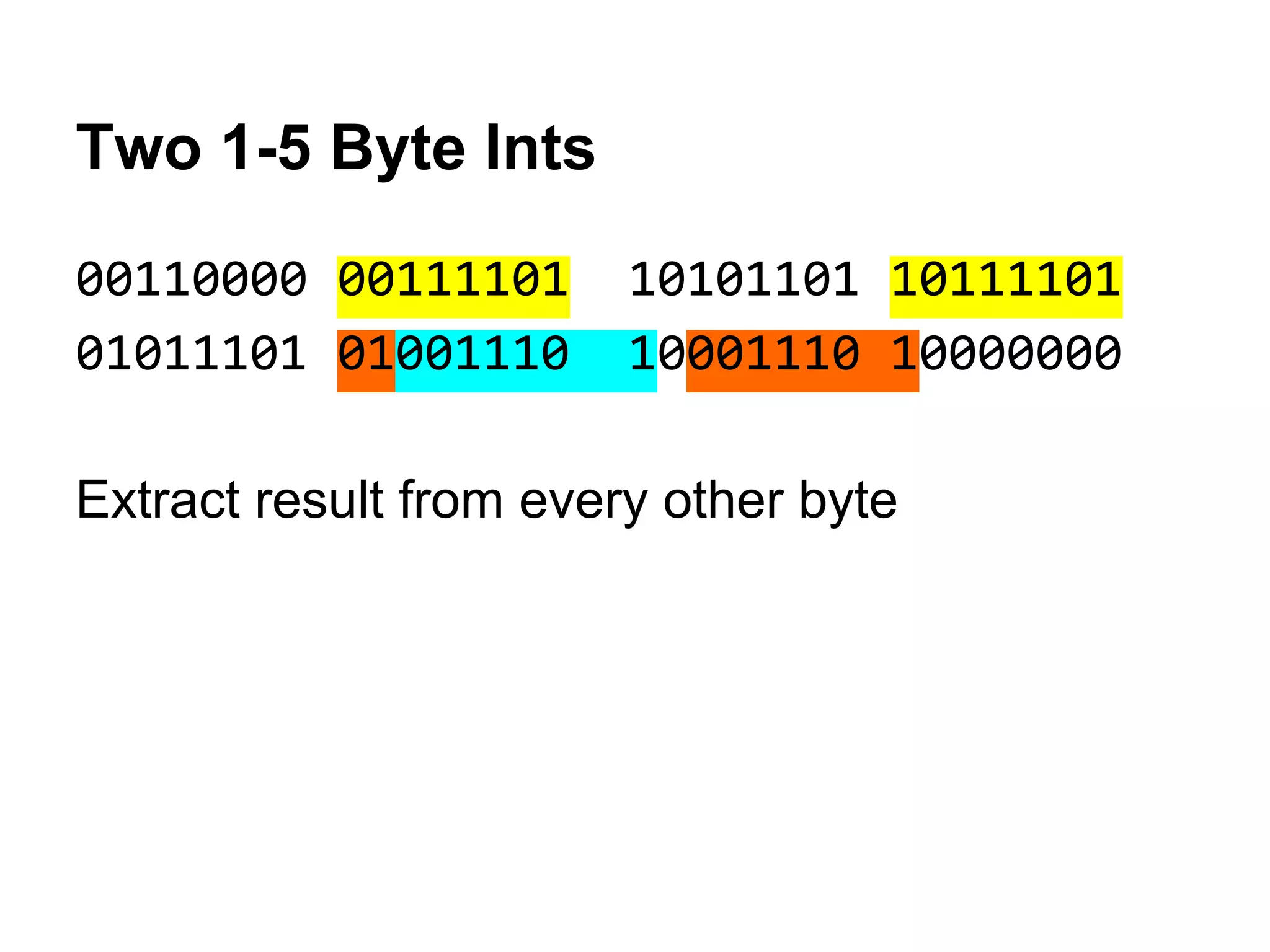

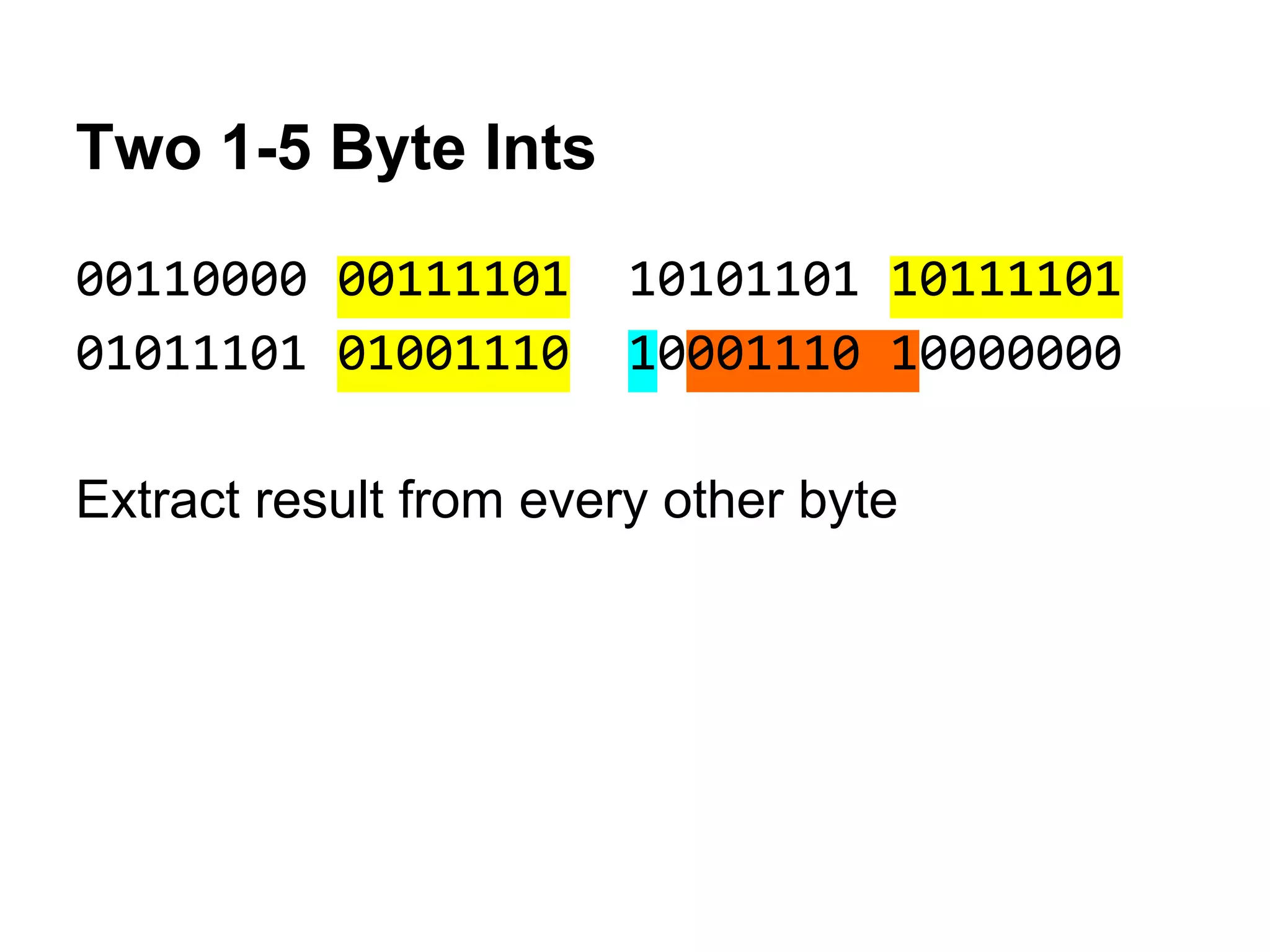

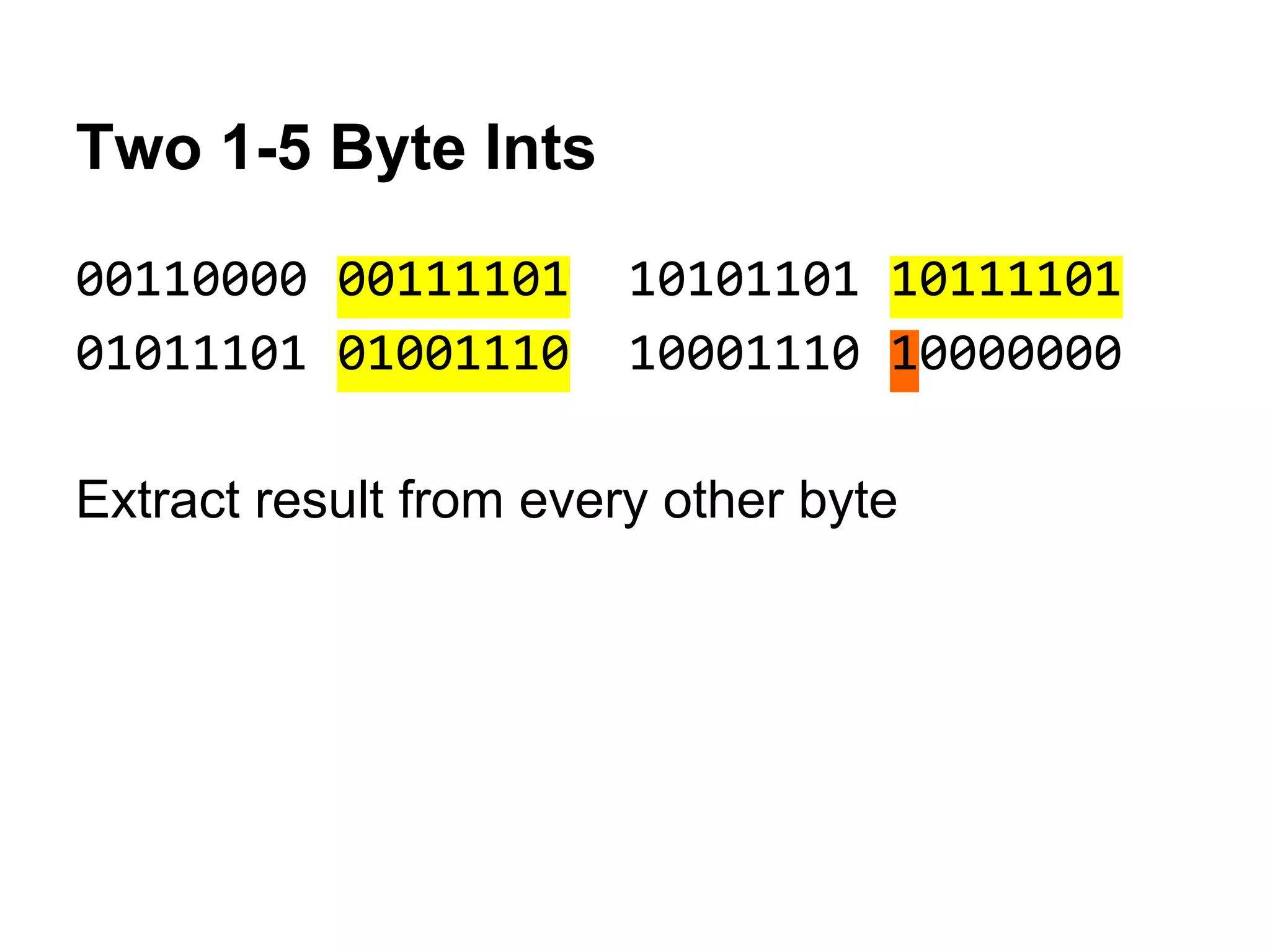

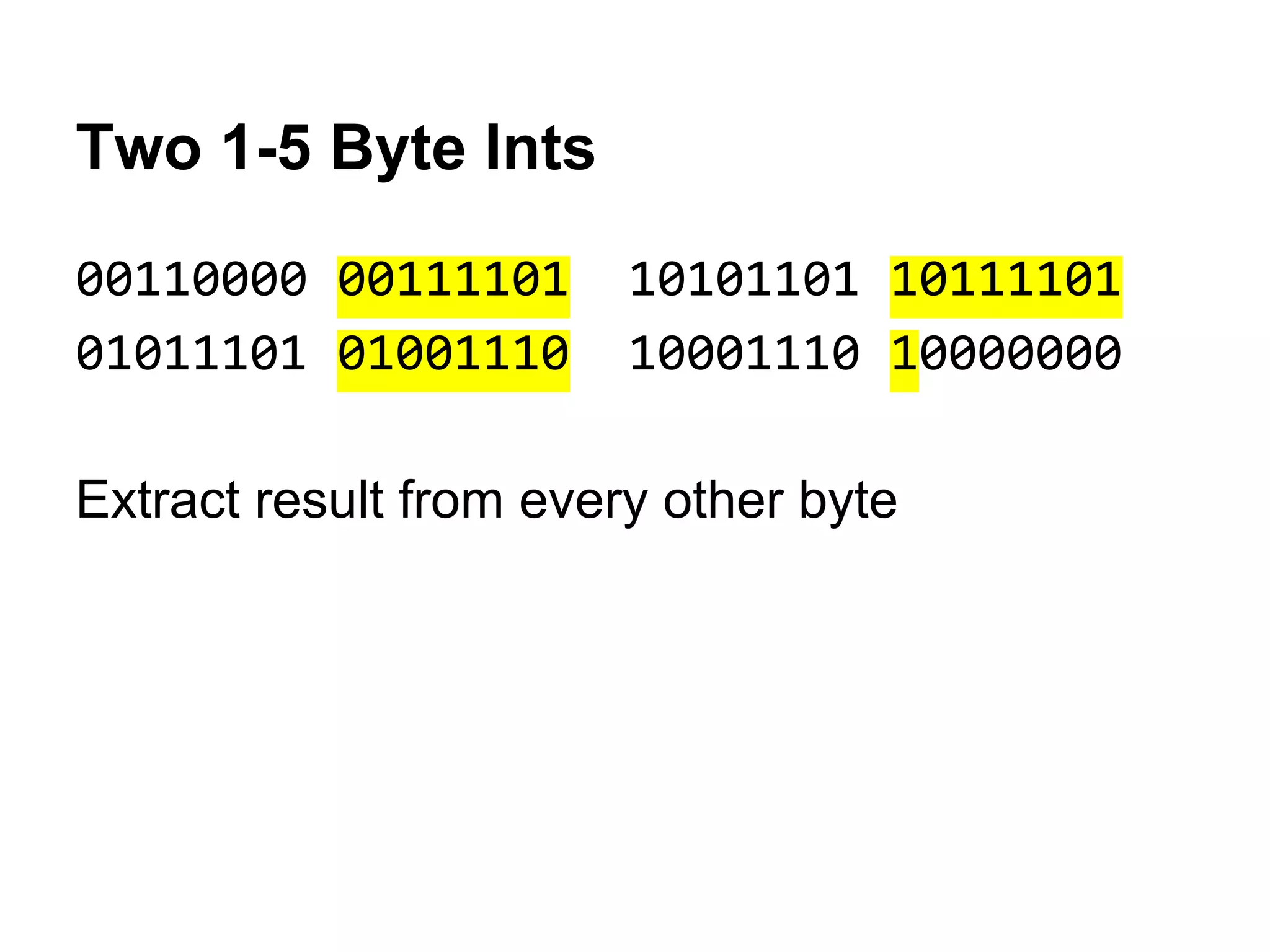

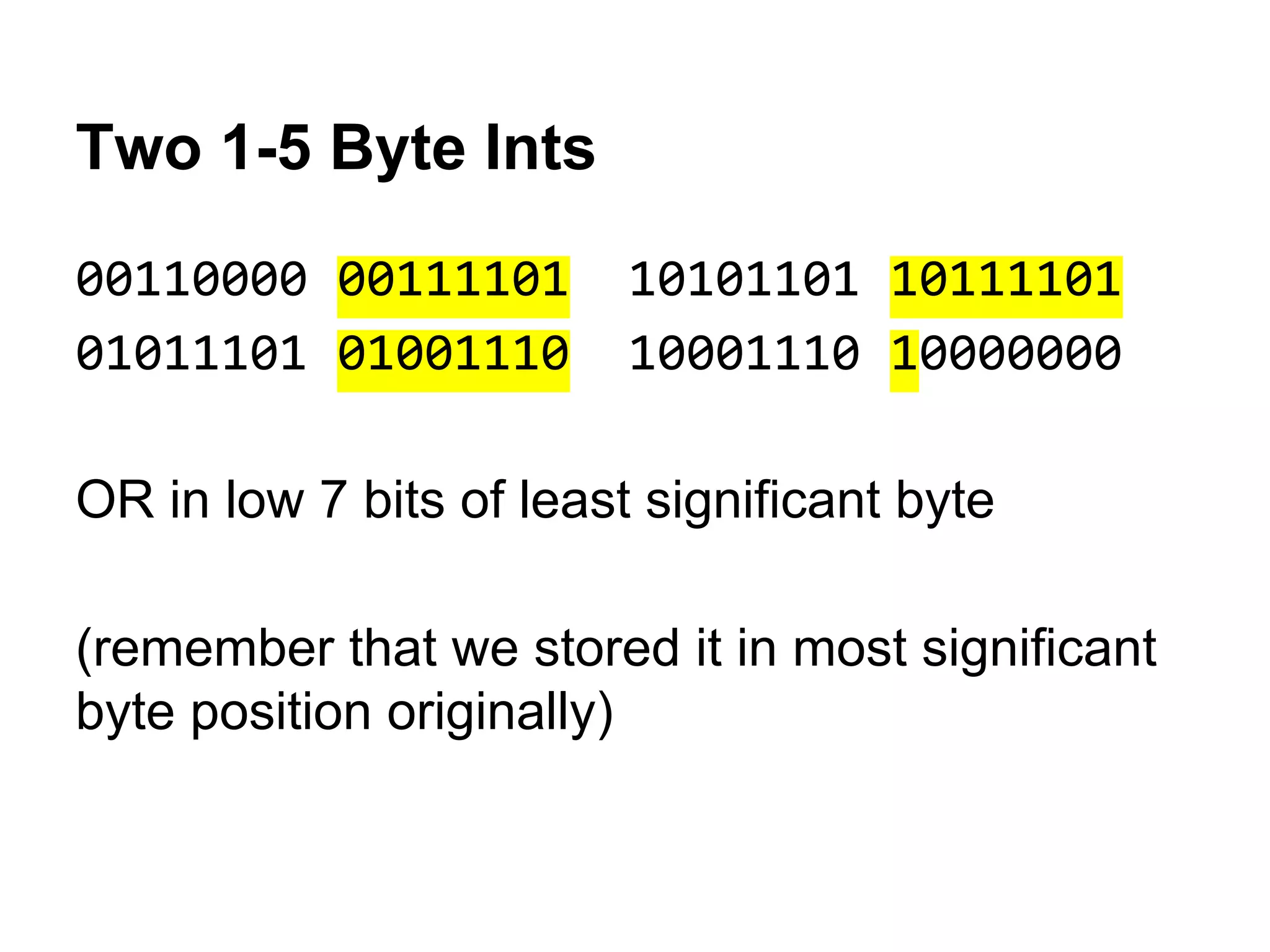

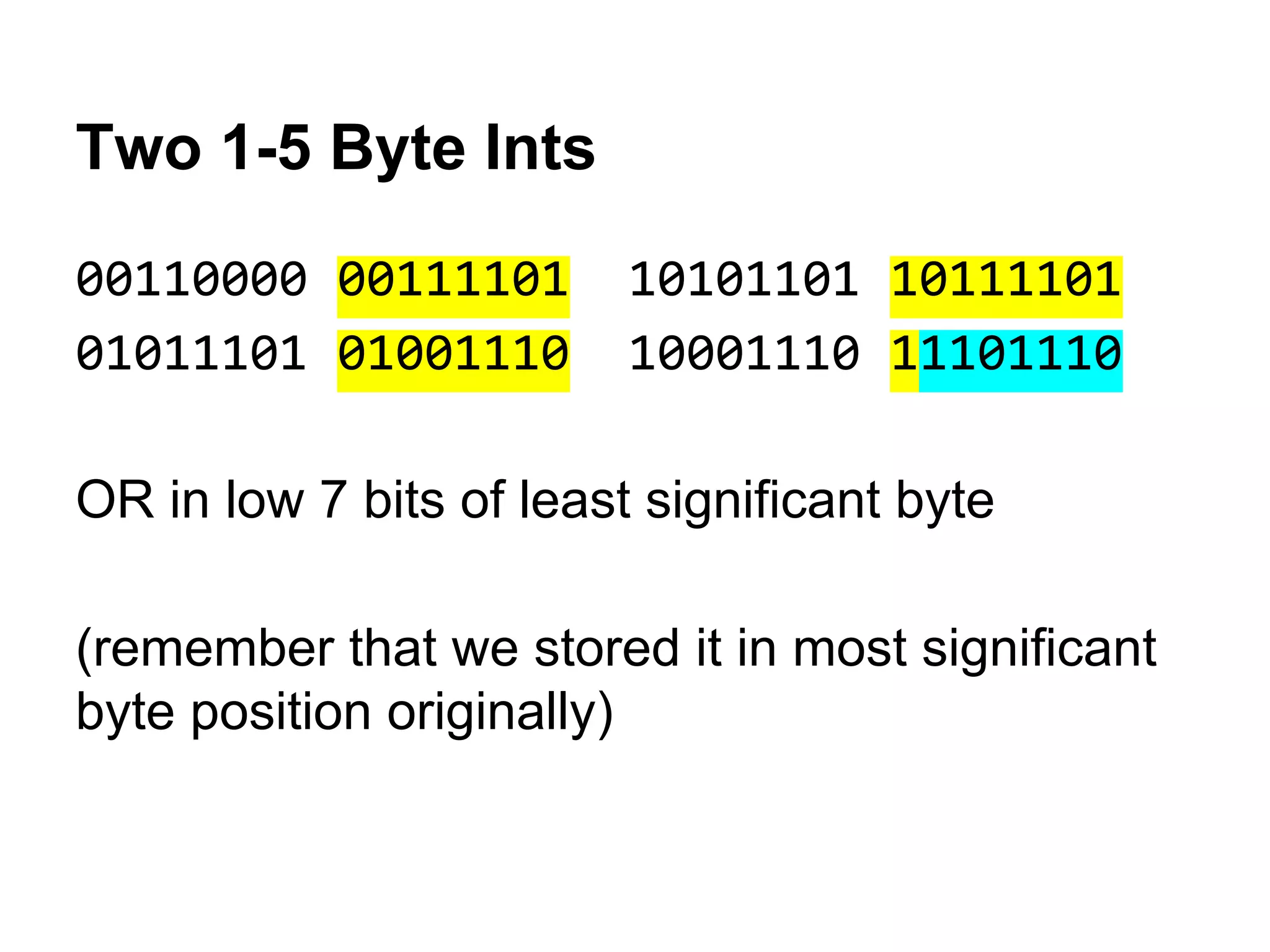

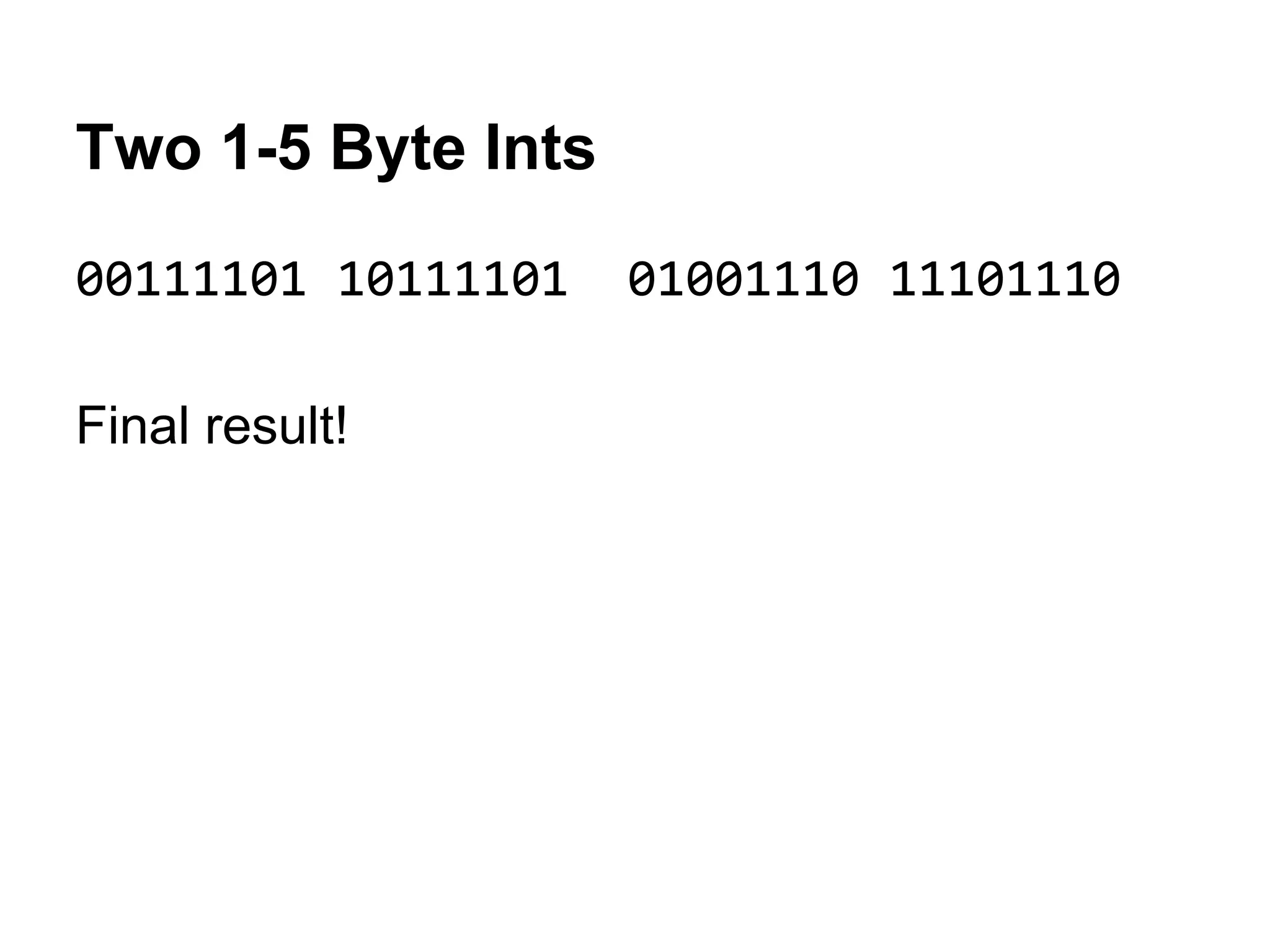

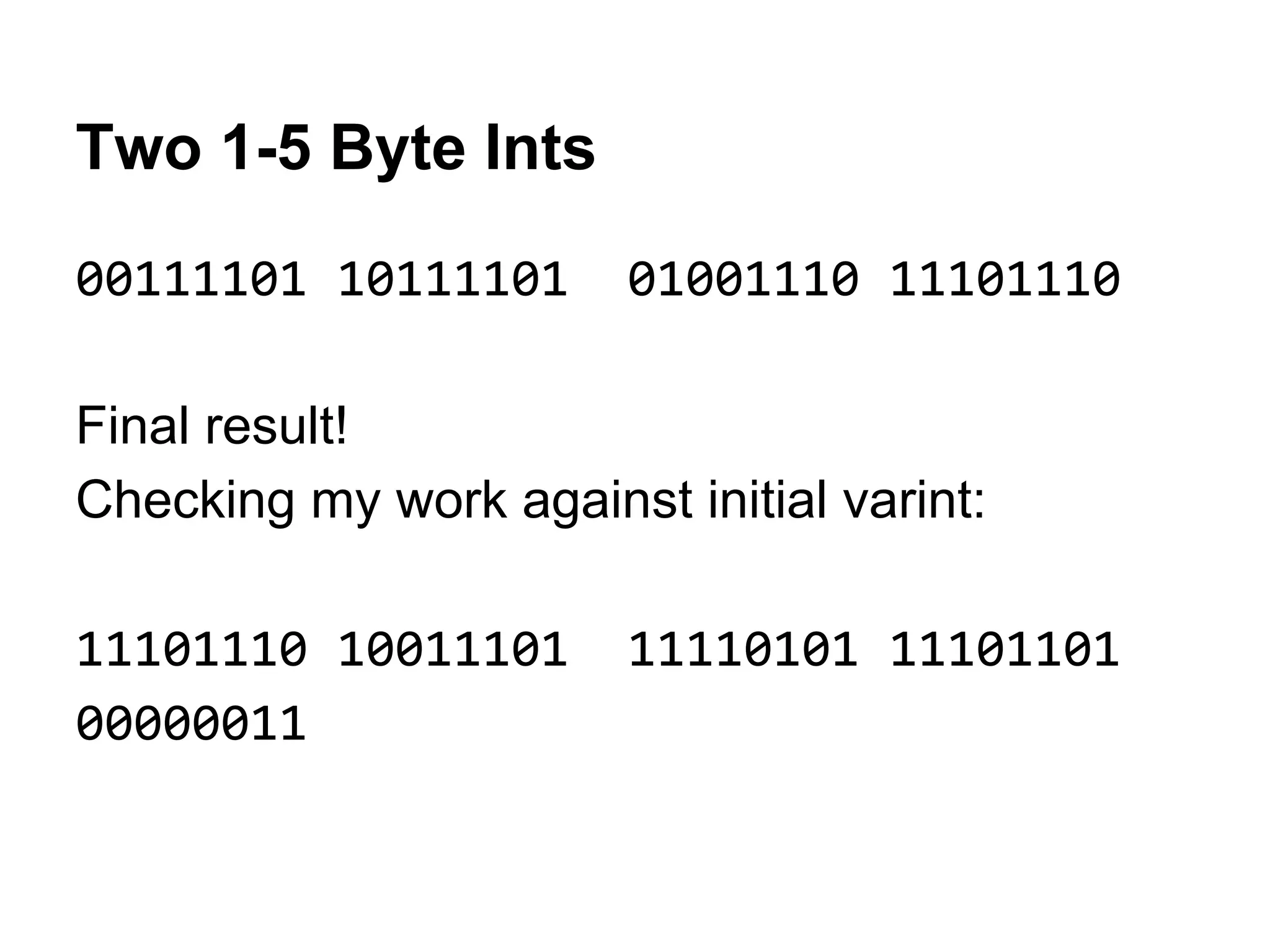

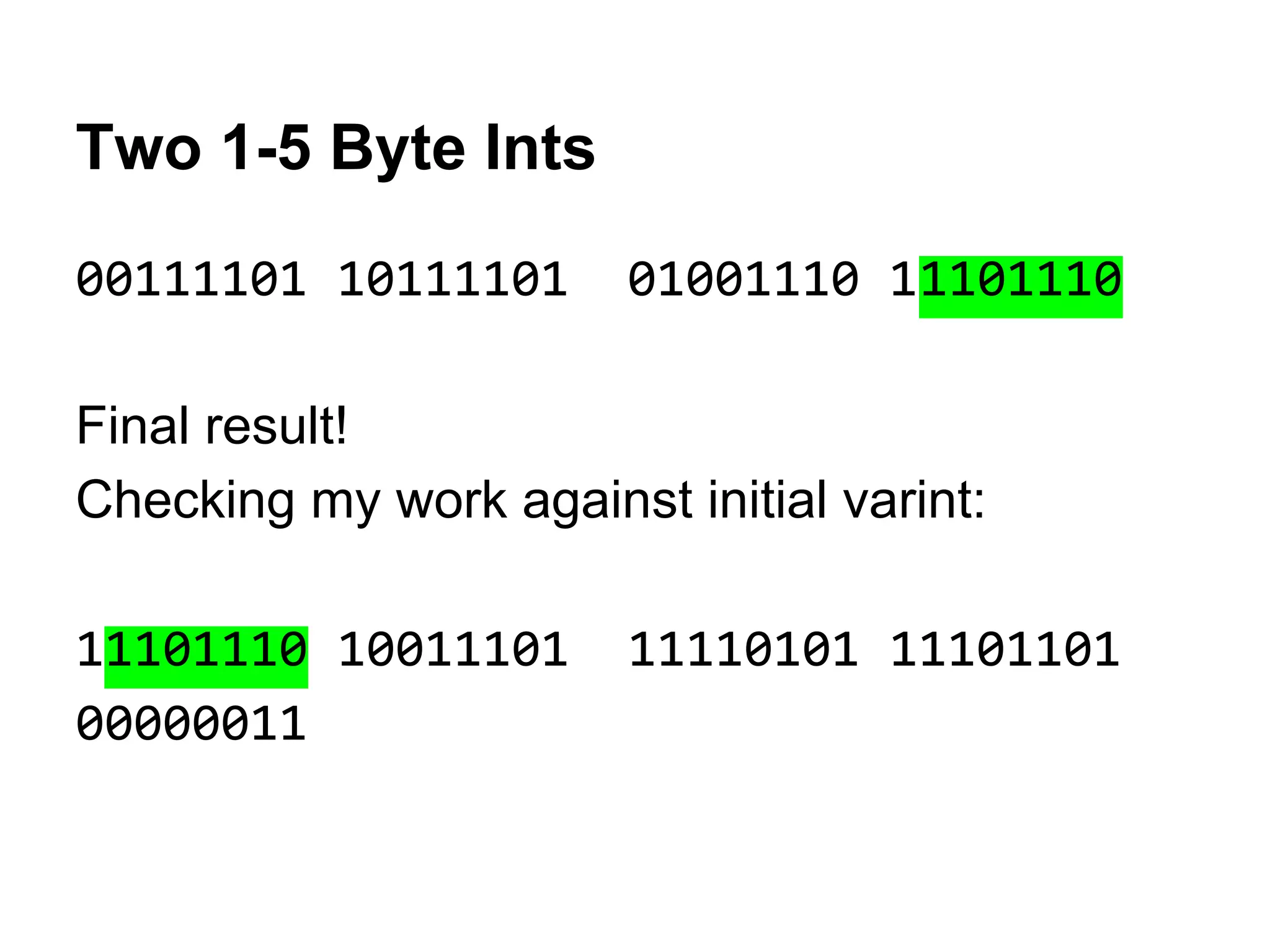

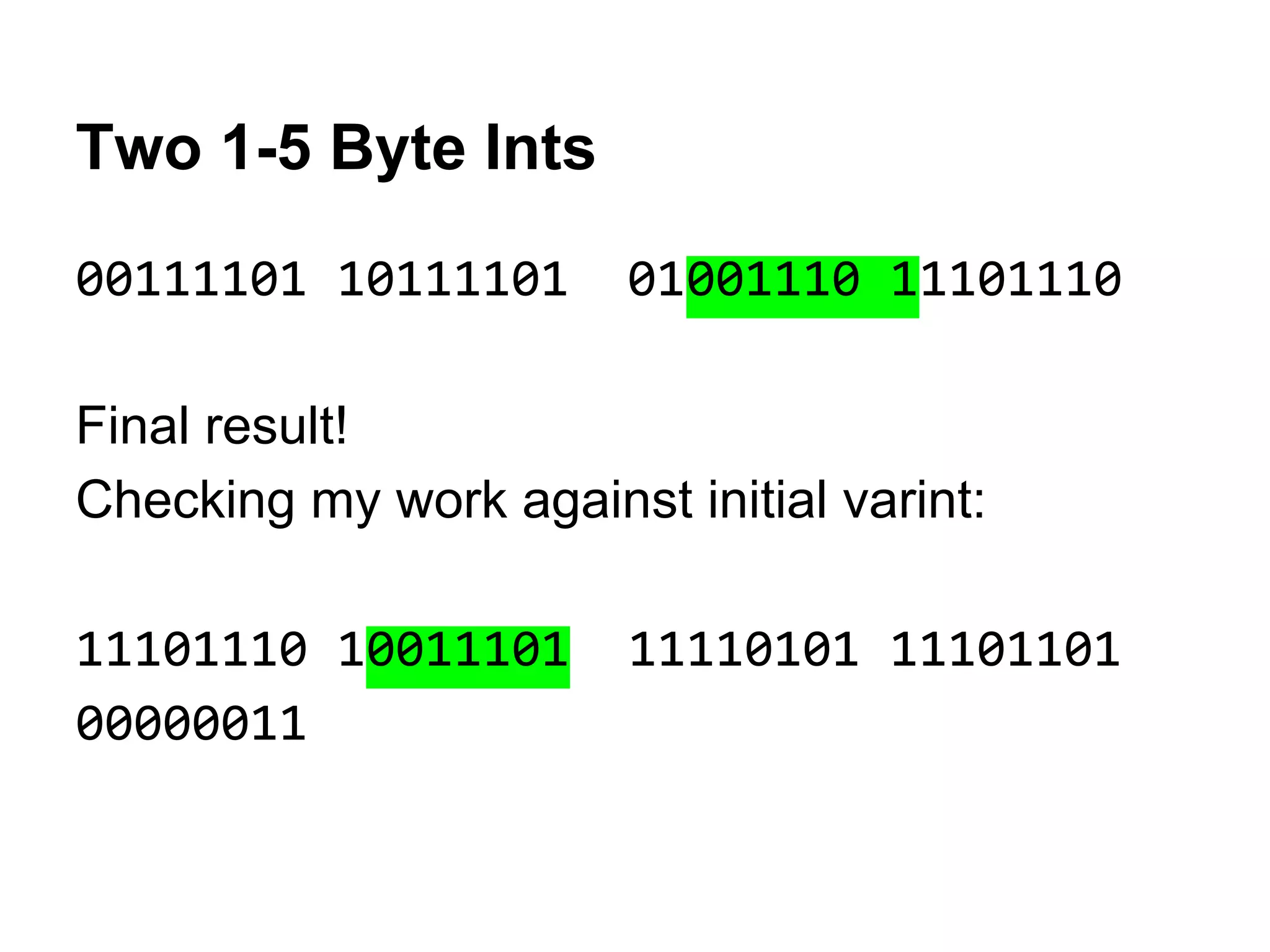

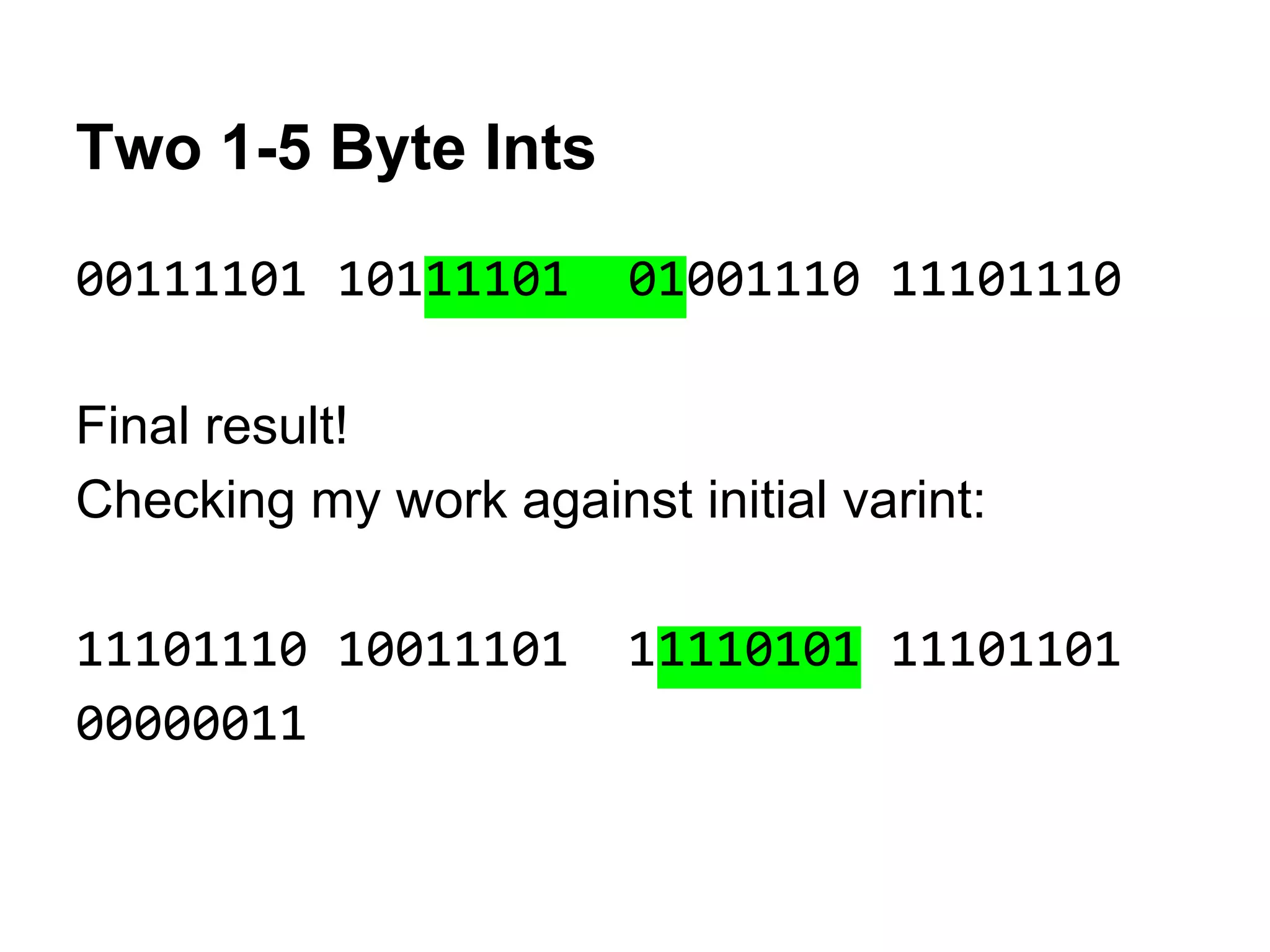

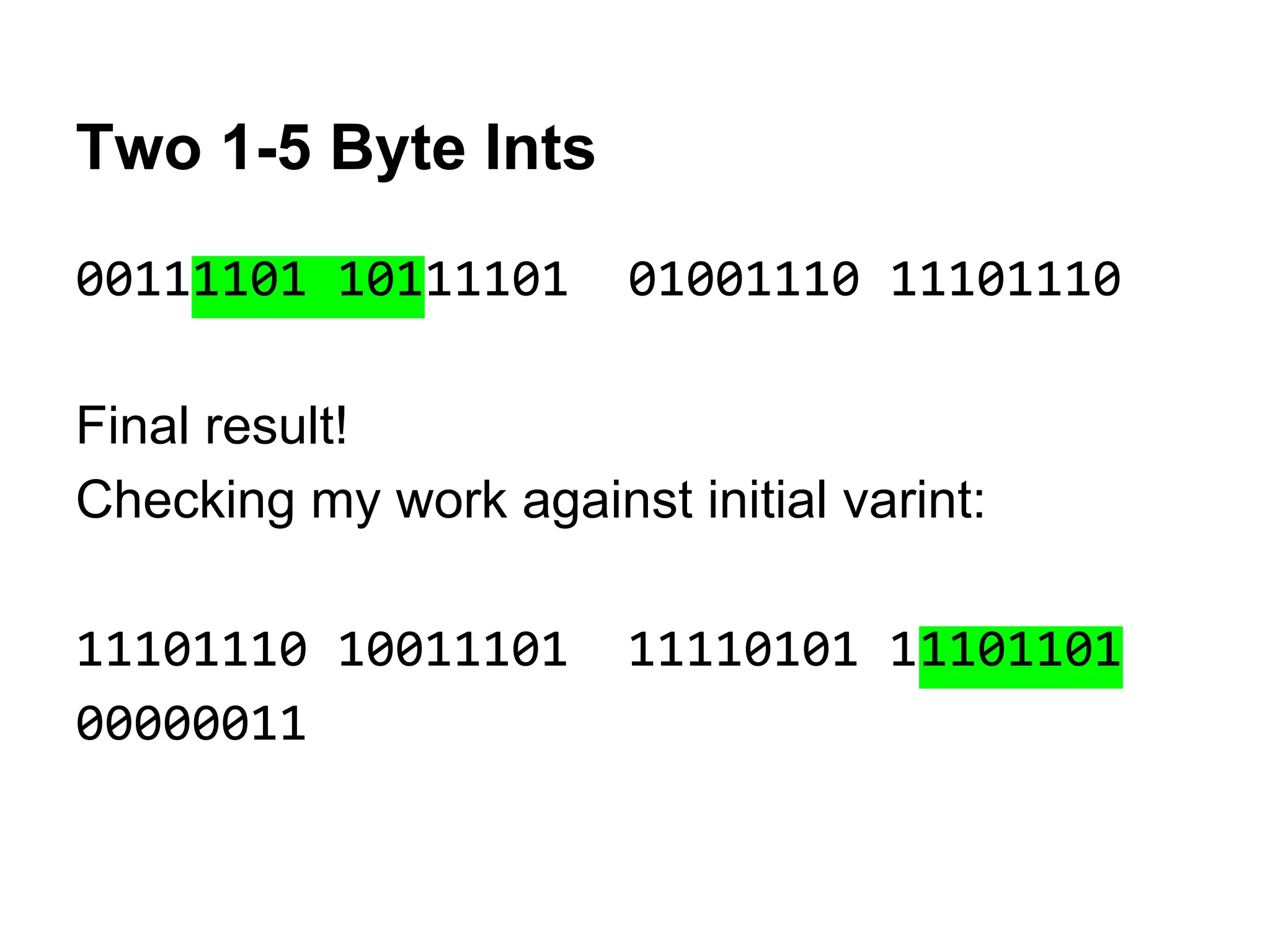

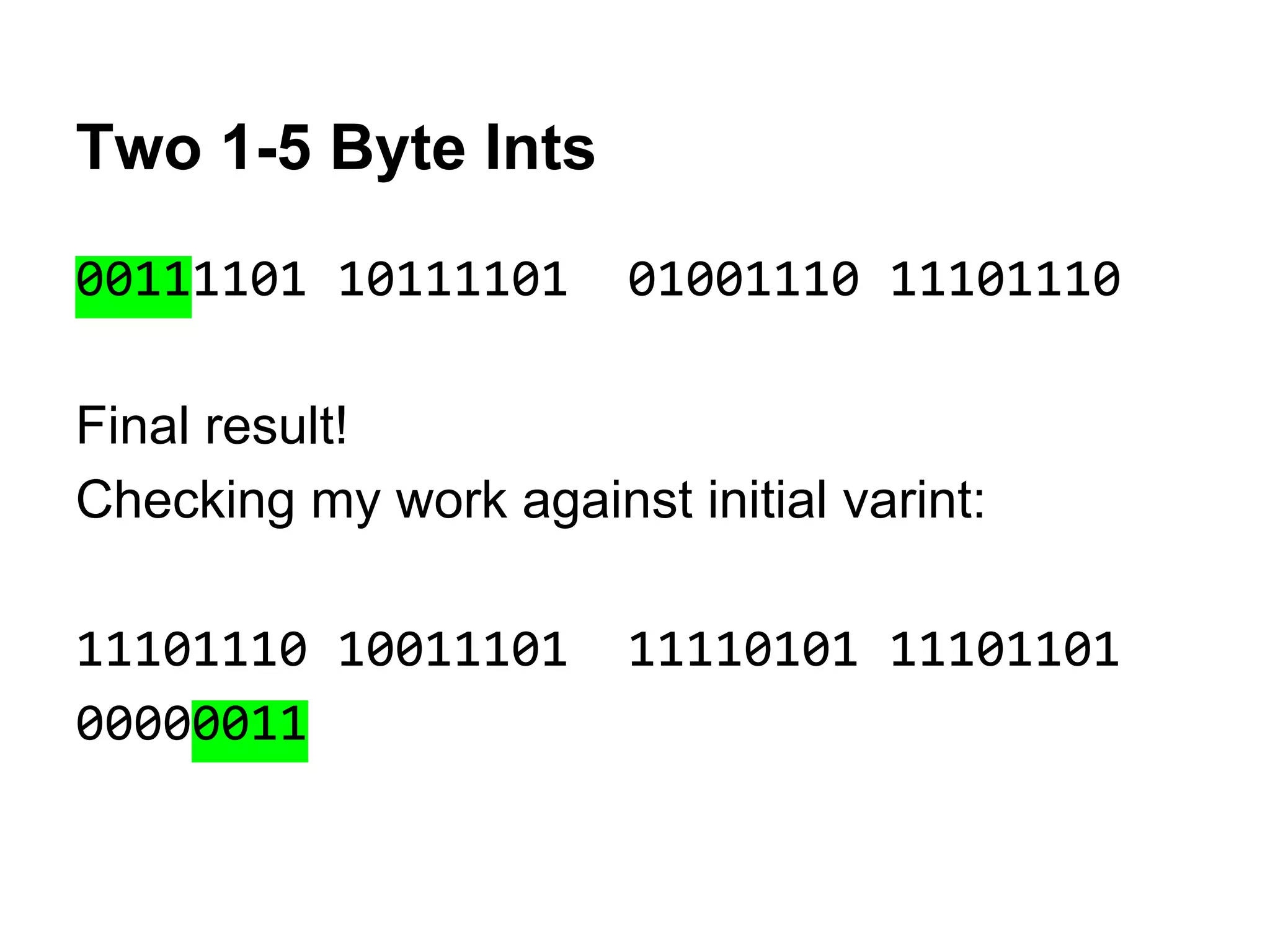

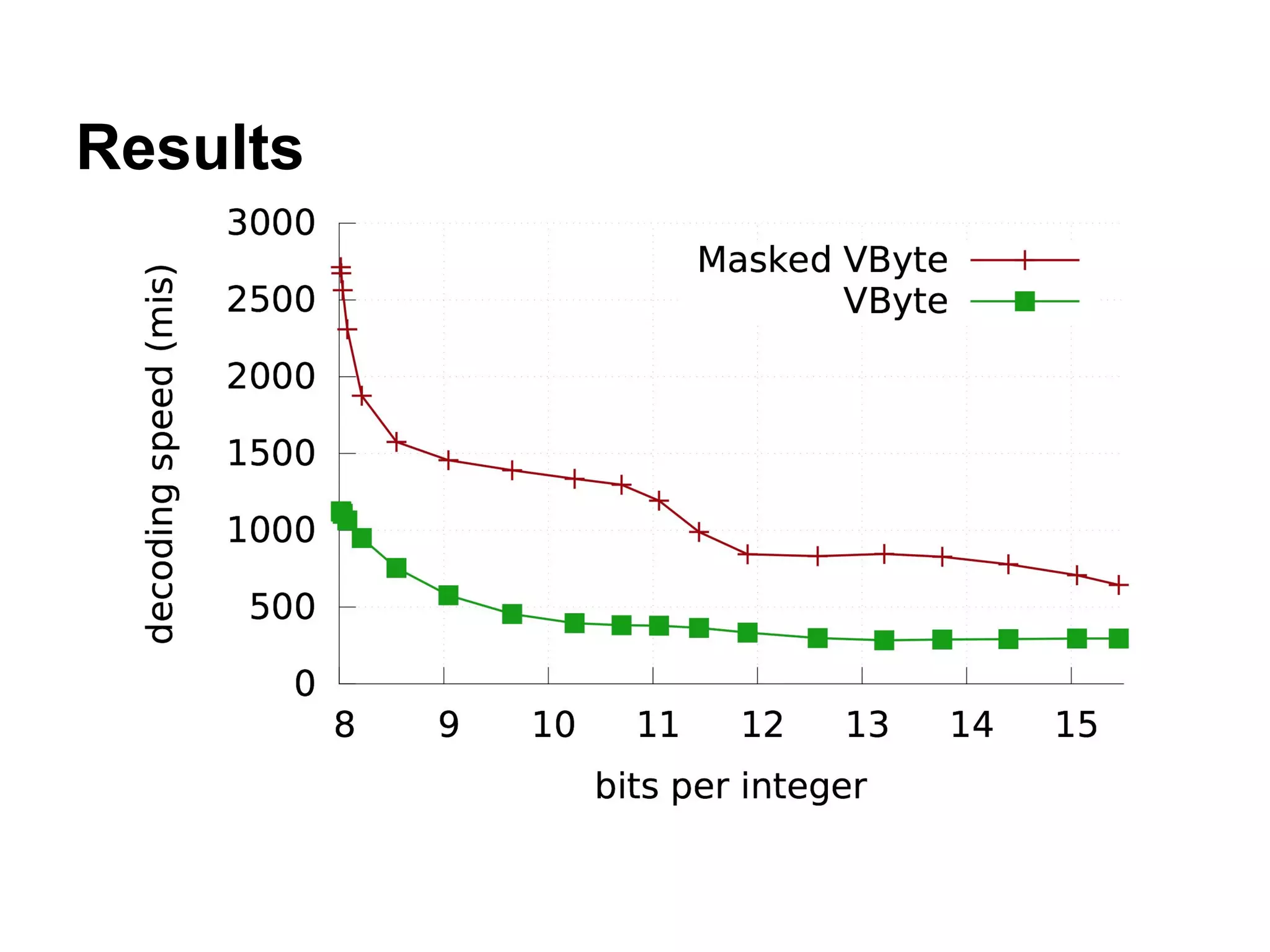

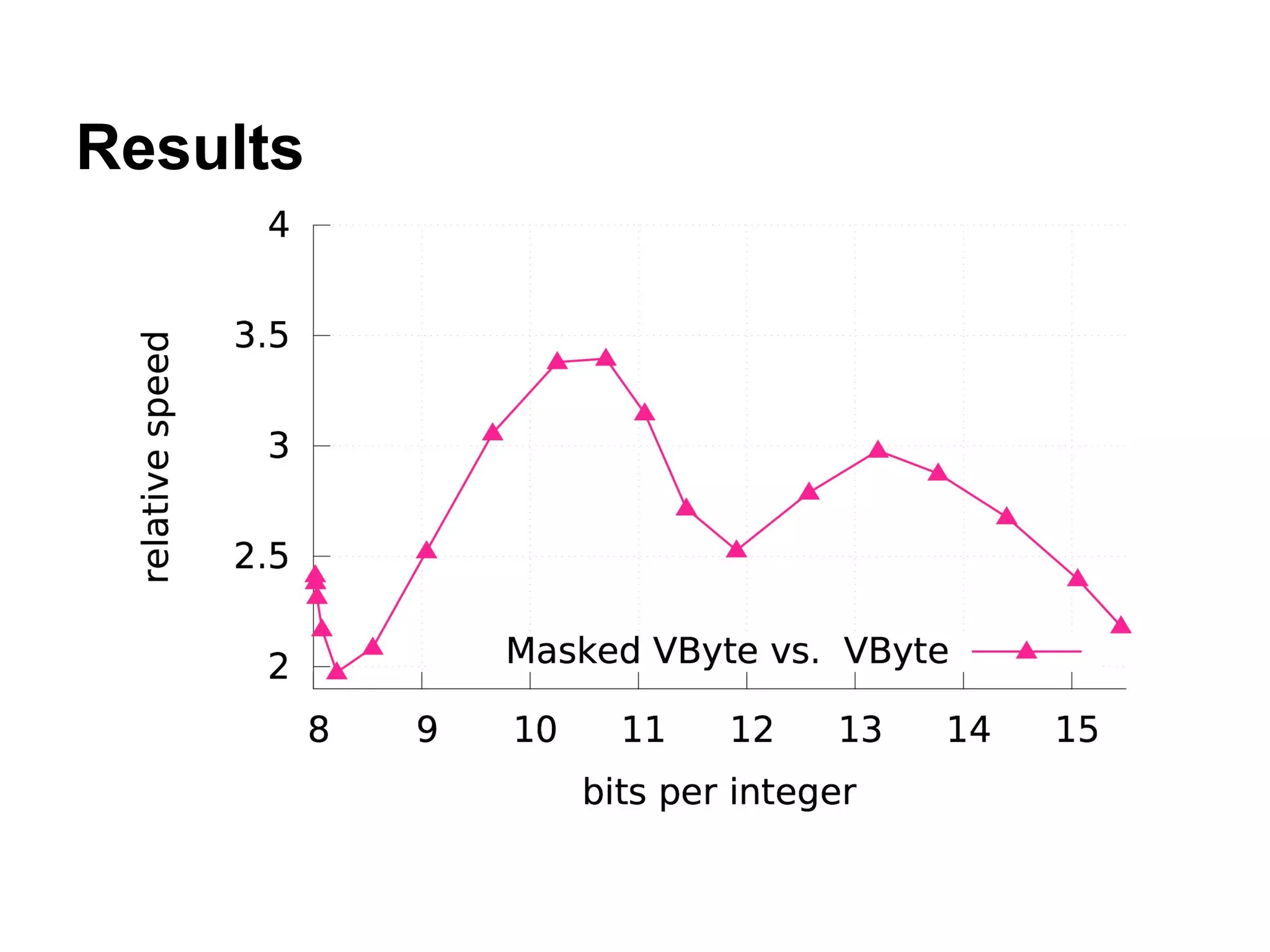

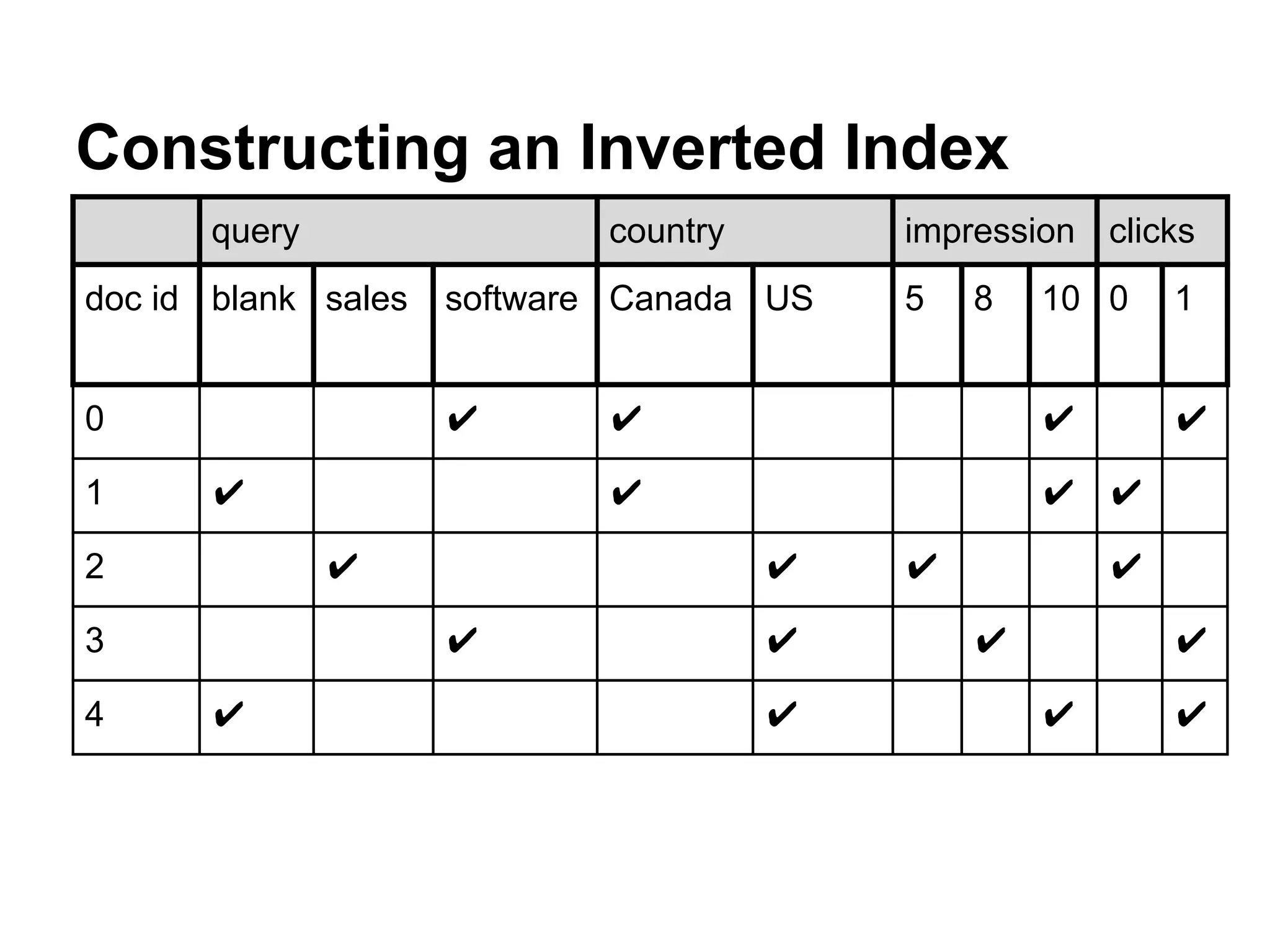

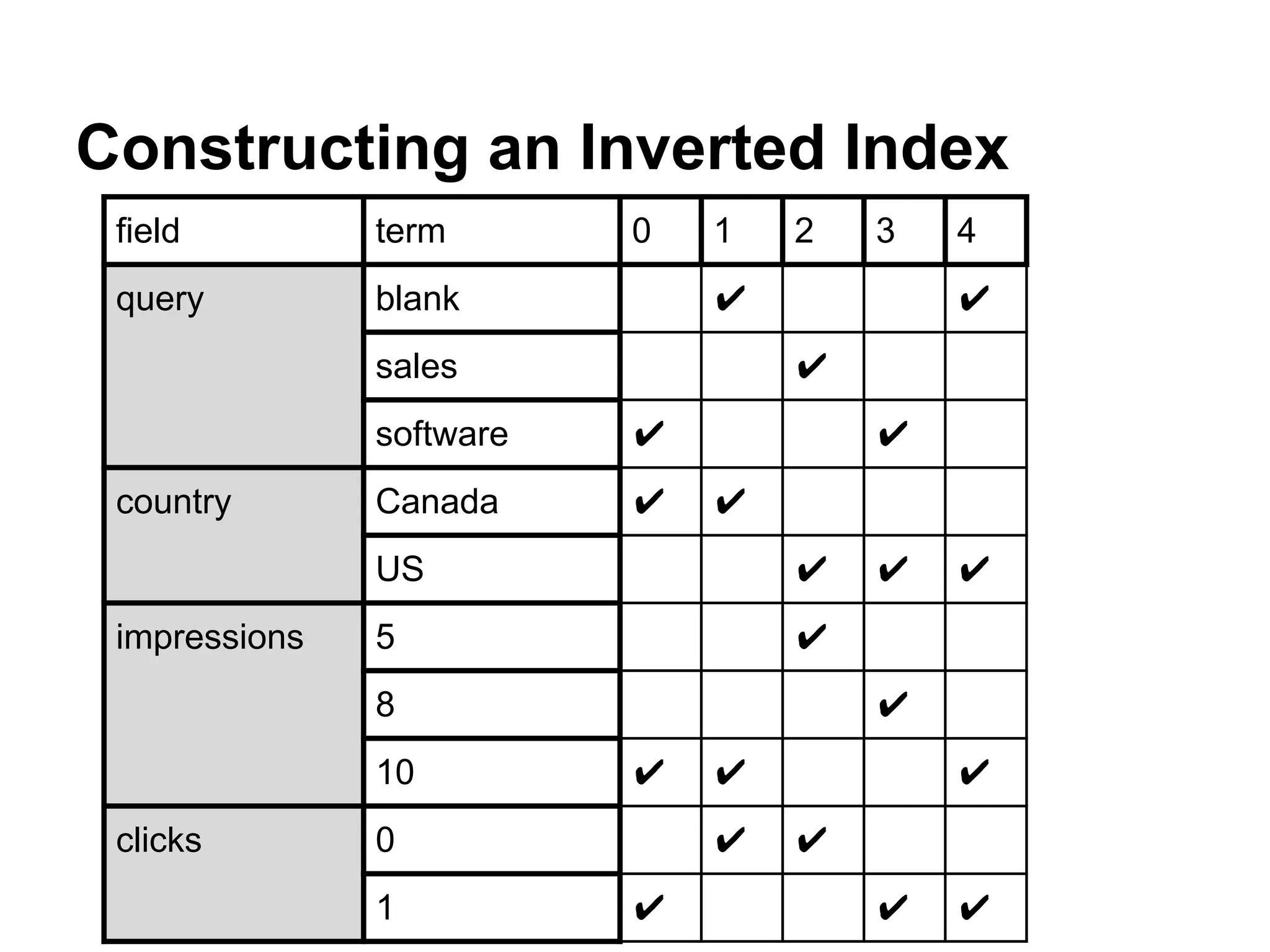

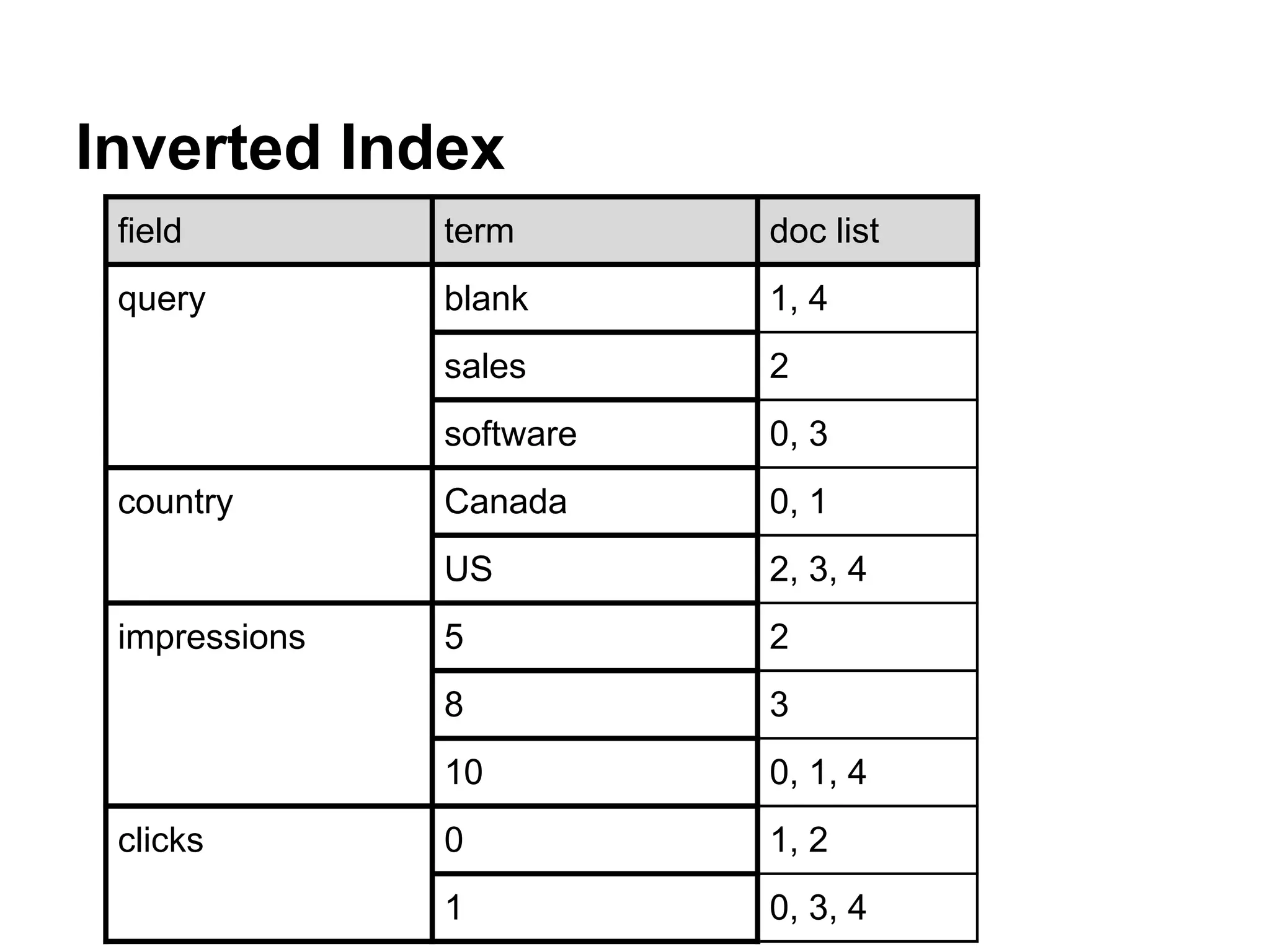

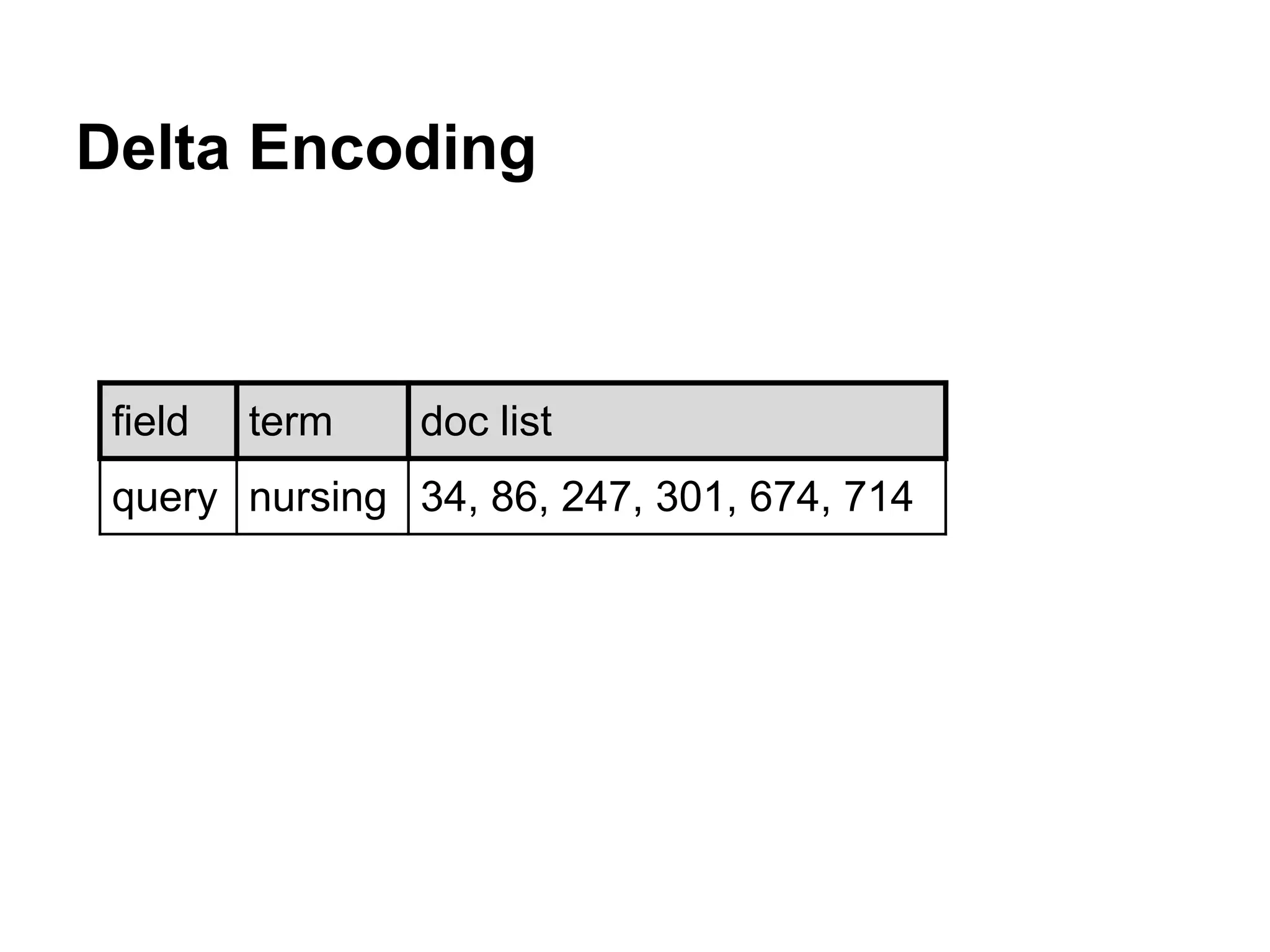

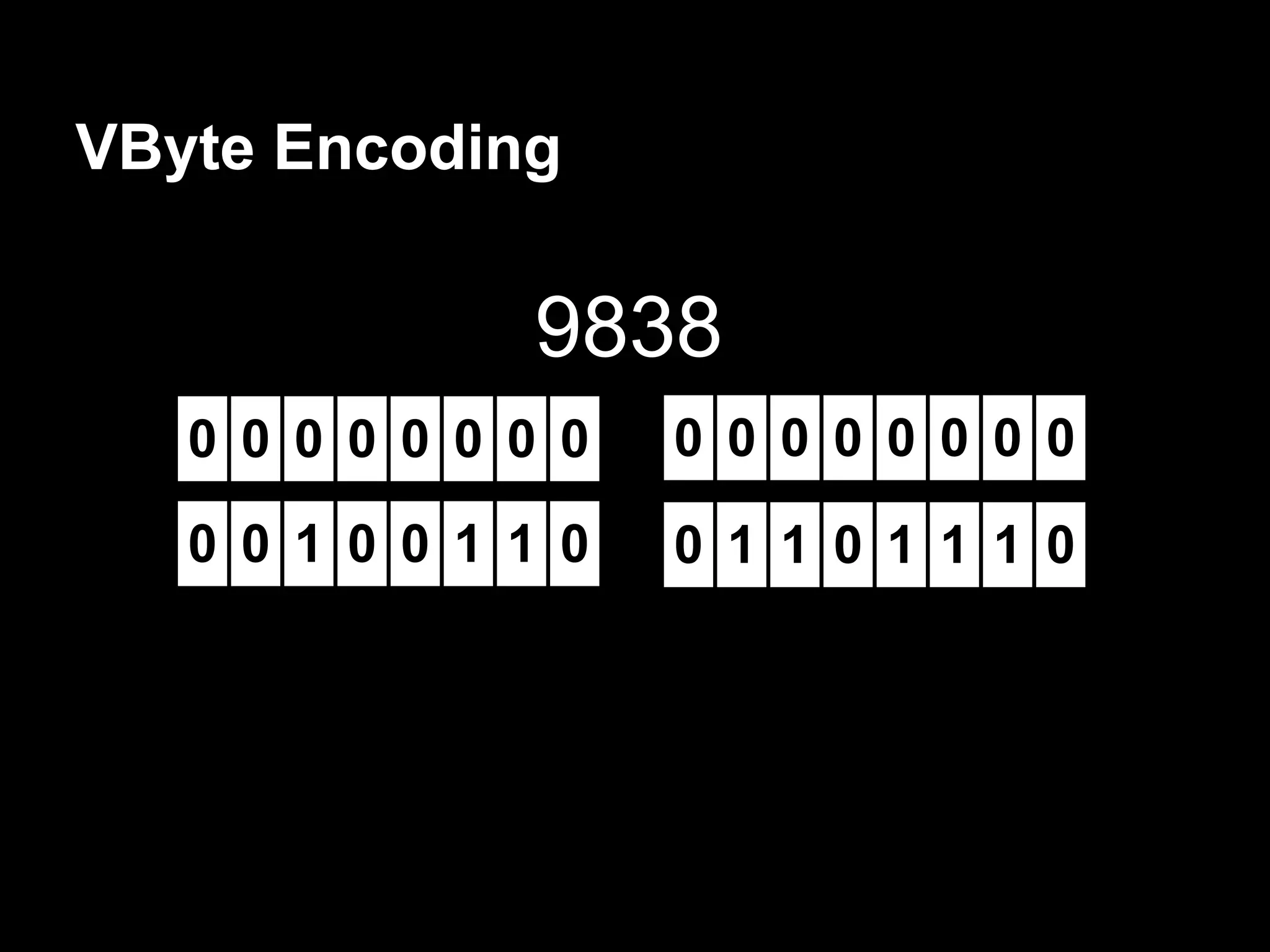

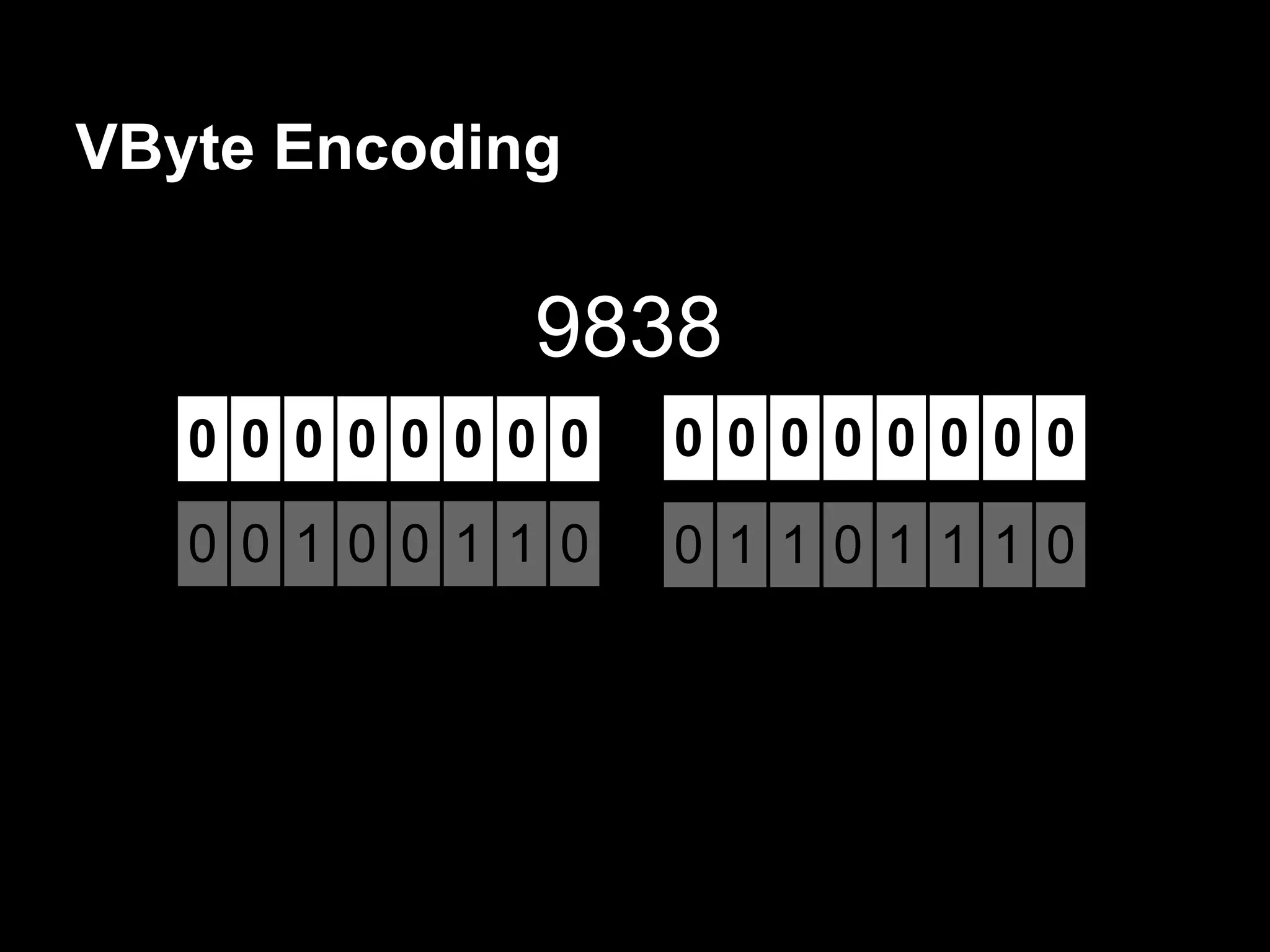

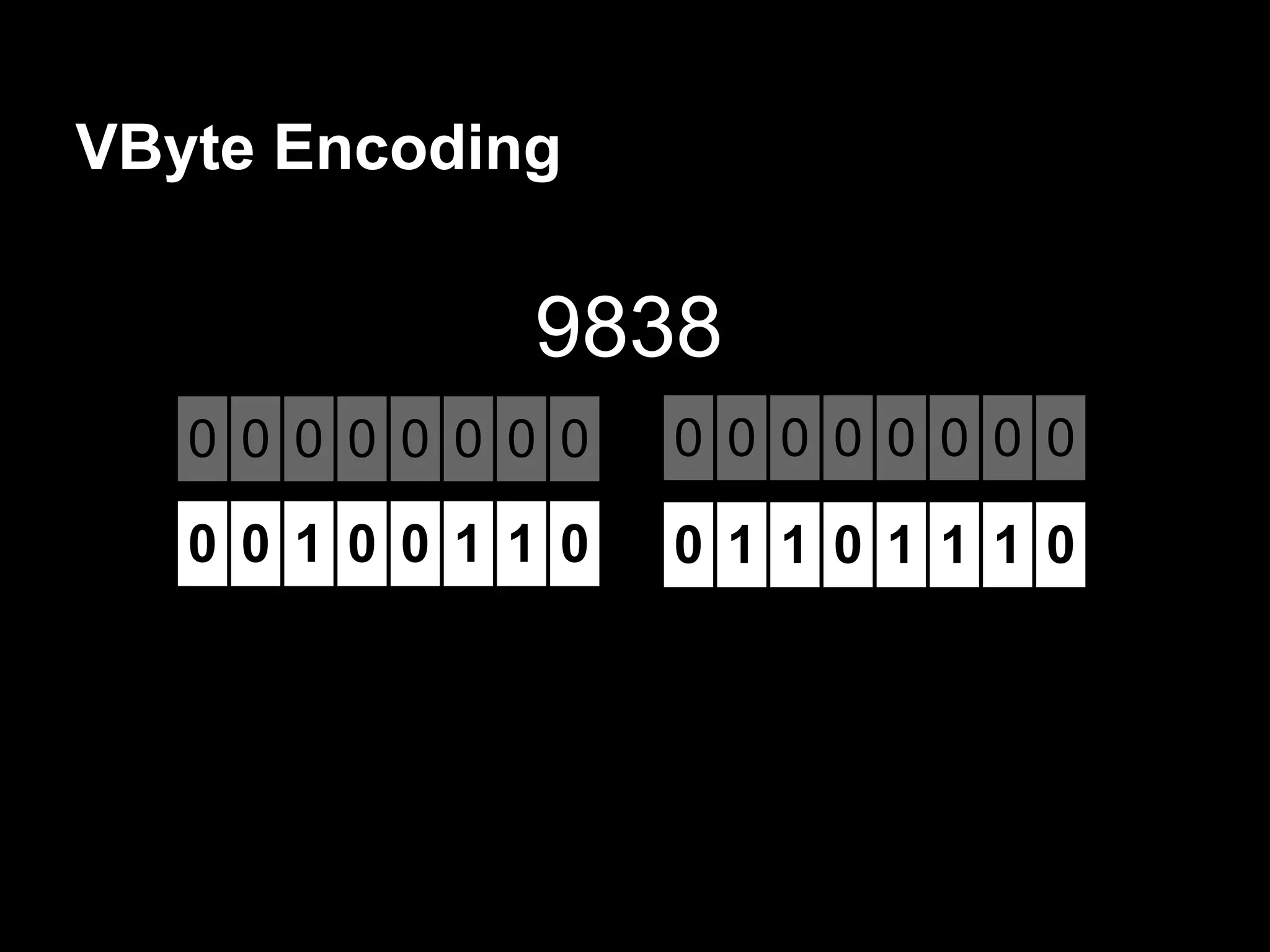

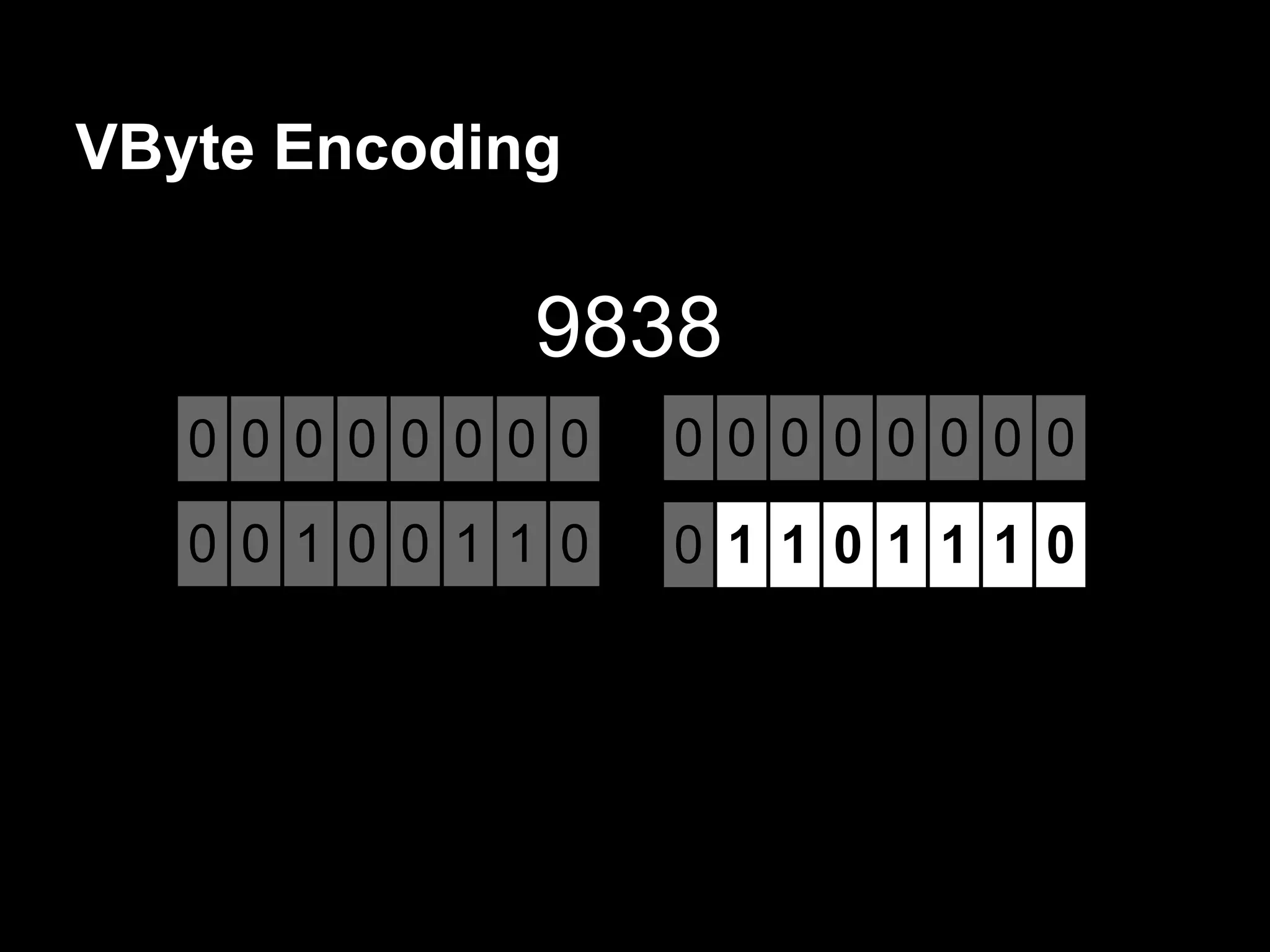

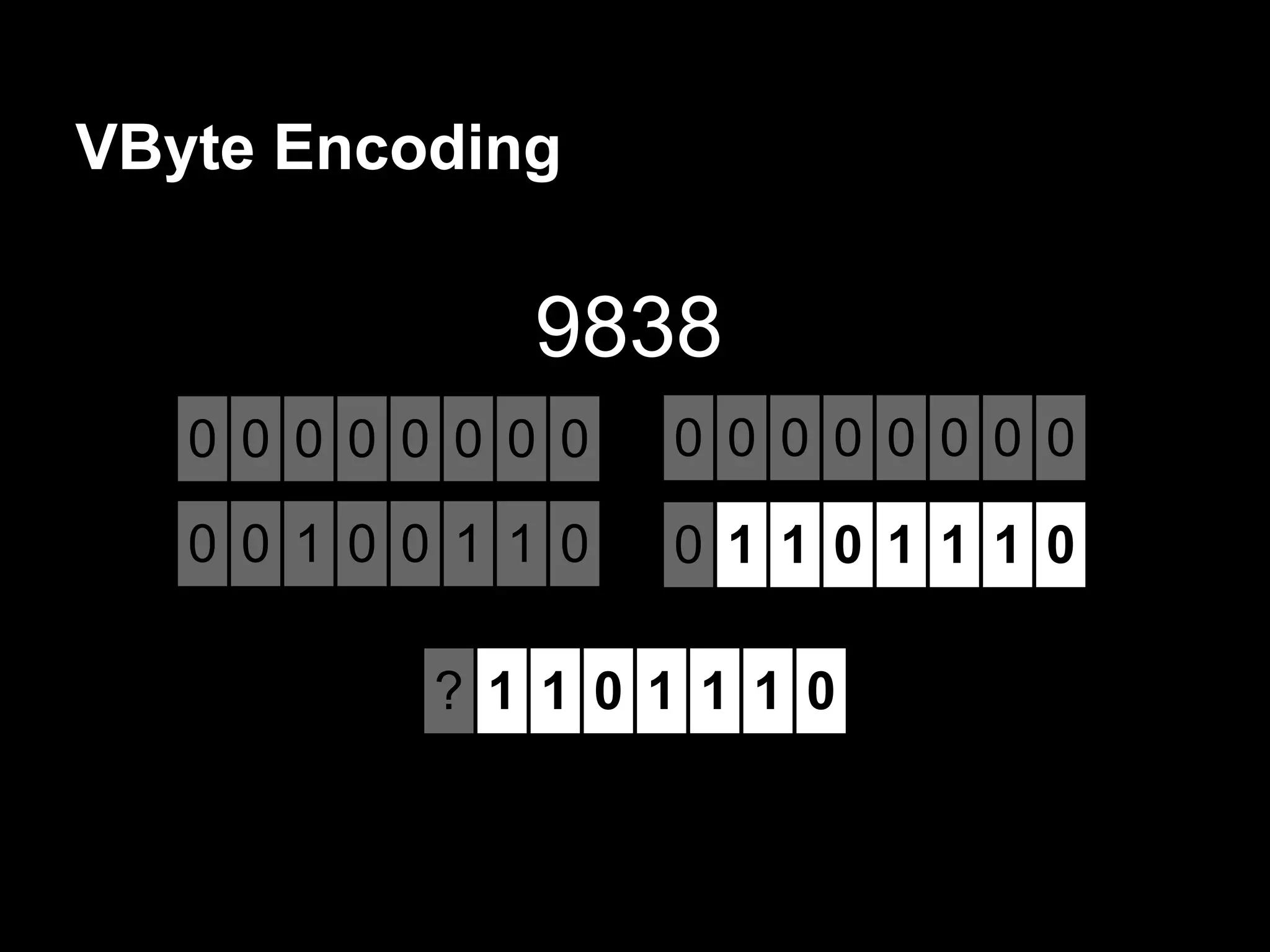

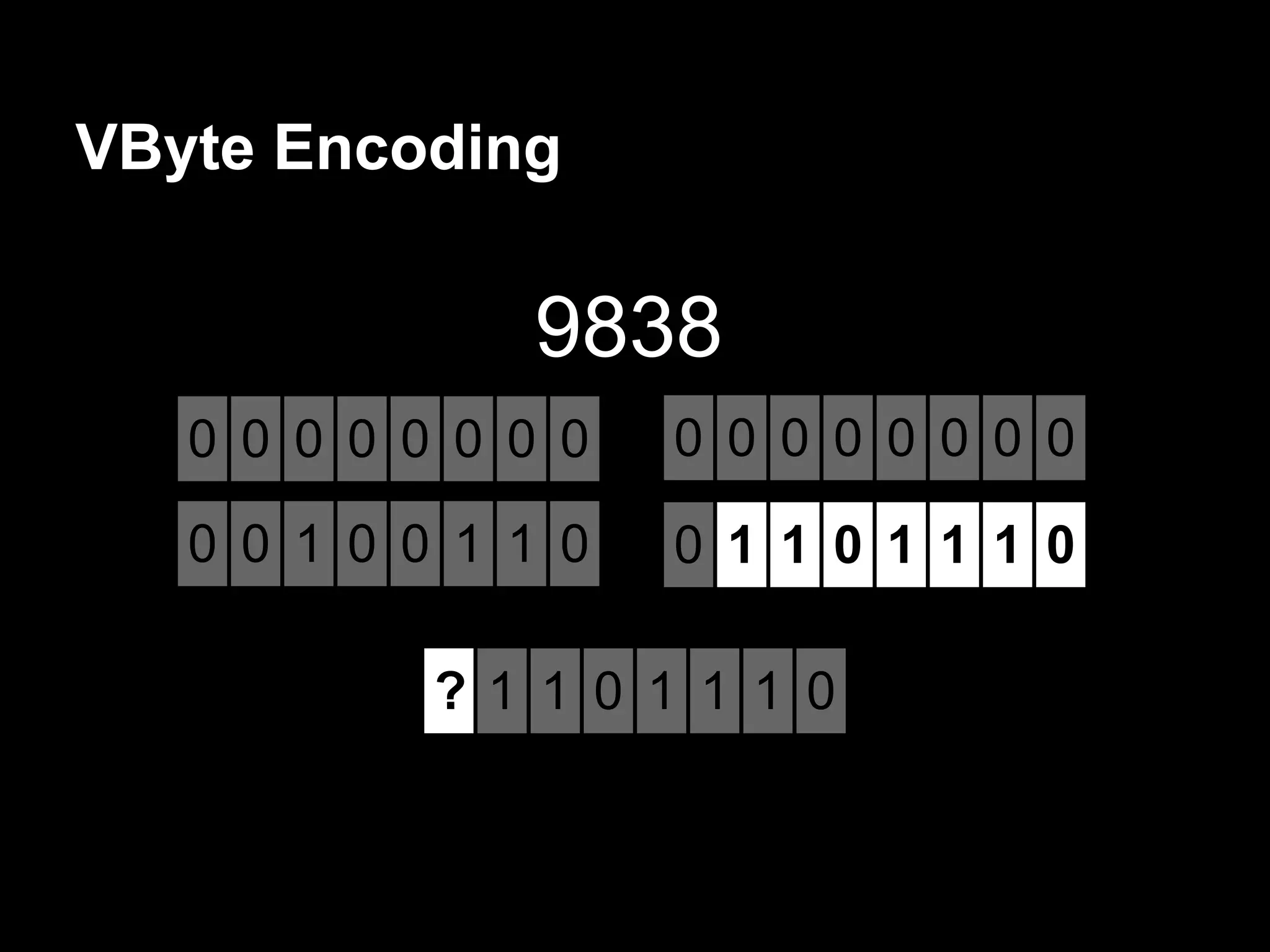

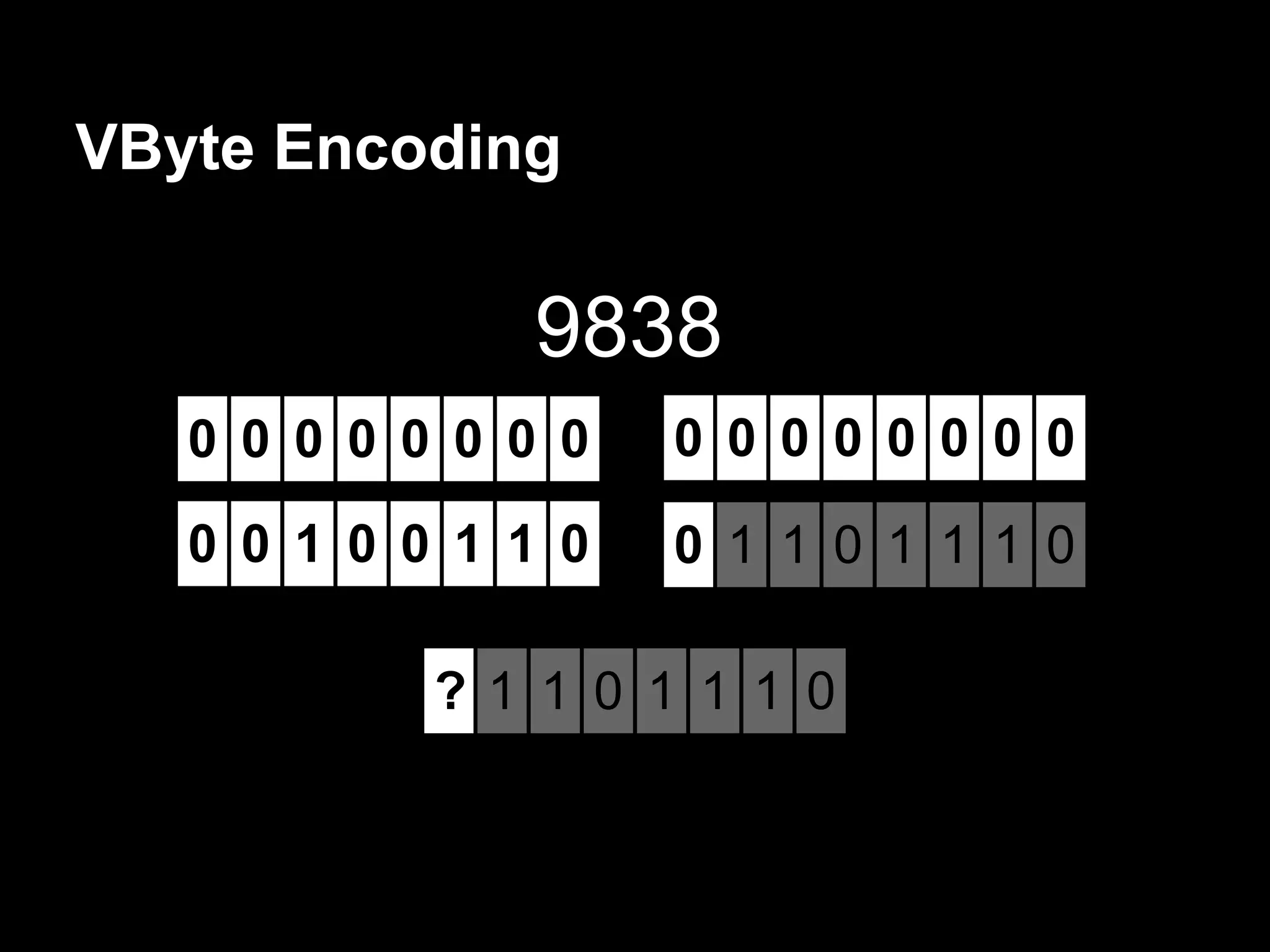

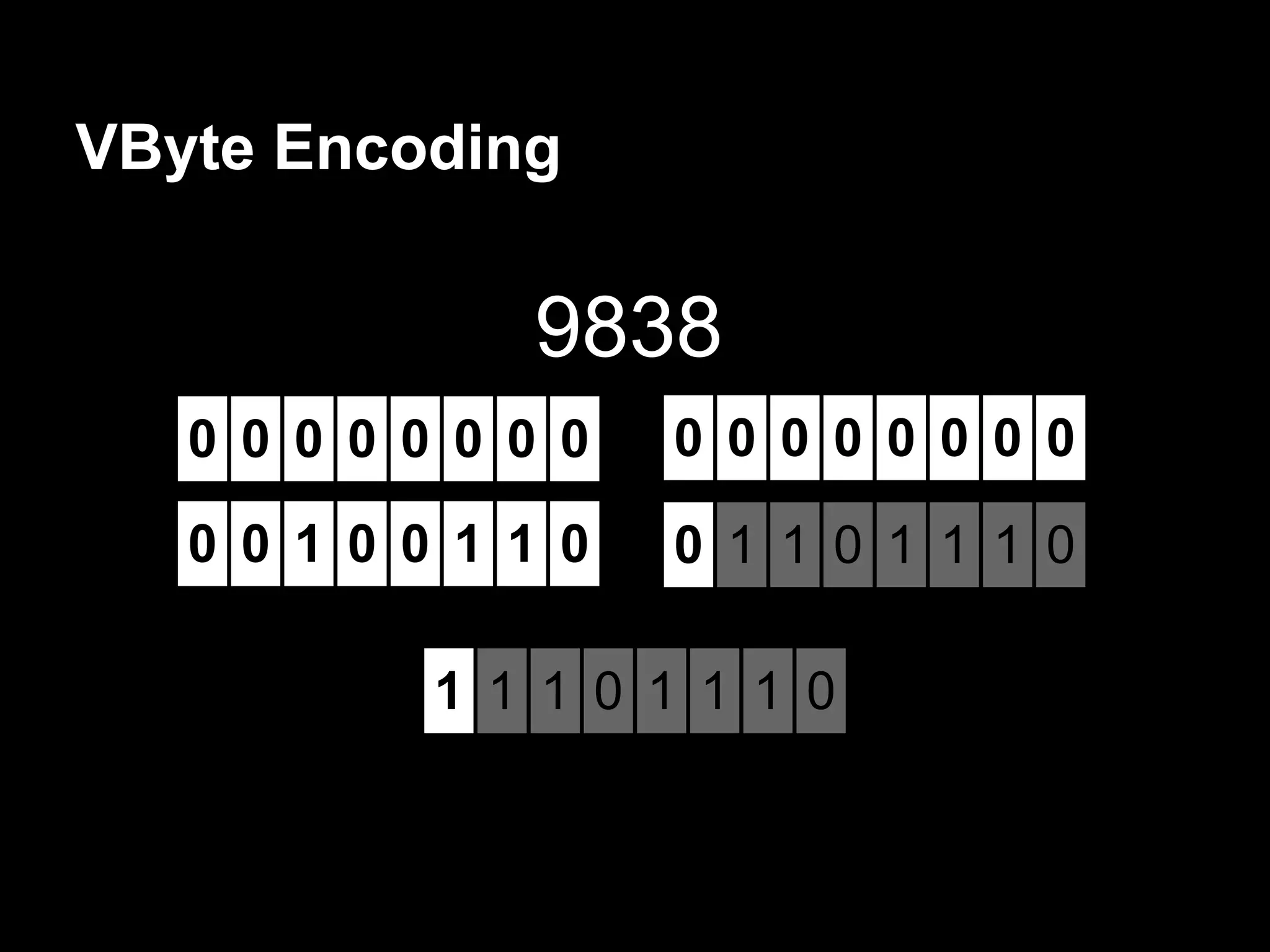

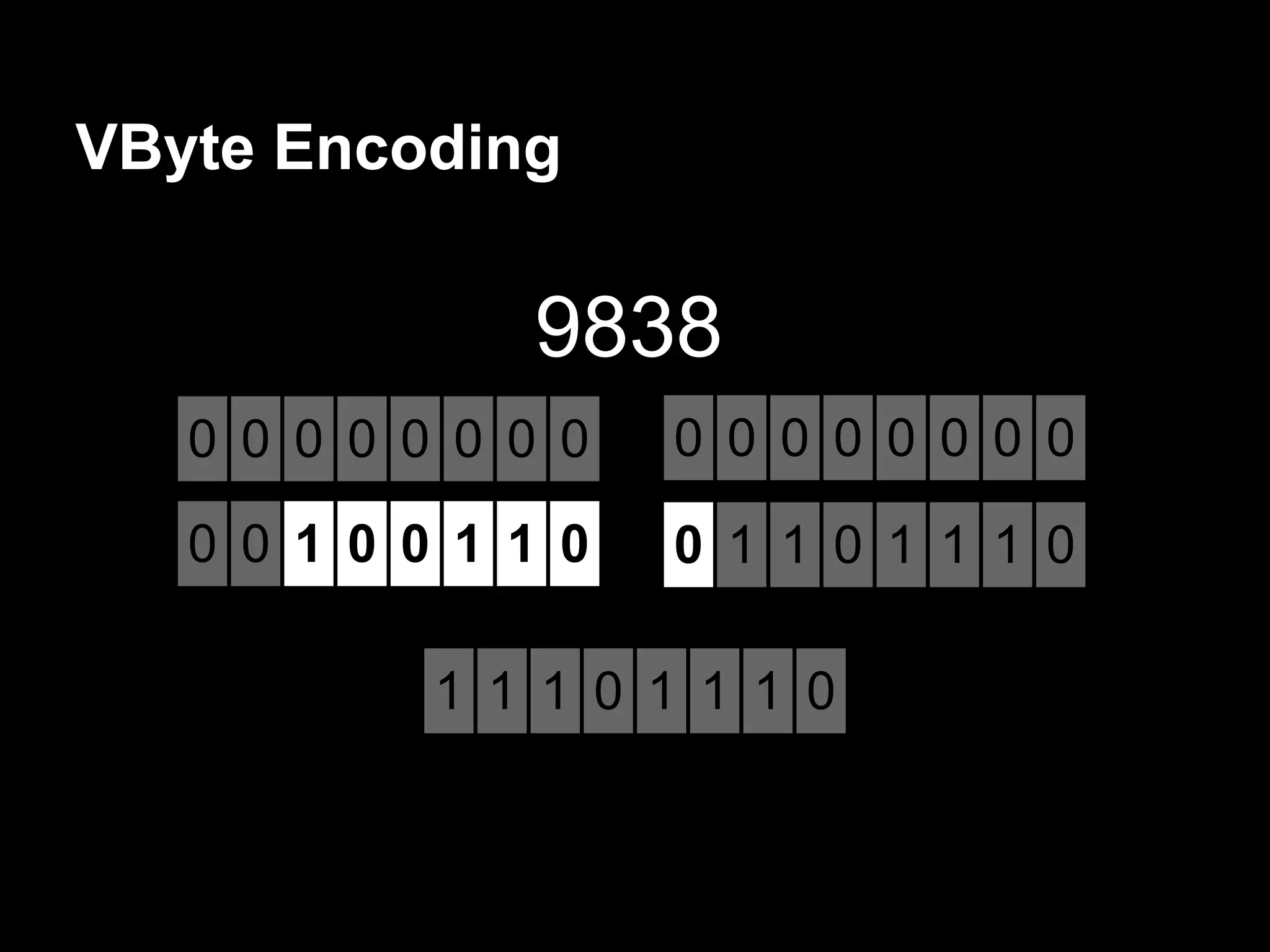

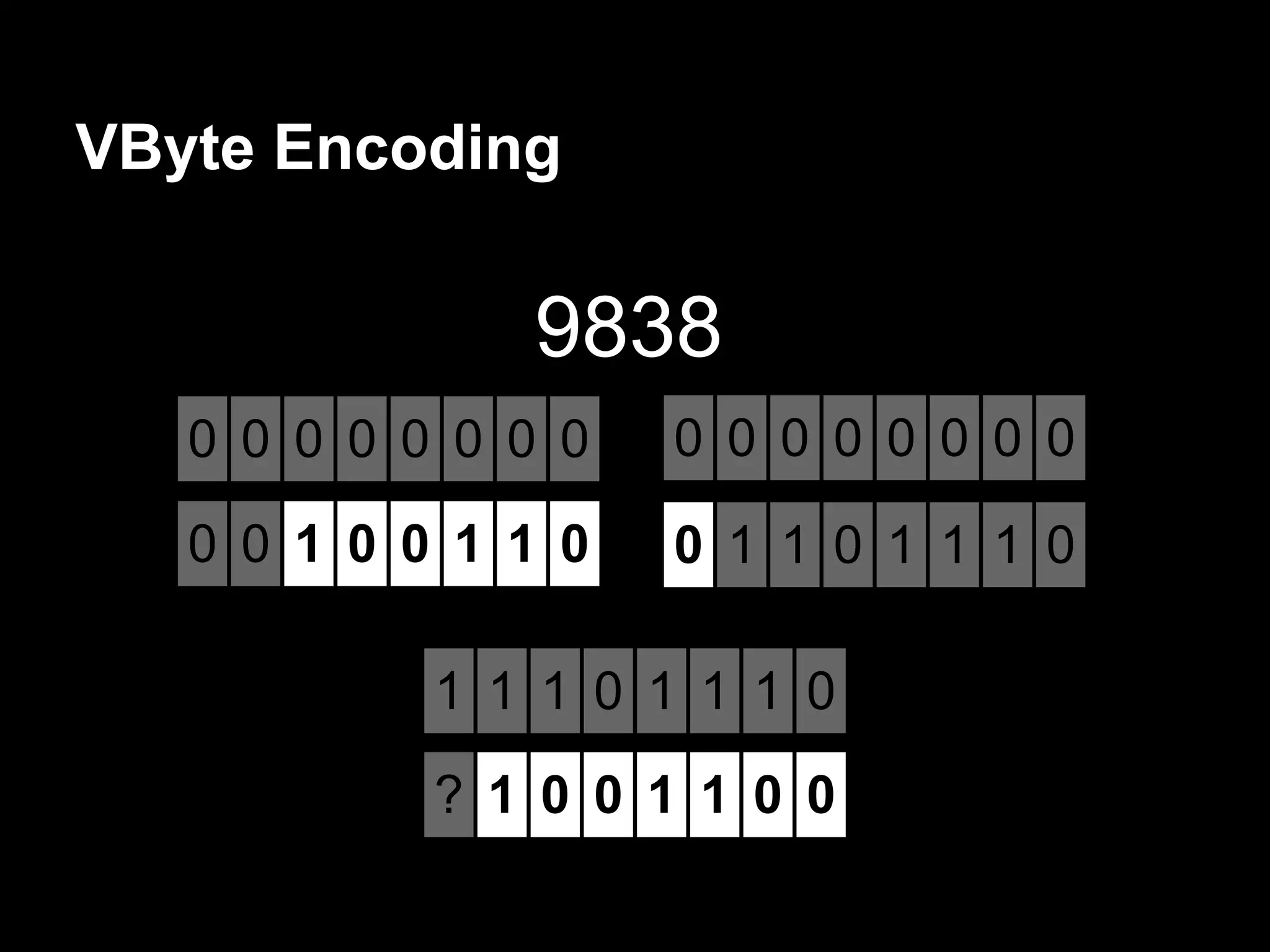

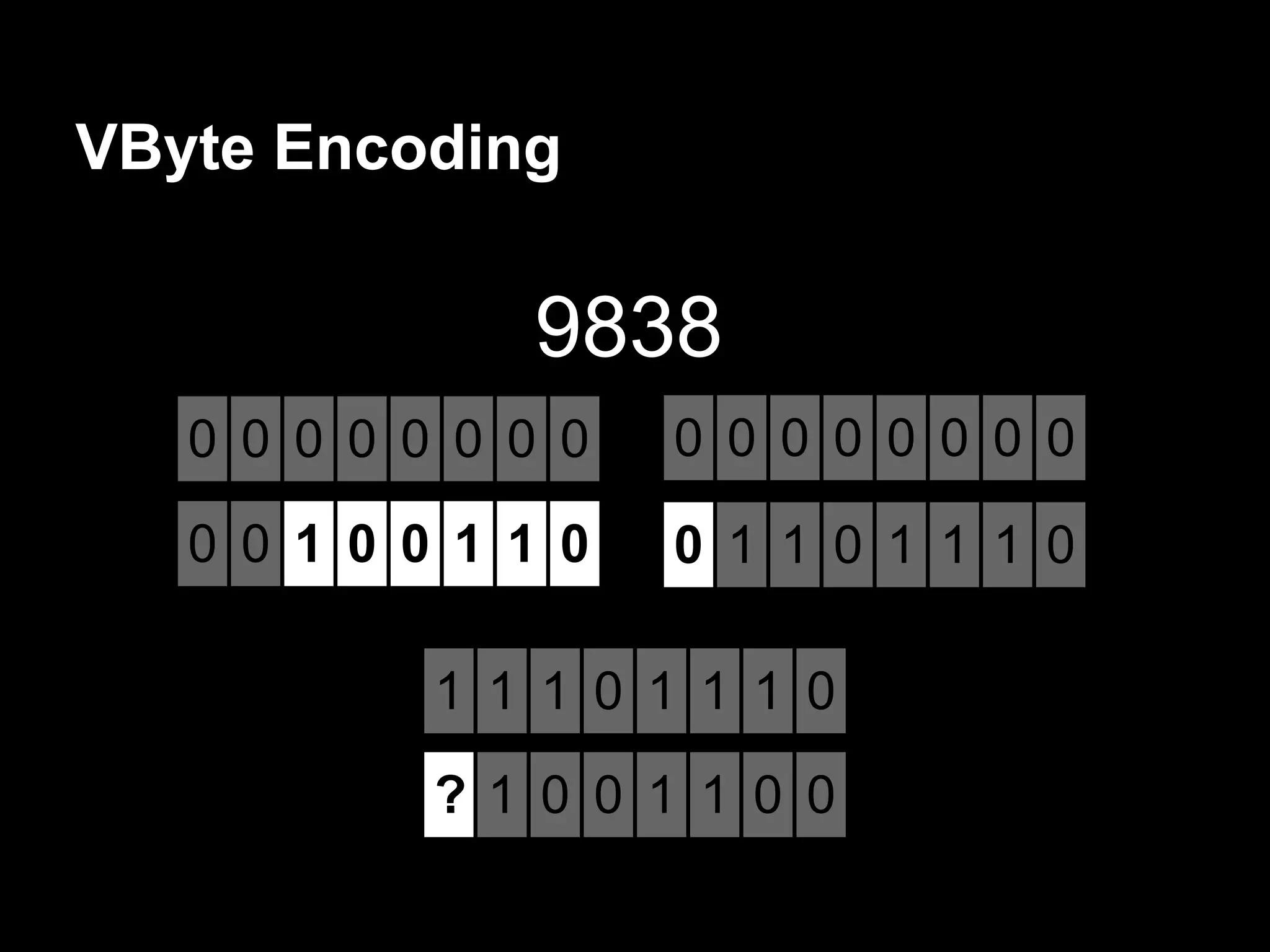

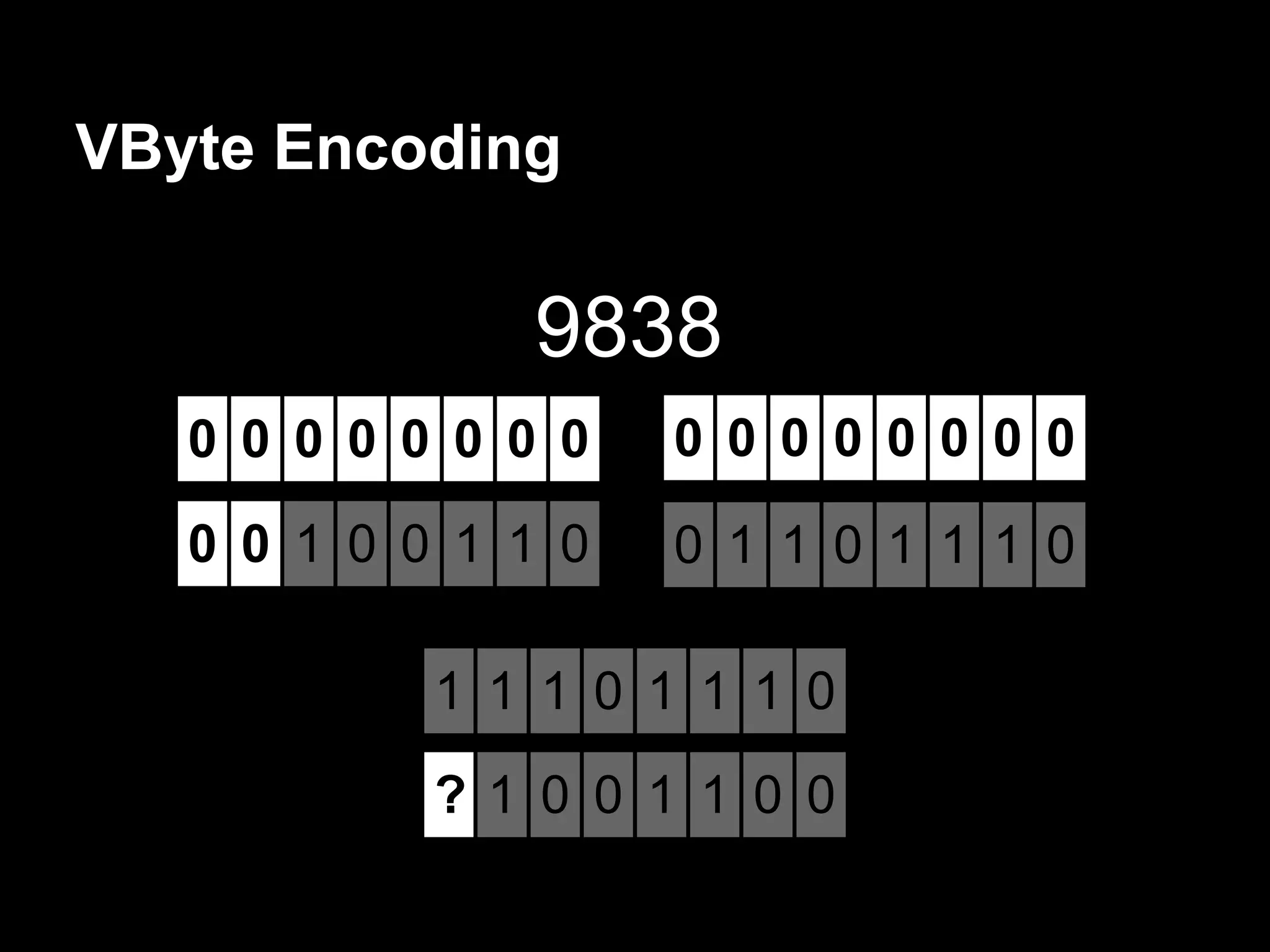

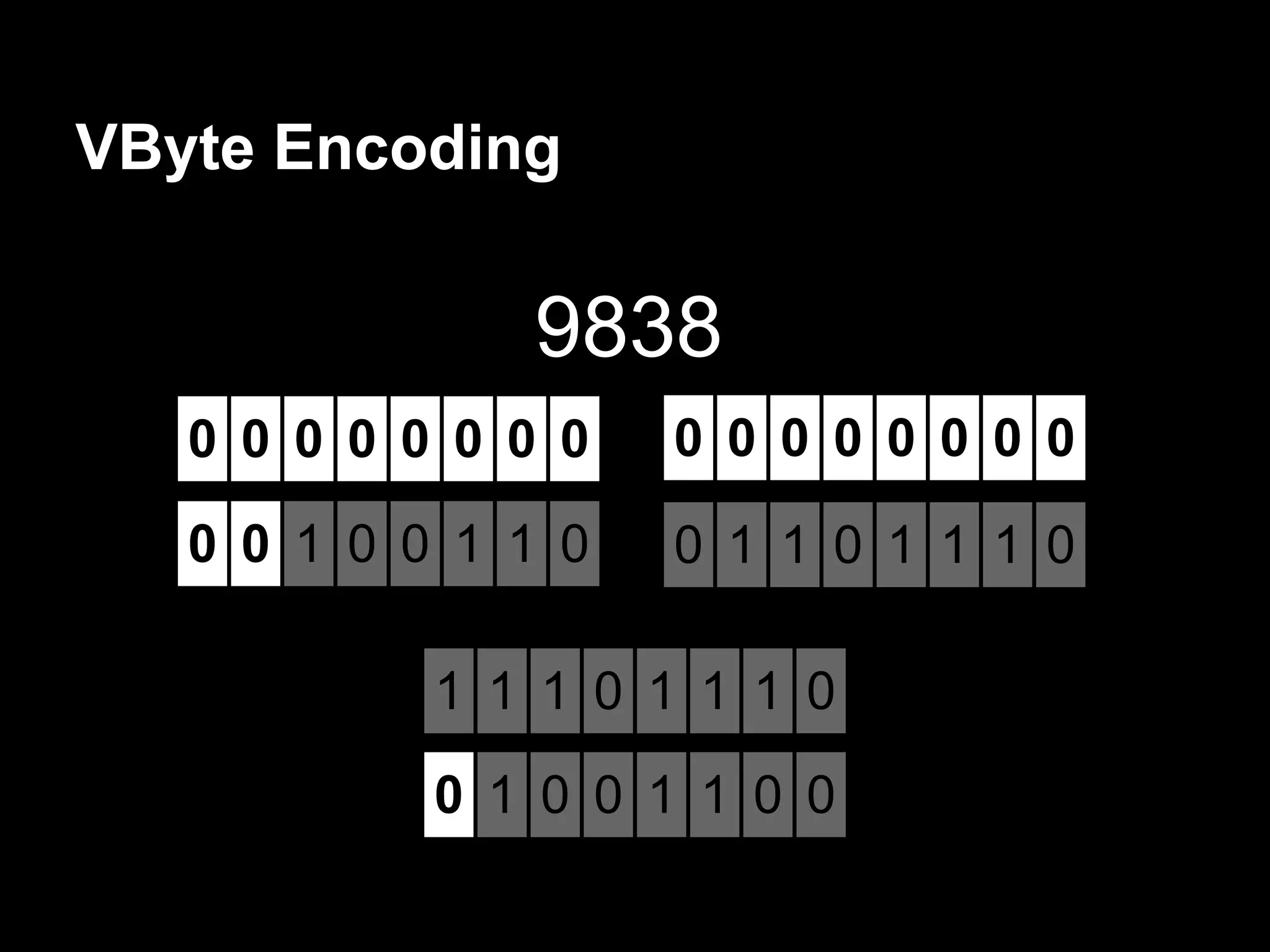

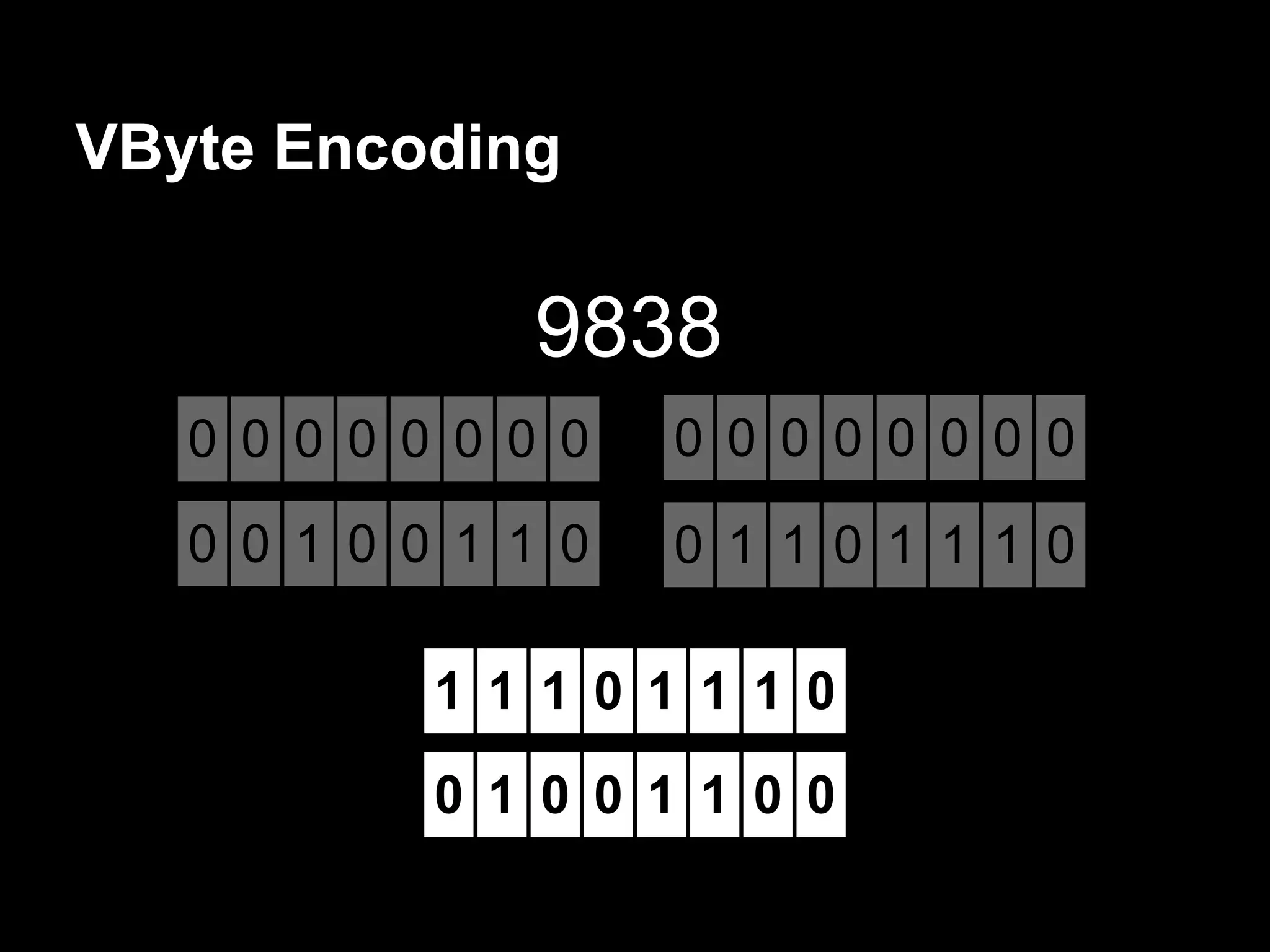

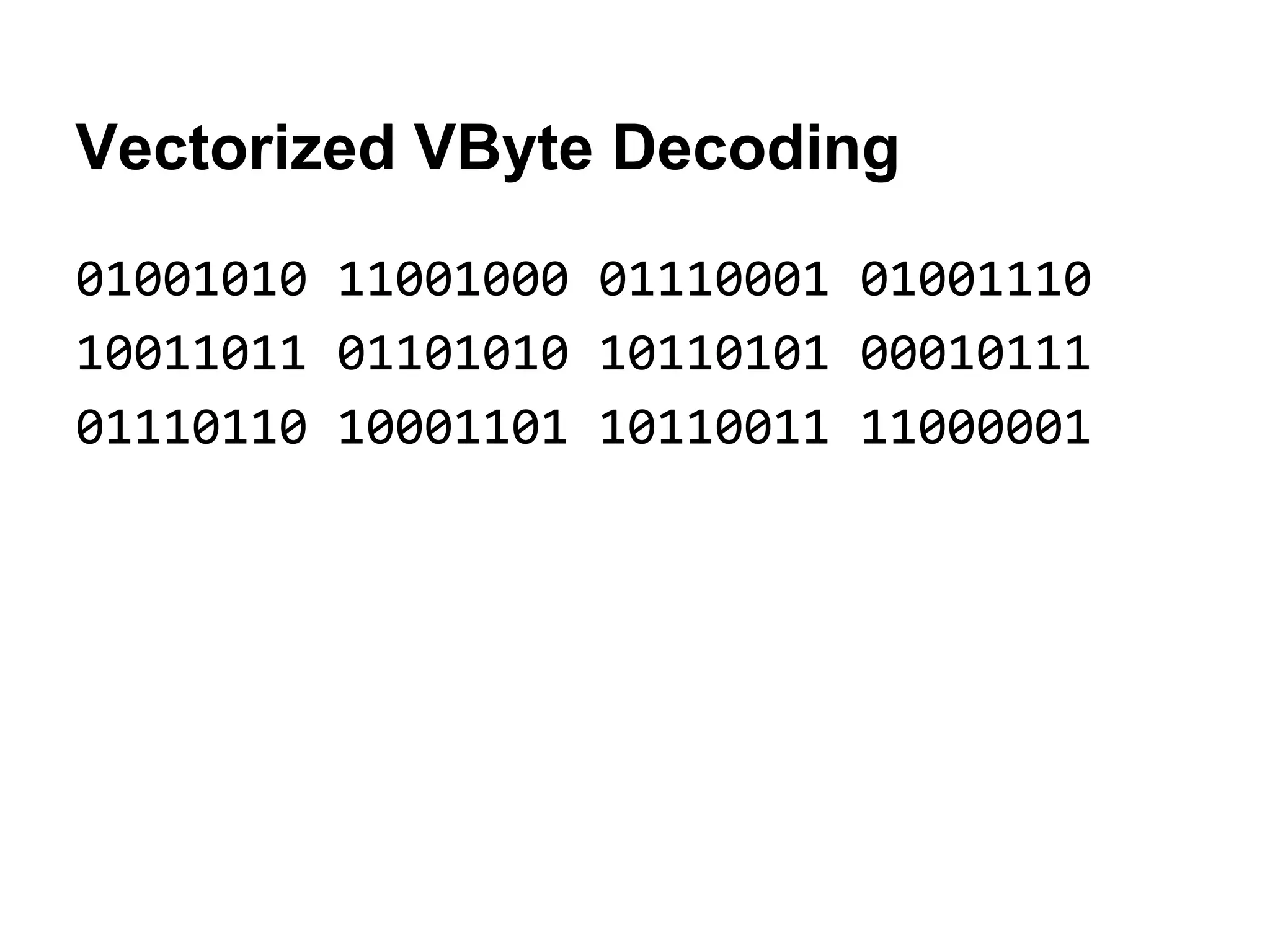

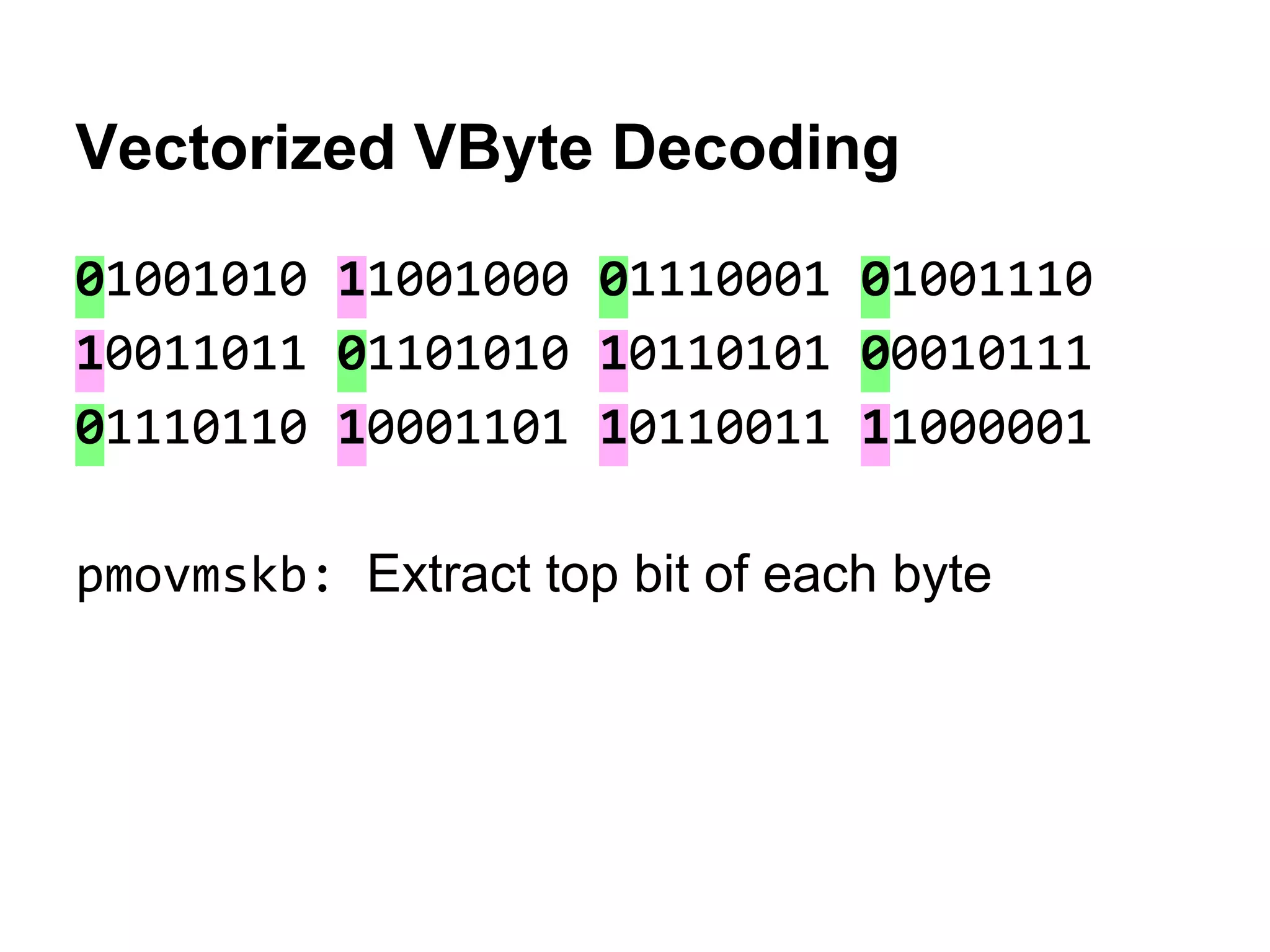

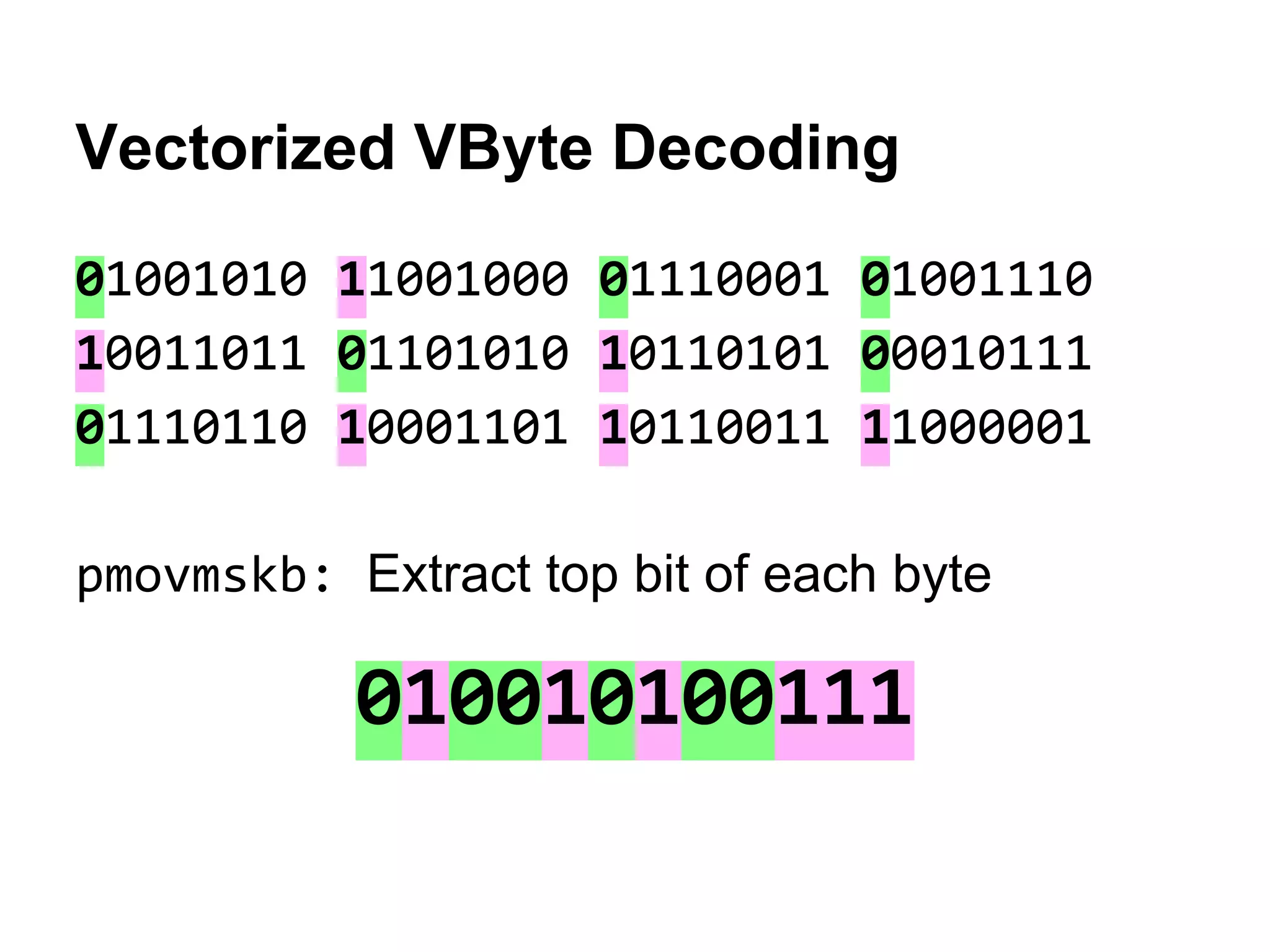

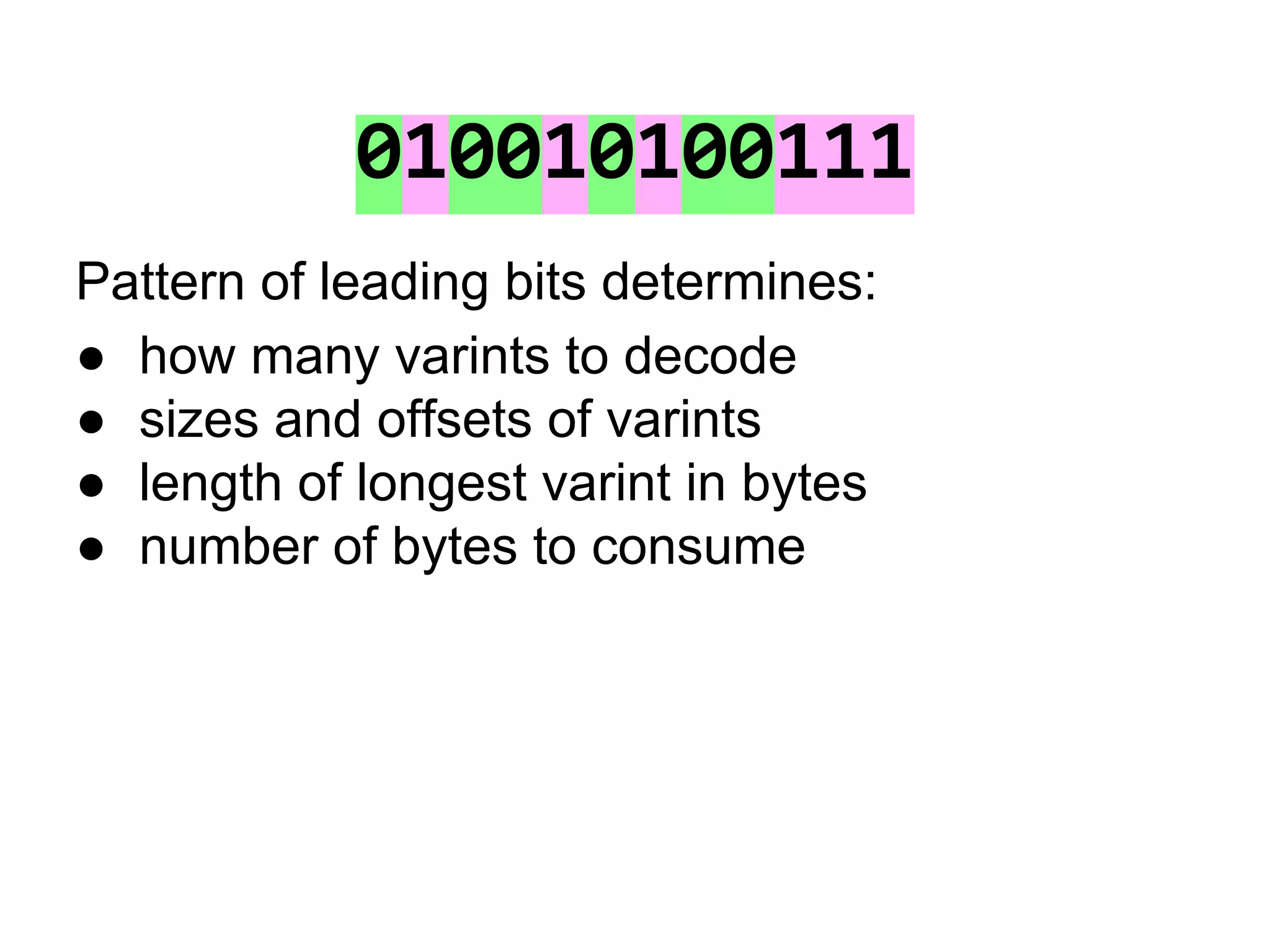

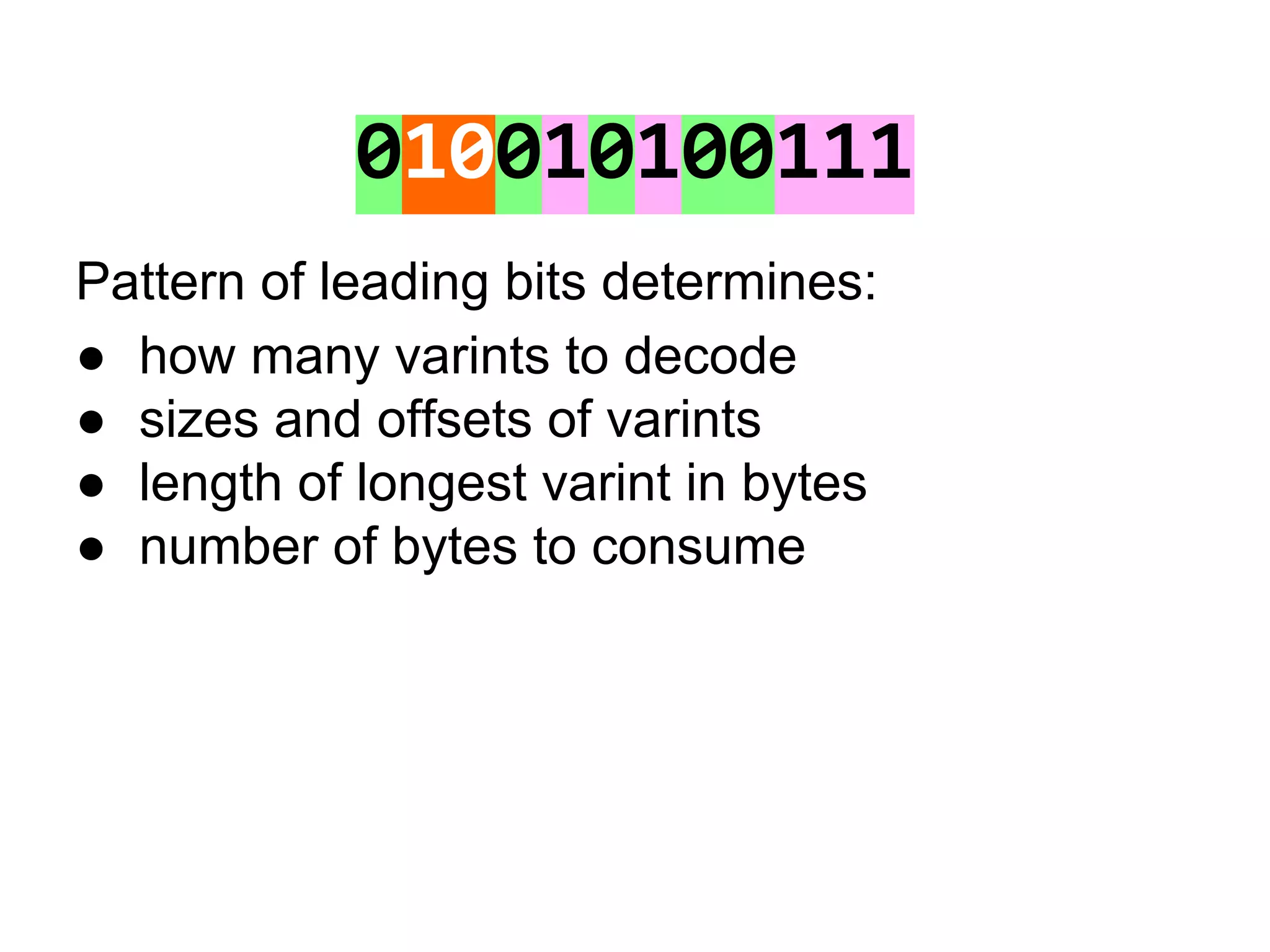

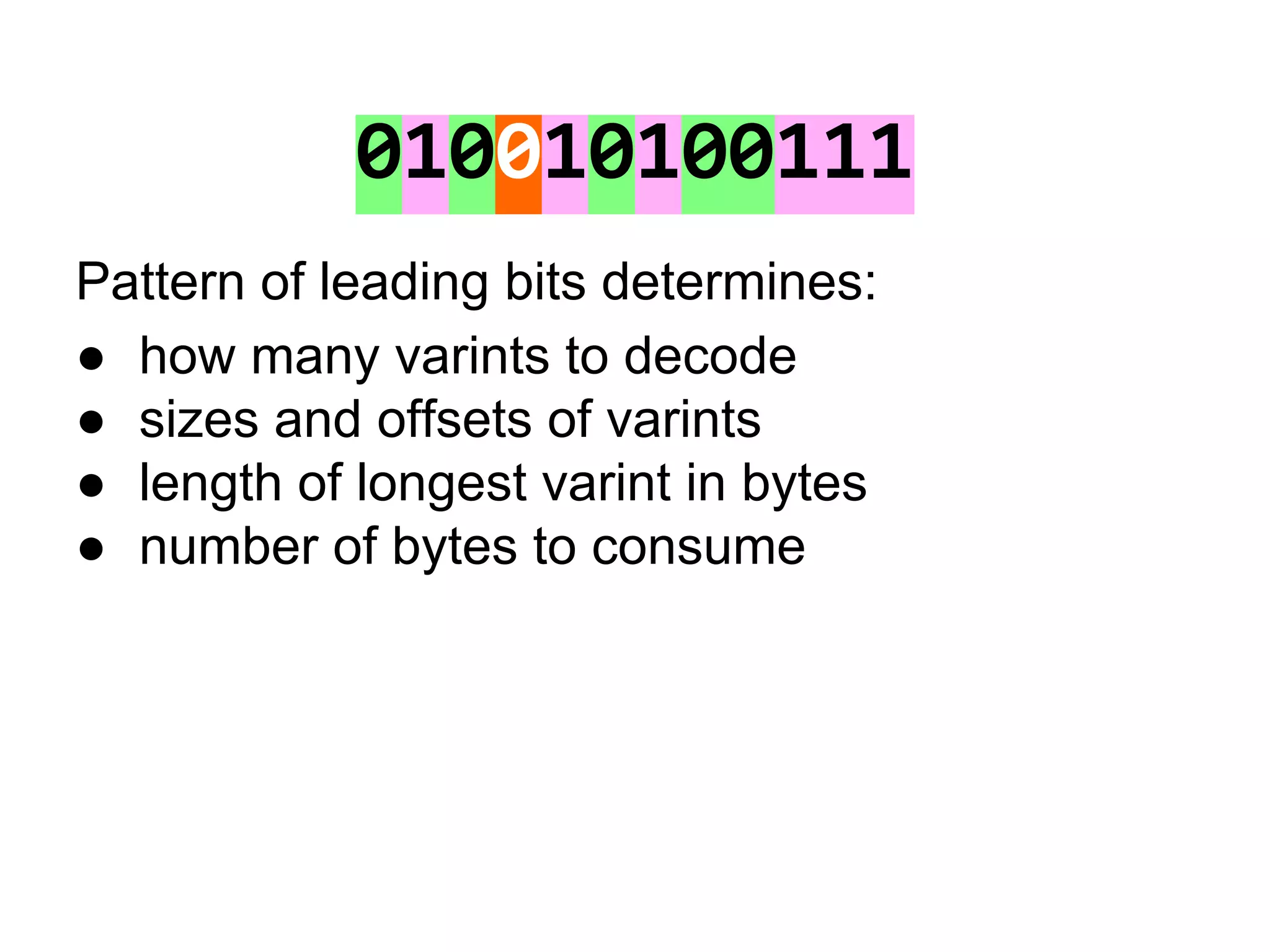

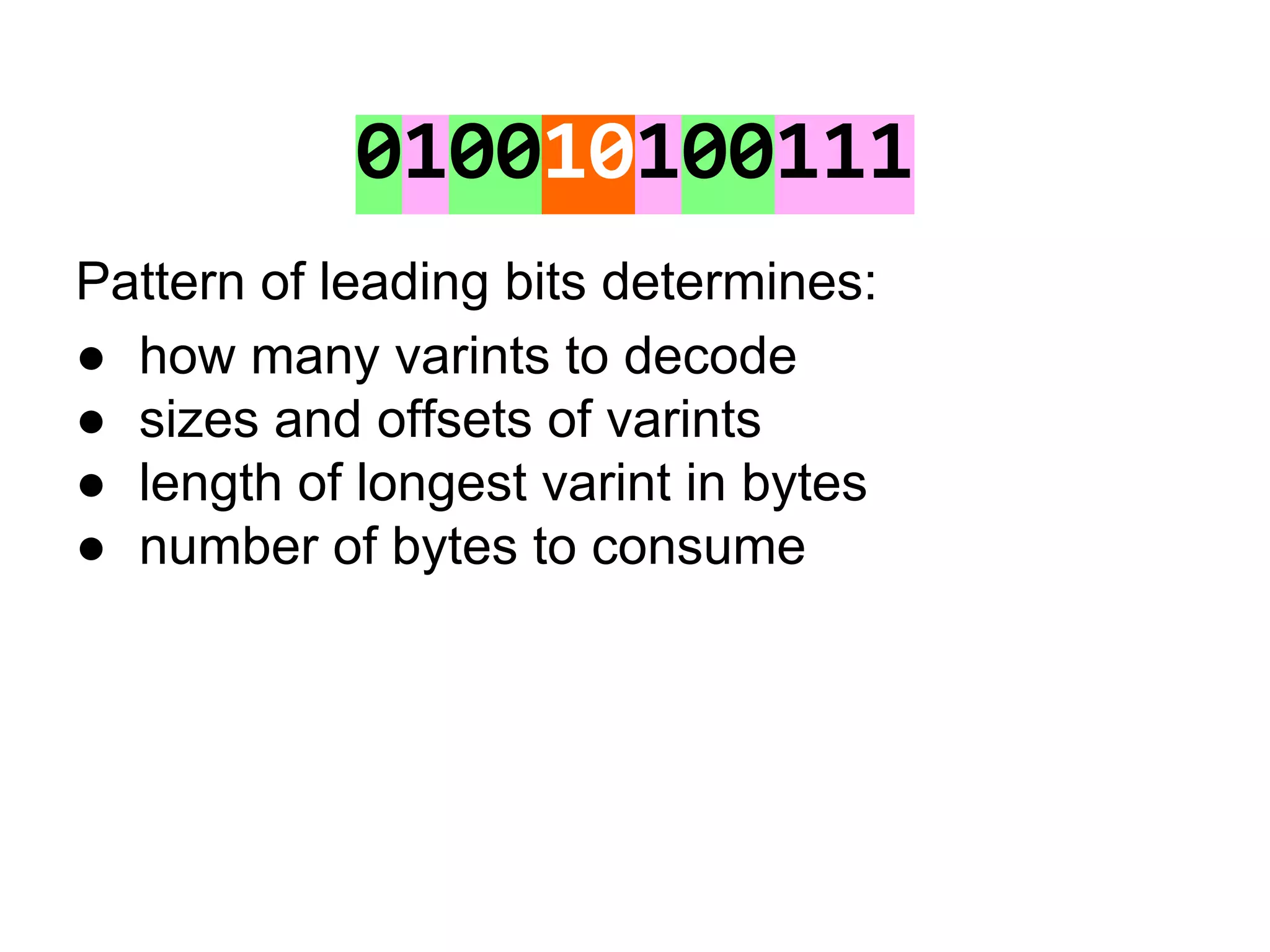

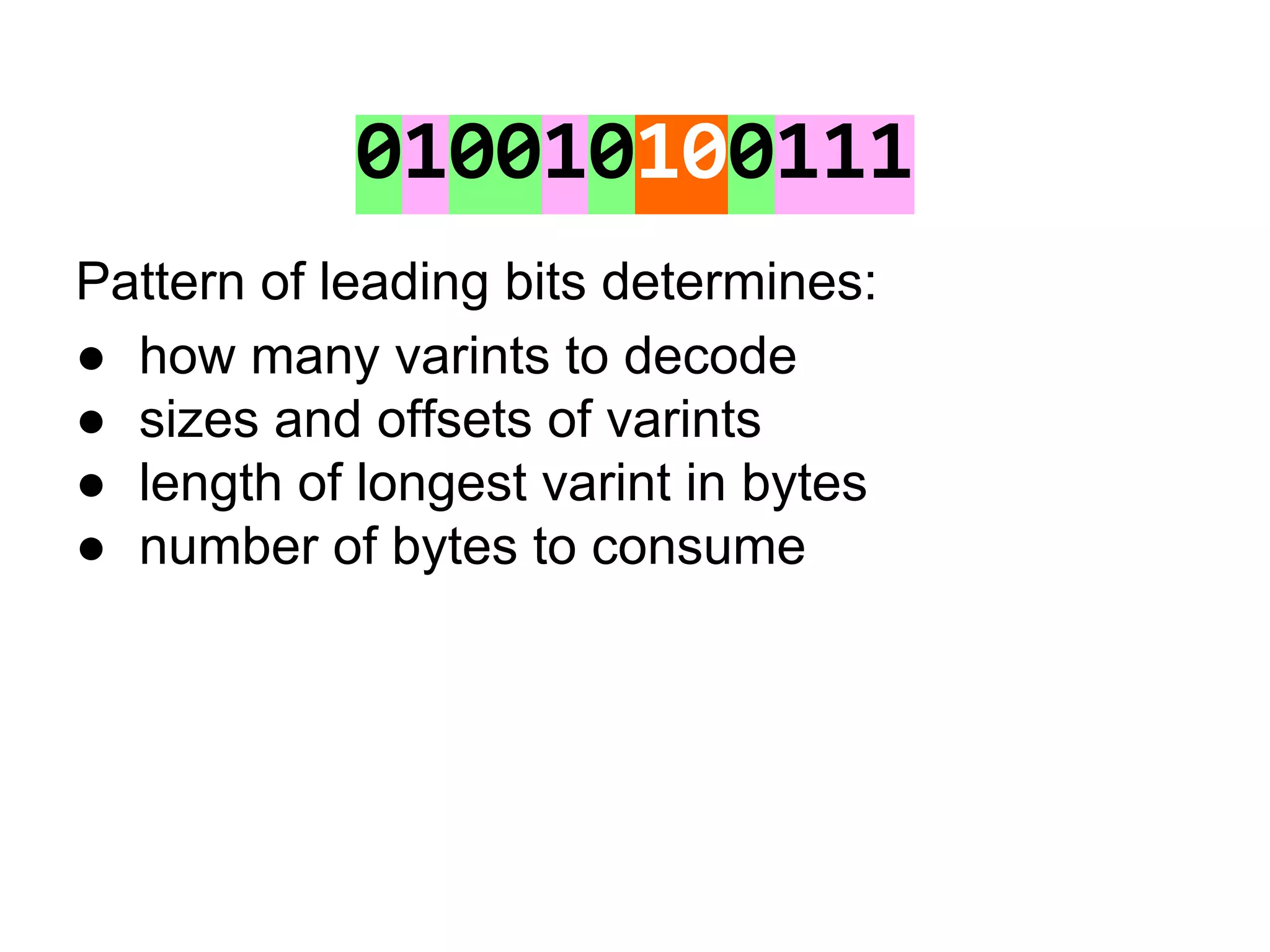

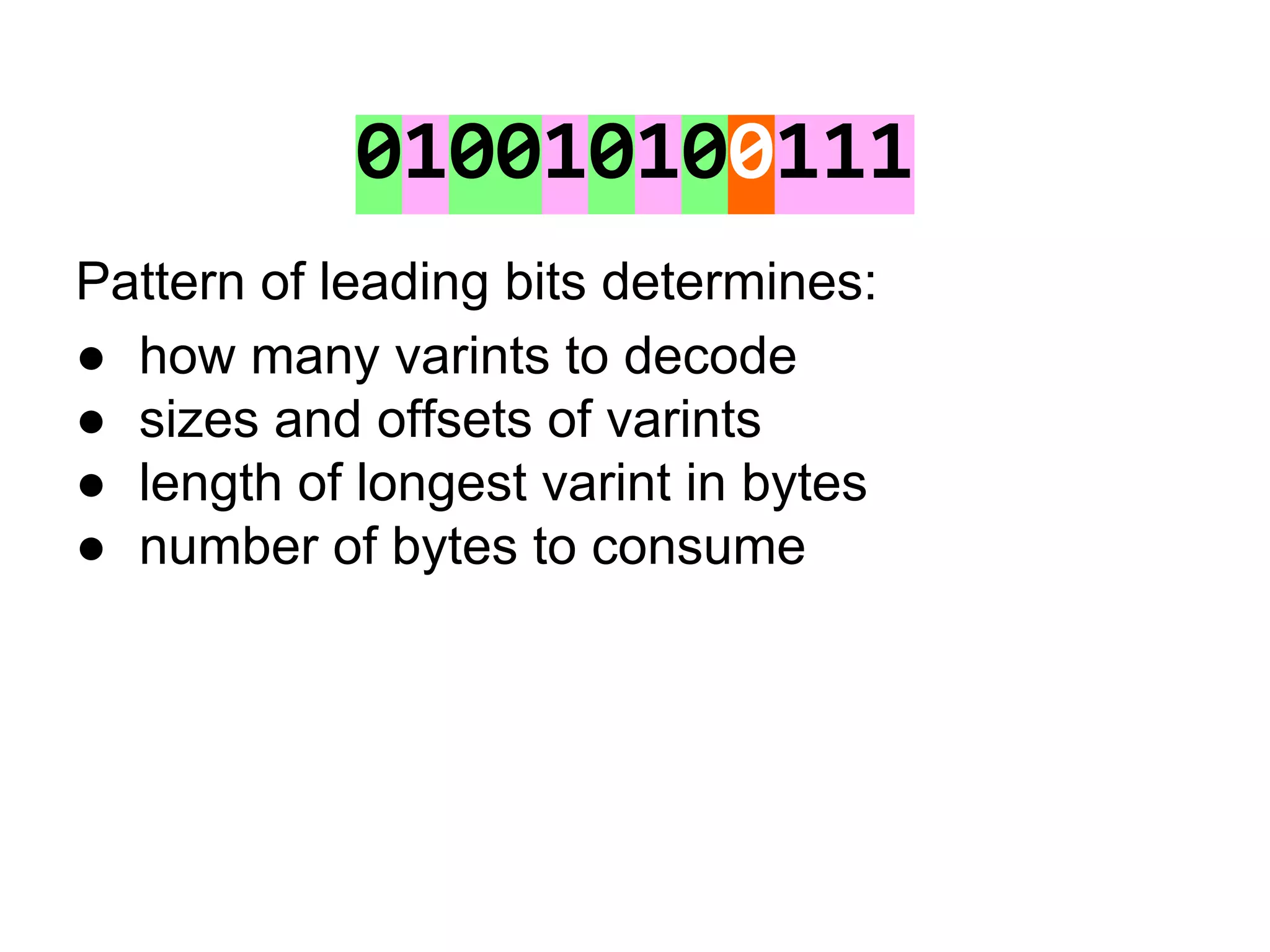

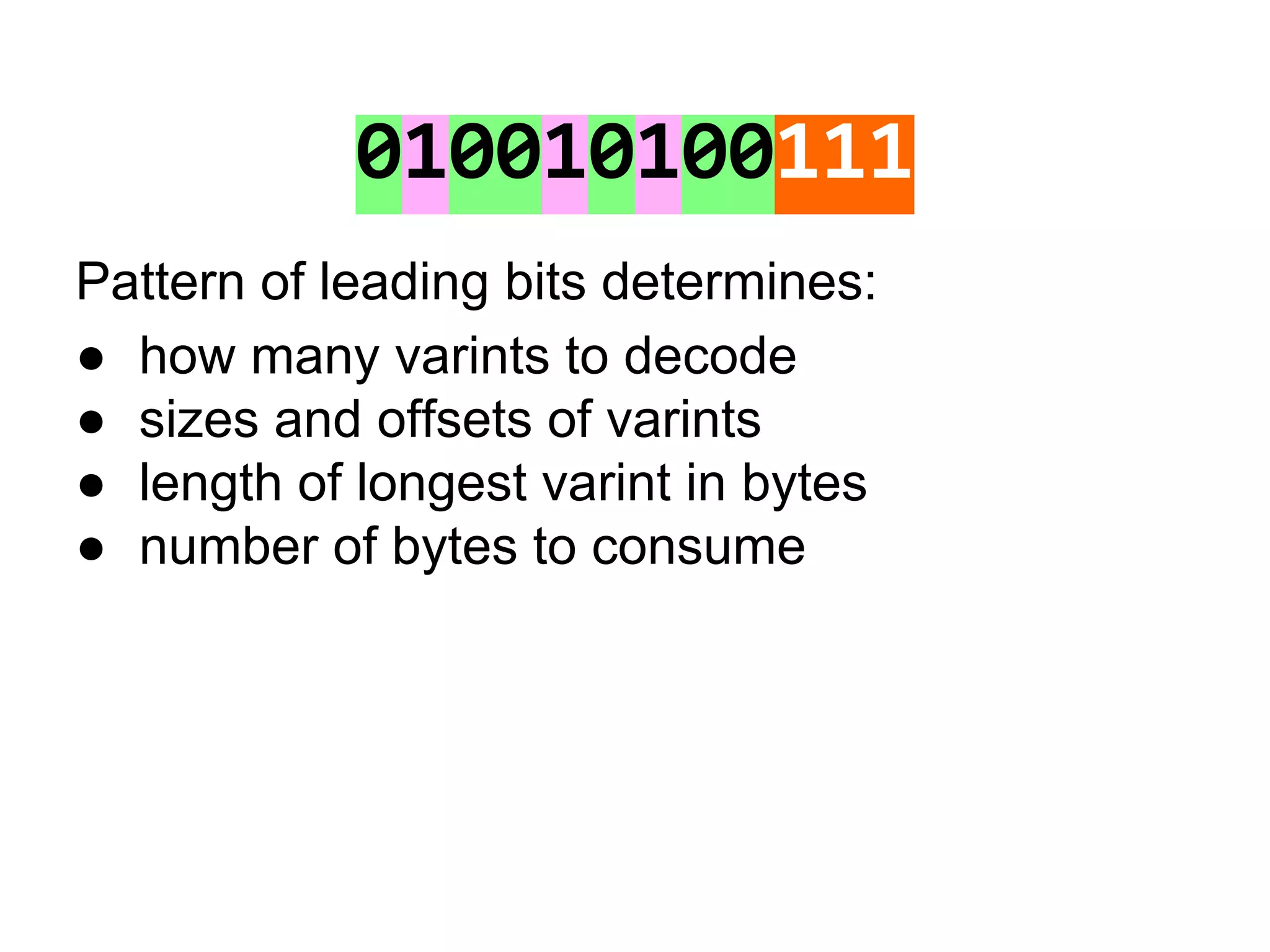

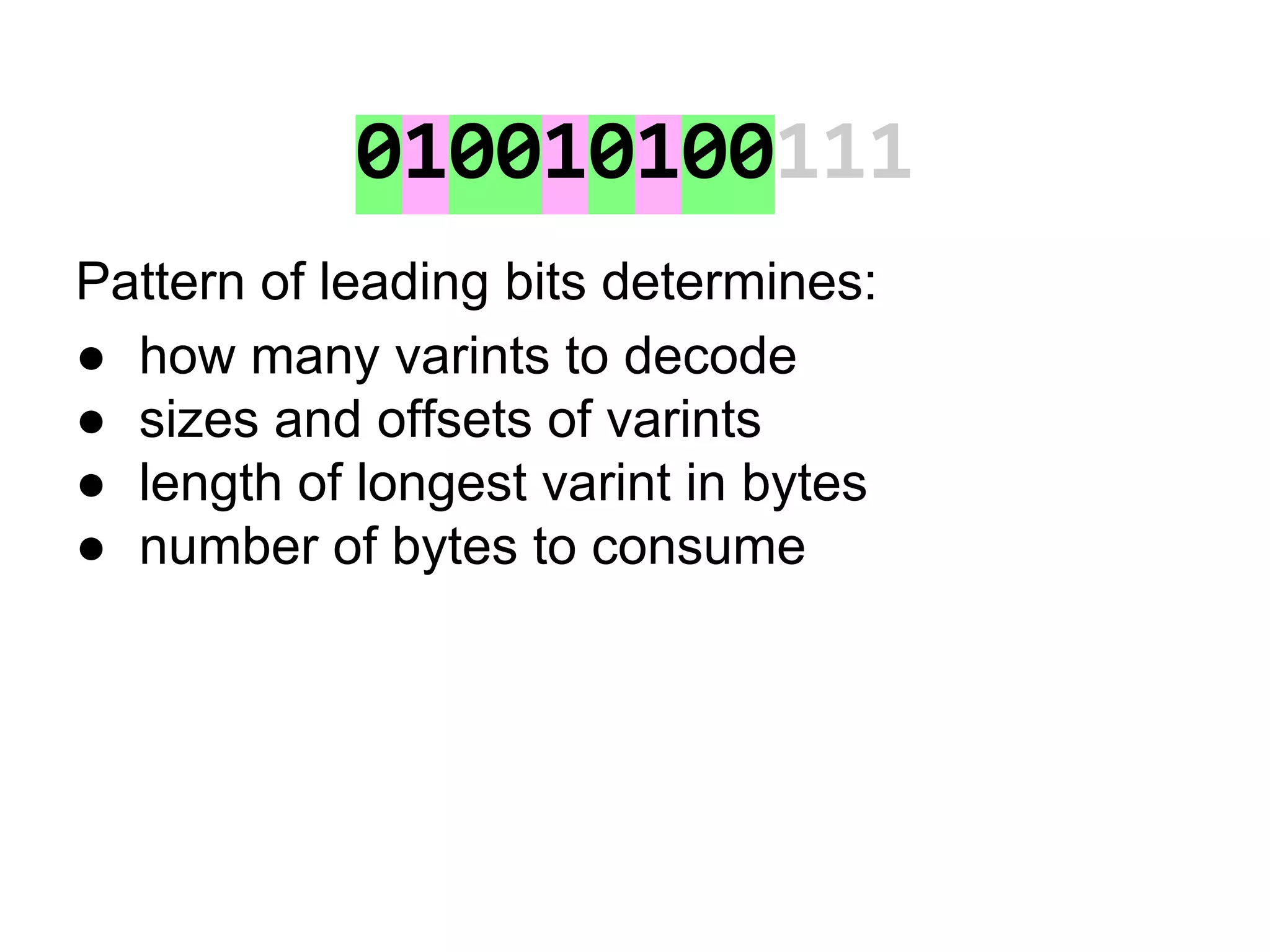

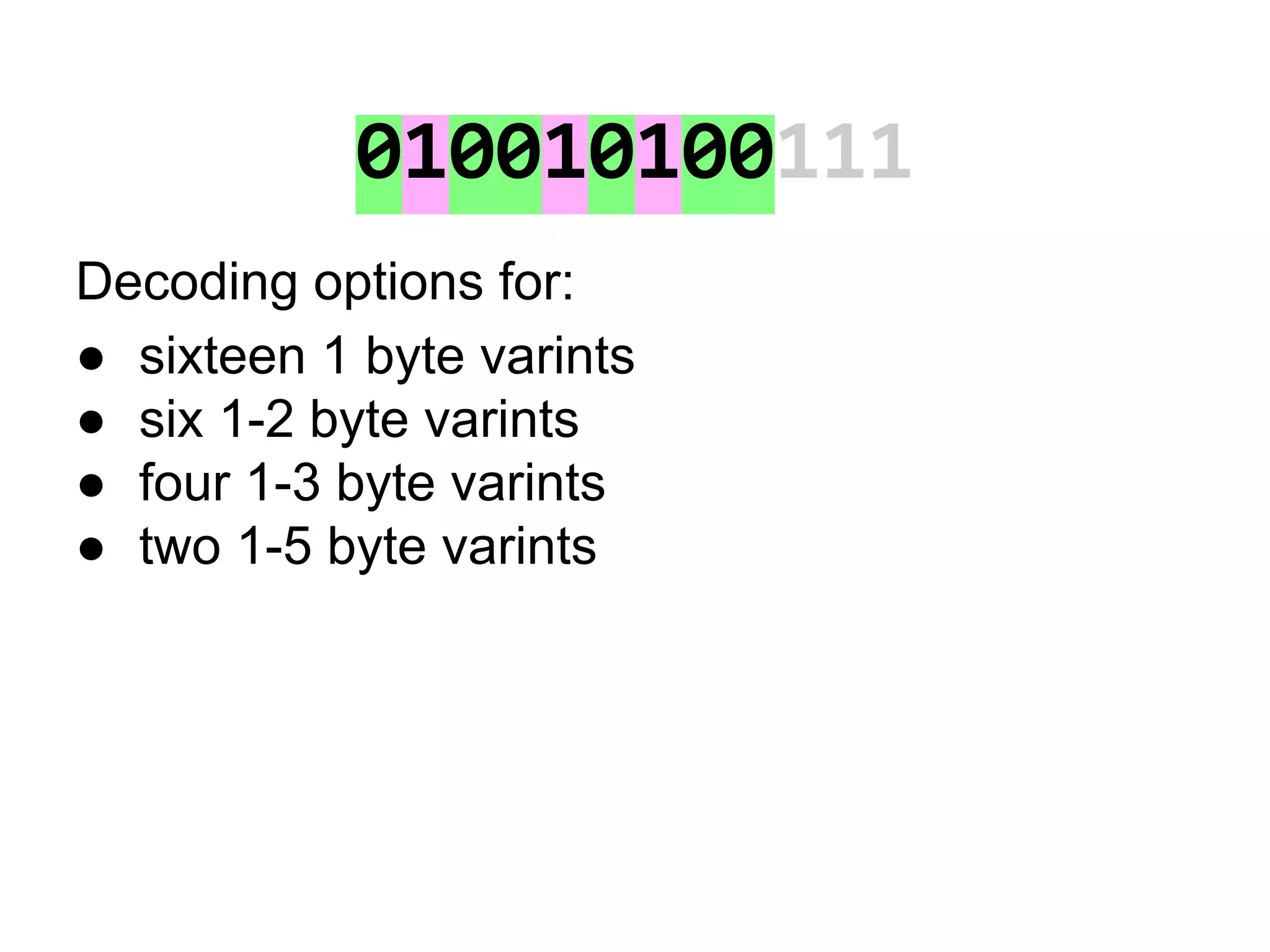

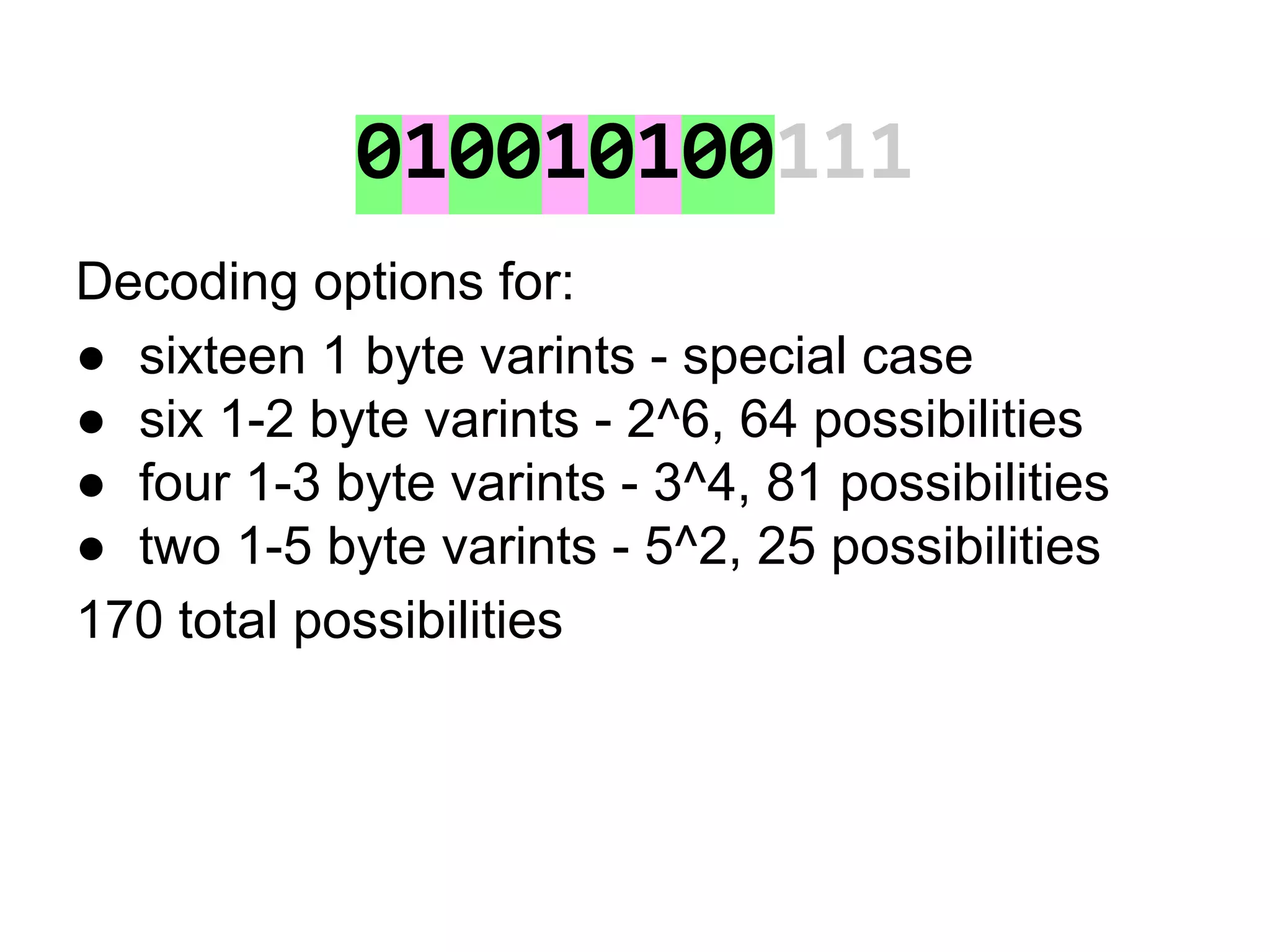

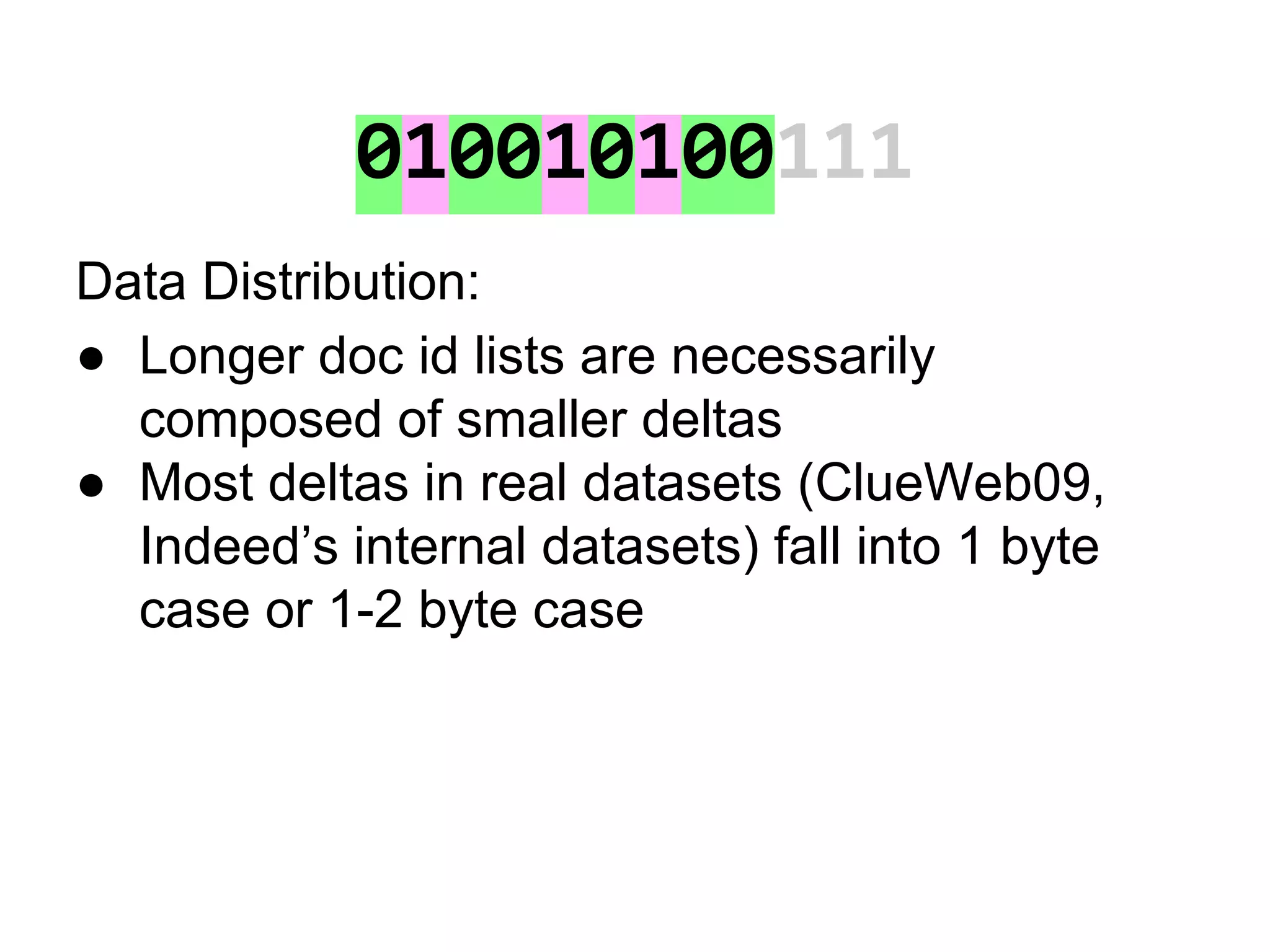

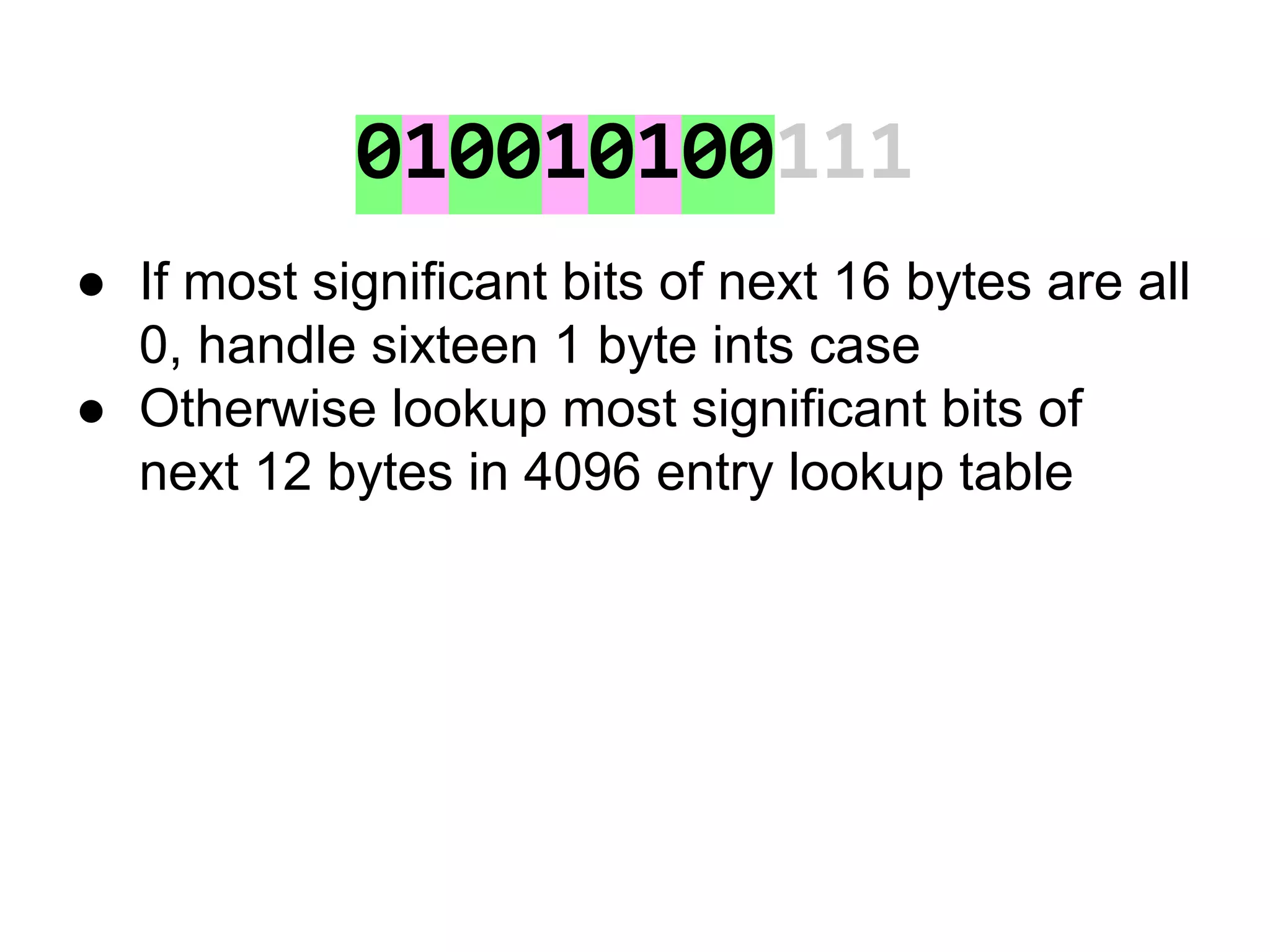

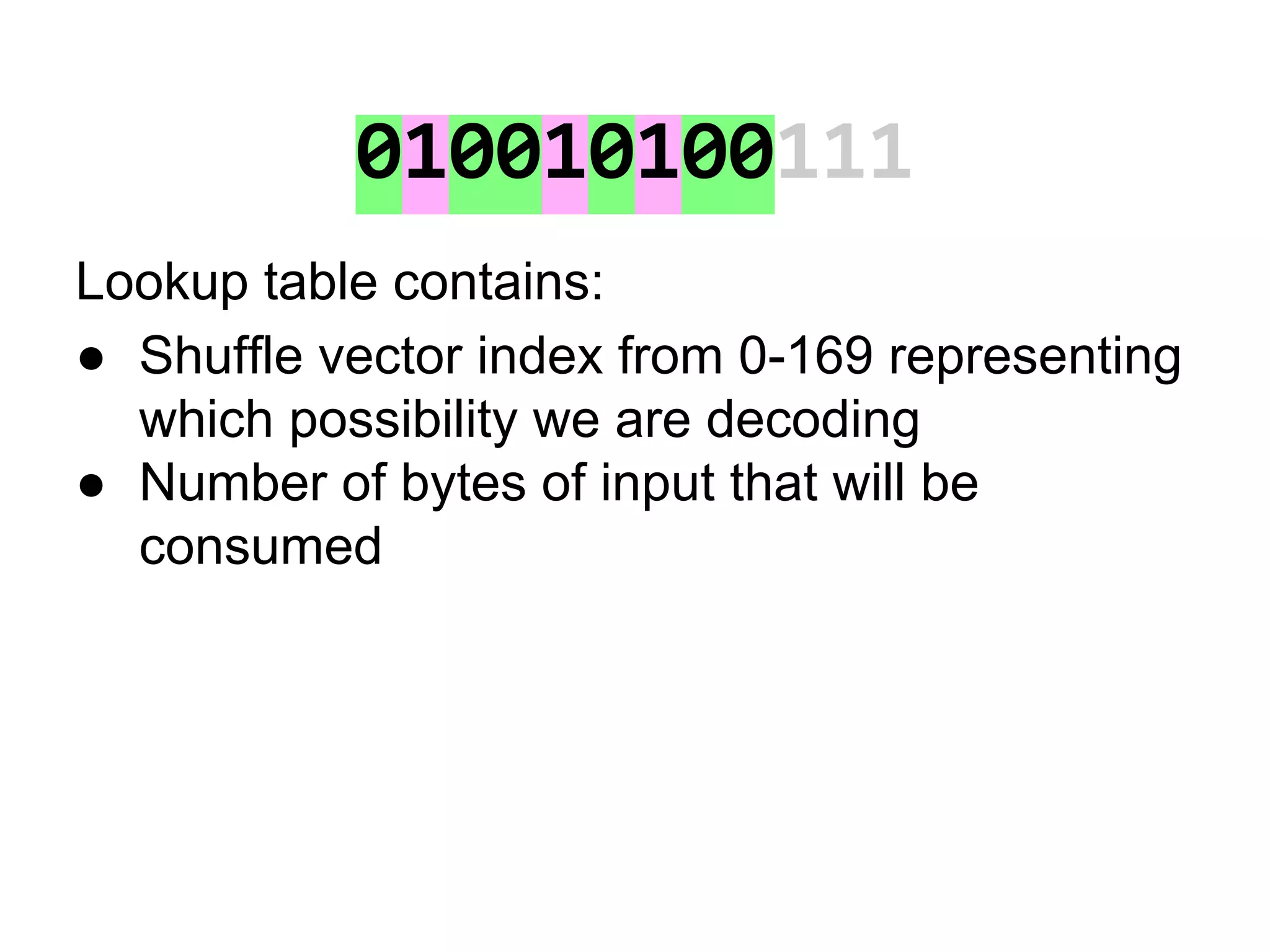

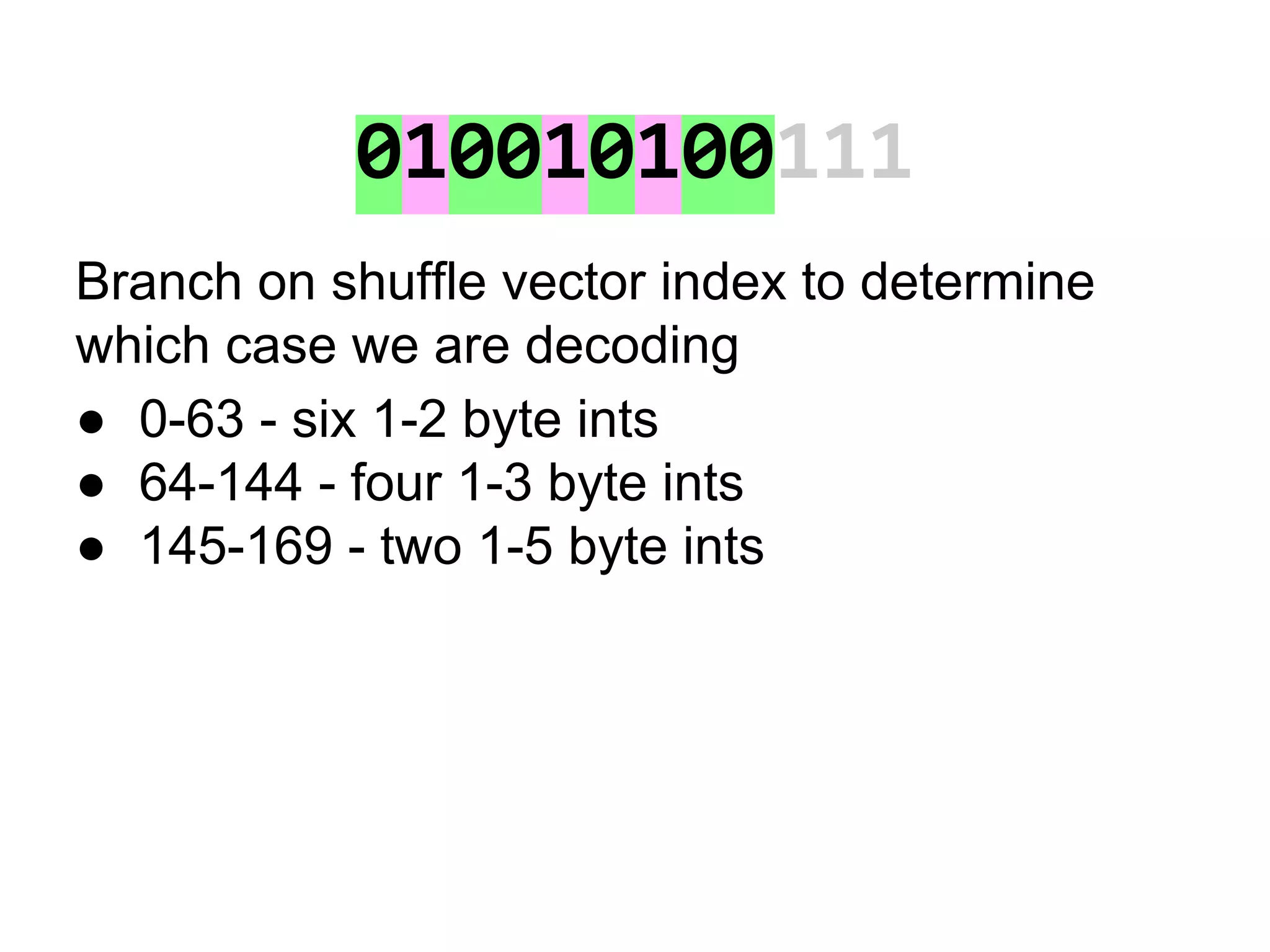

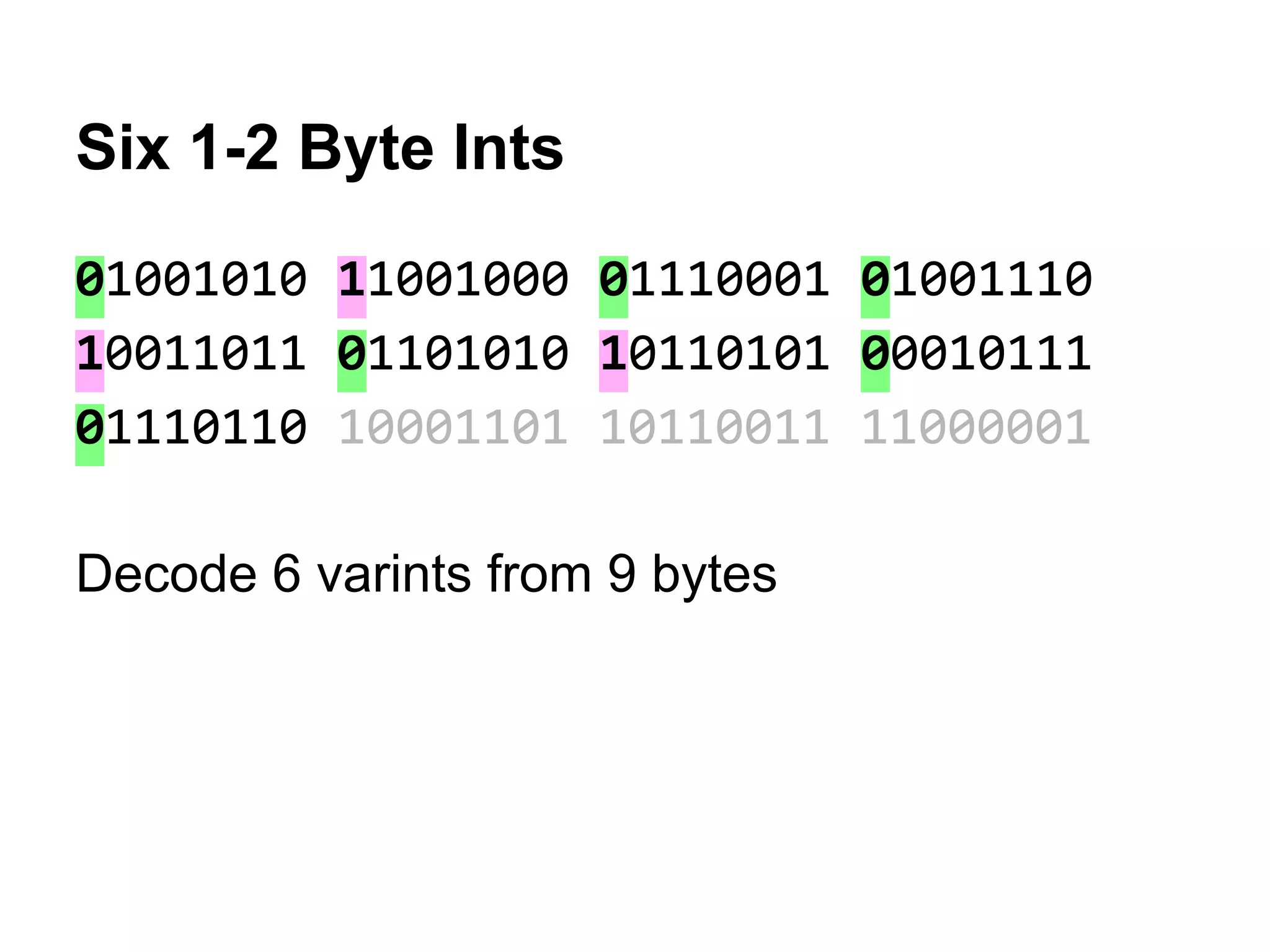

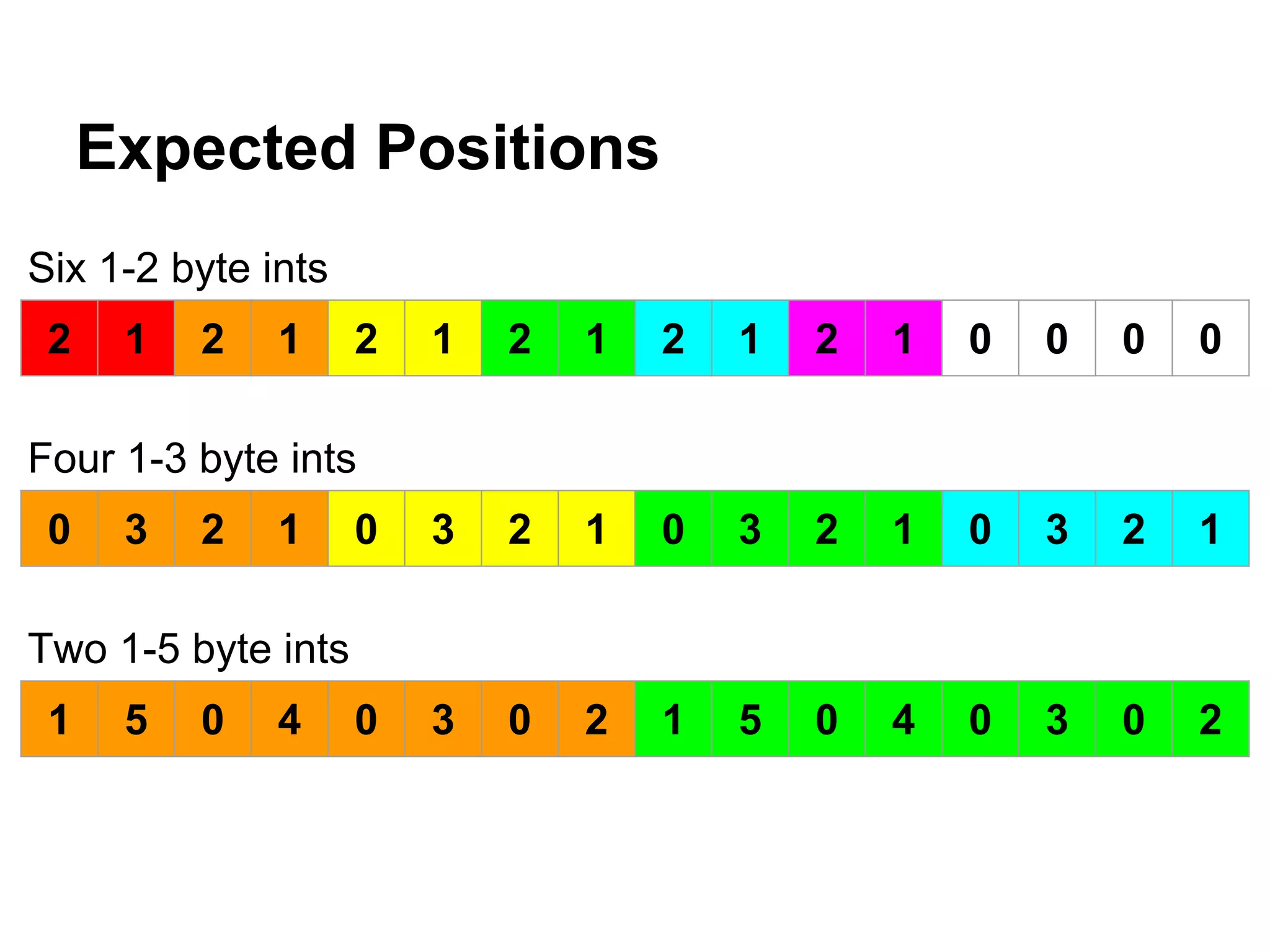

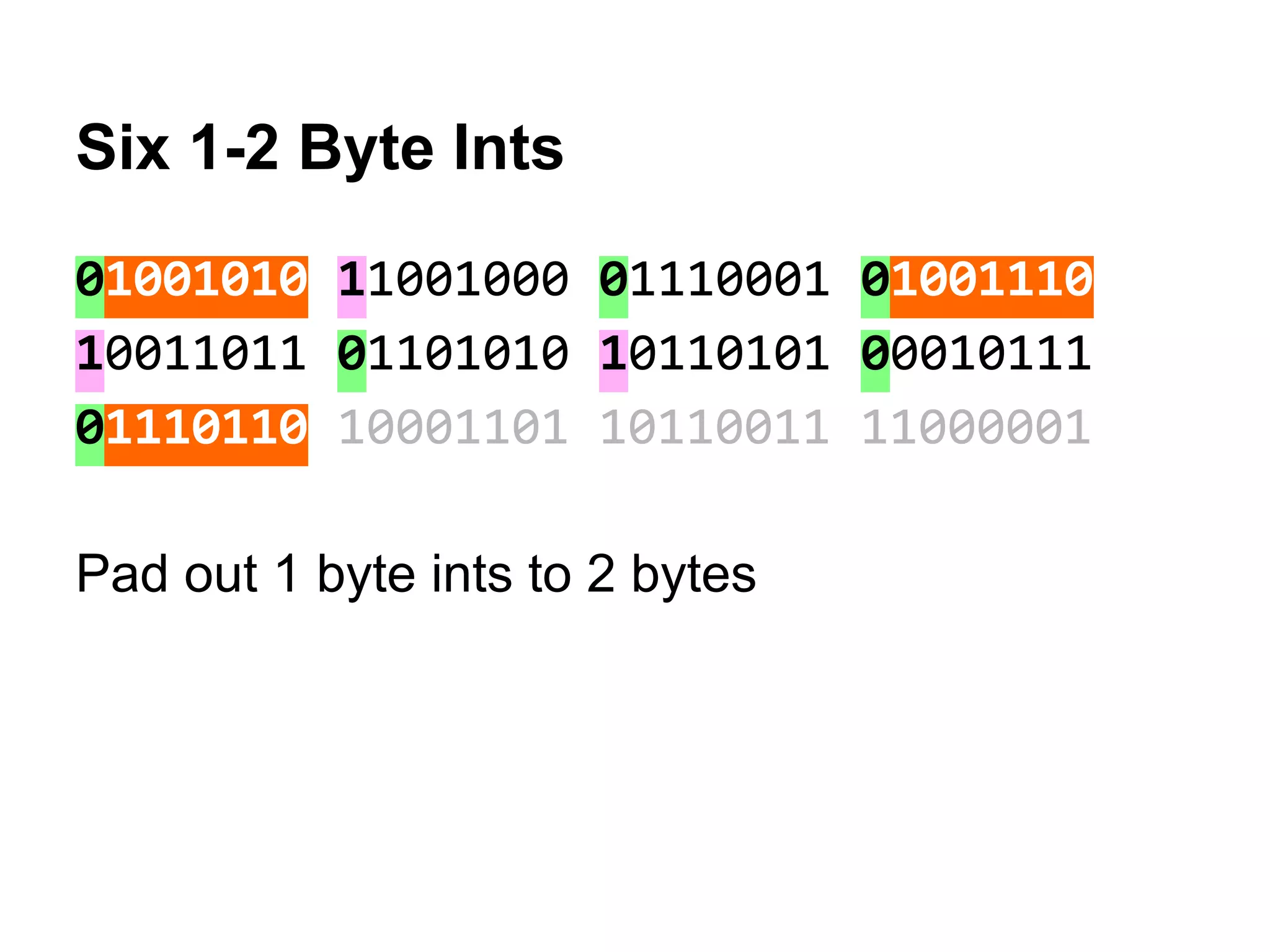

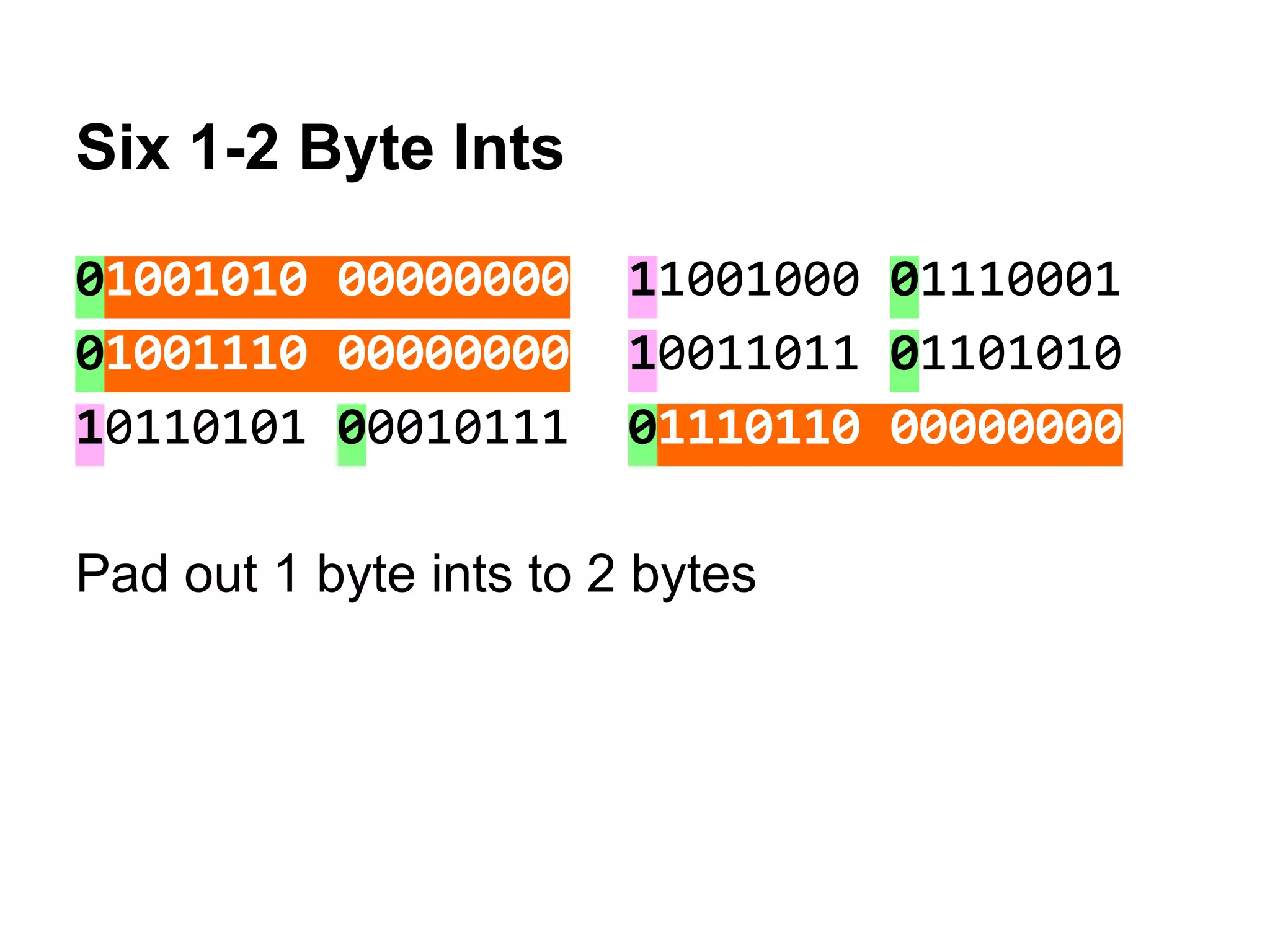

The document discusses techniques for optimizing inverted indexes used for document retrieval, including delta encoding and vectorized VByte decoding. Delta encoding stores the differences between adjacent document IDs rather than the IDs themselves, since differences are usually small integers. VByte encoding compresses these deltas into variable-length bytes. Vectorized VByte decoding decodes multiple VByte-encoded integers simultaneously using CPU intrinsics for improved performance over sequential decoding. It analyzes the variable-length encoding to group integers for bulk decoding in parallel.

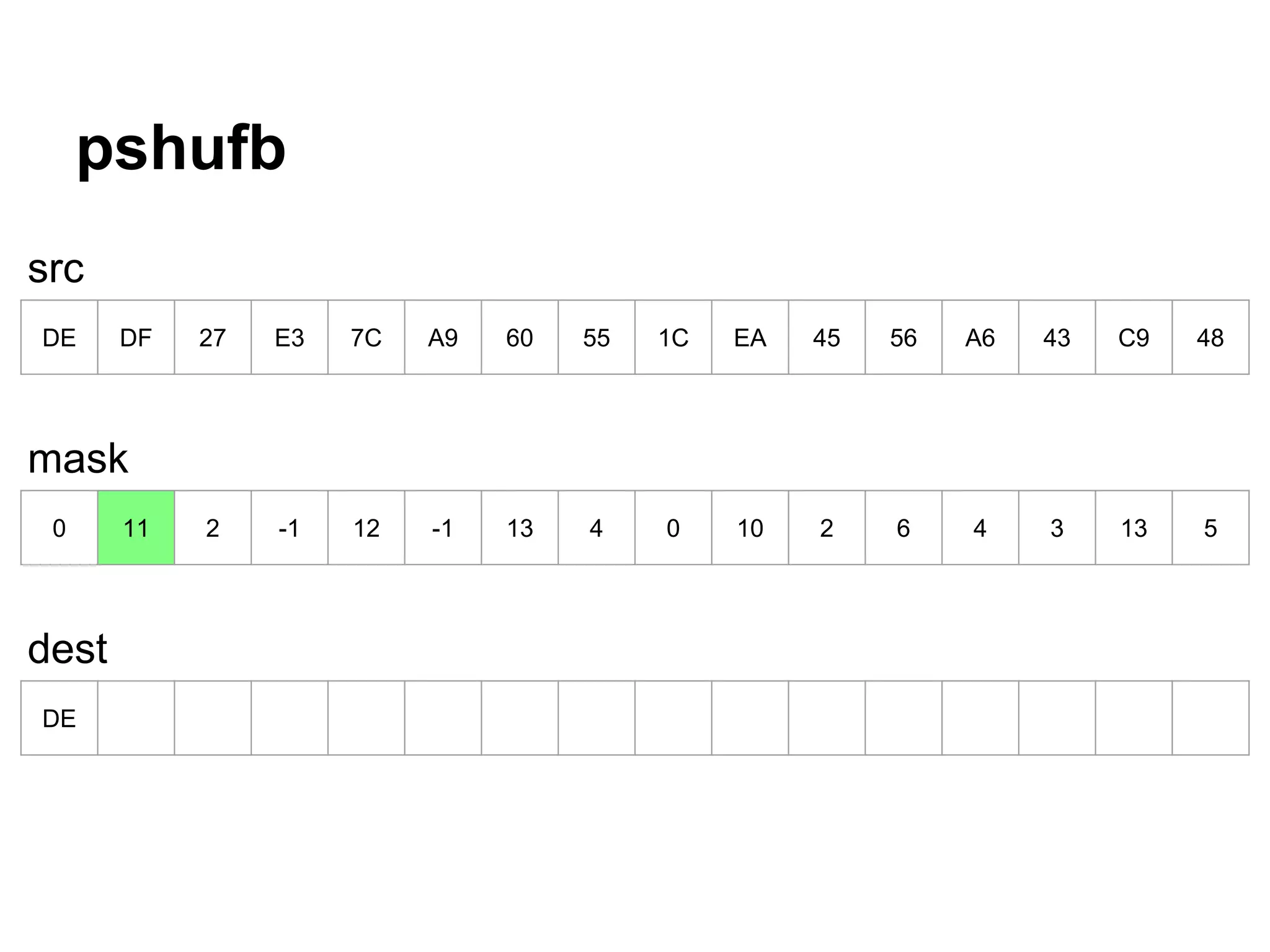

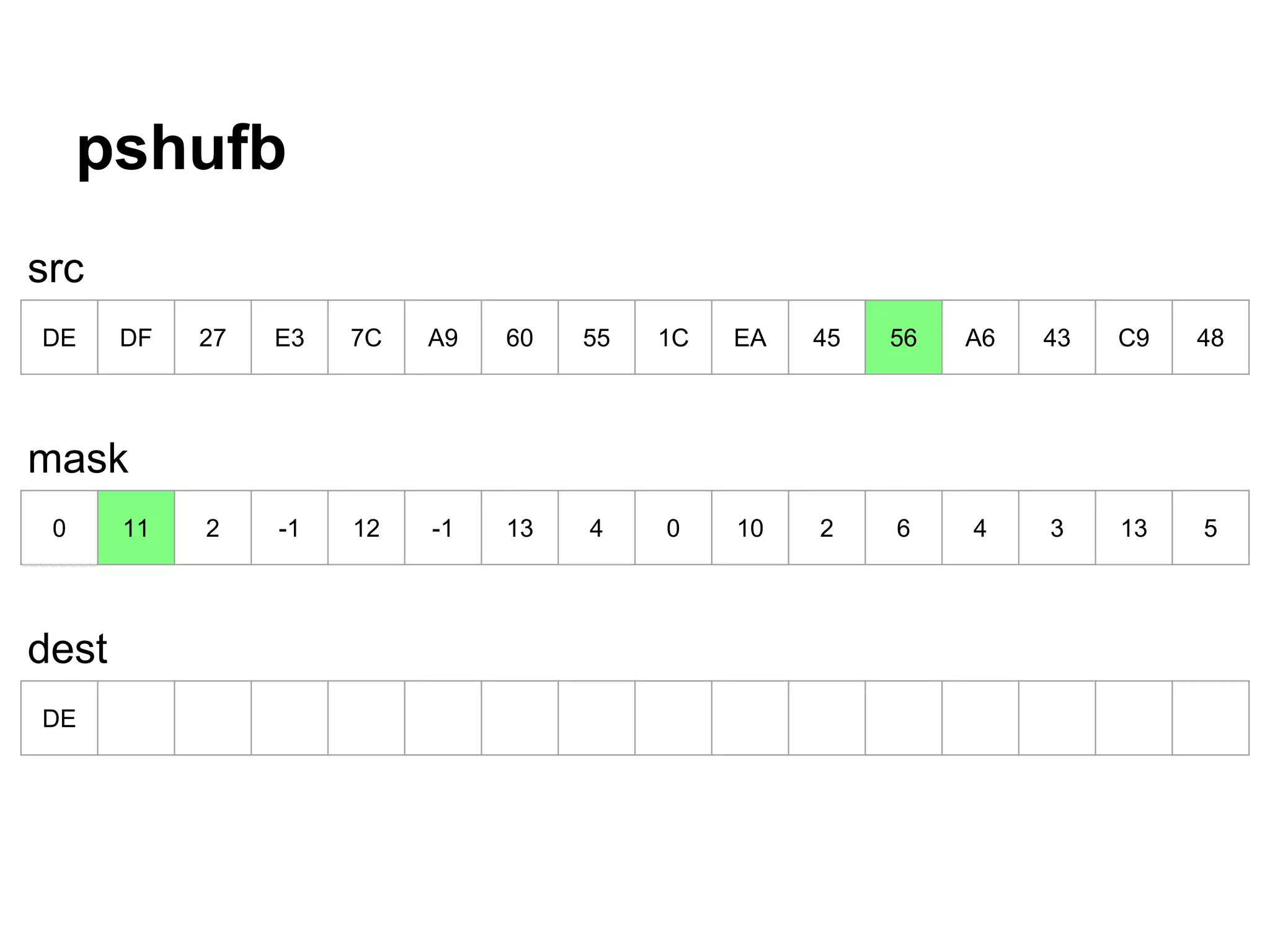

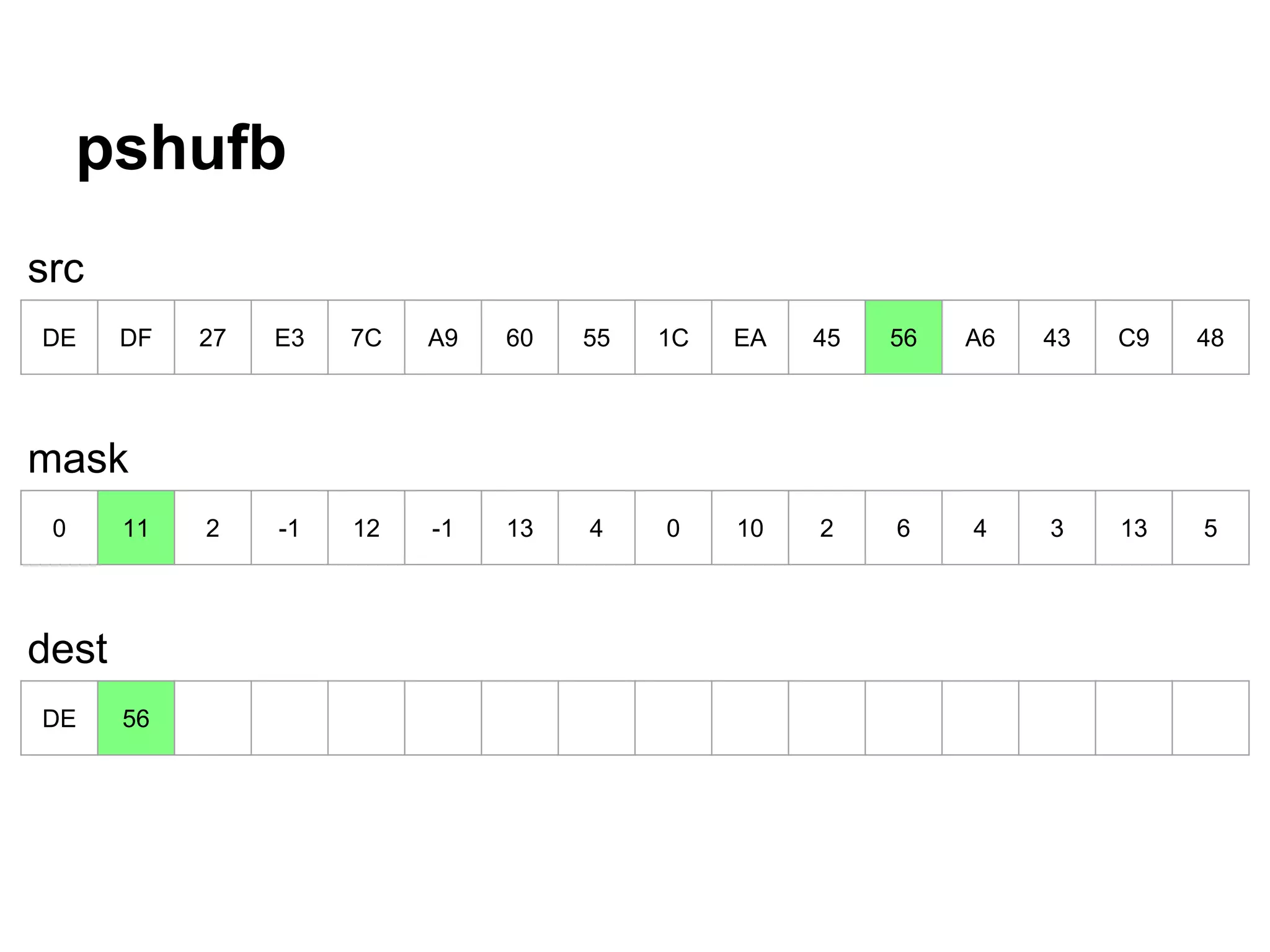

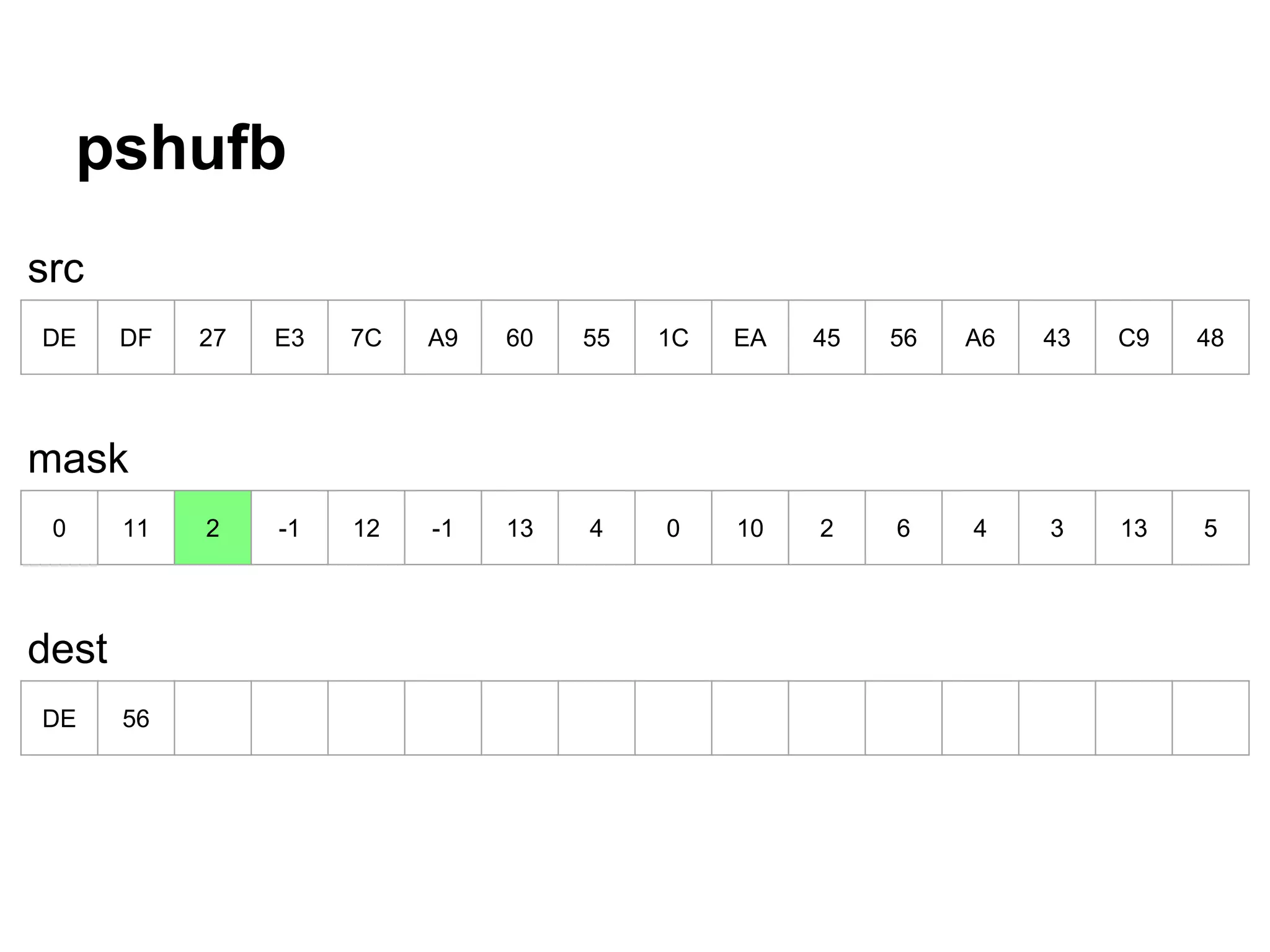

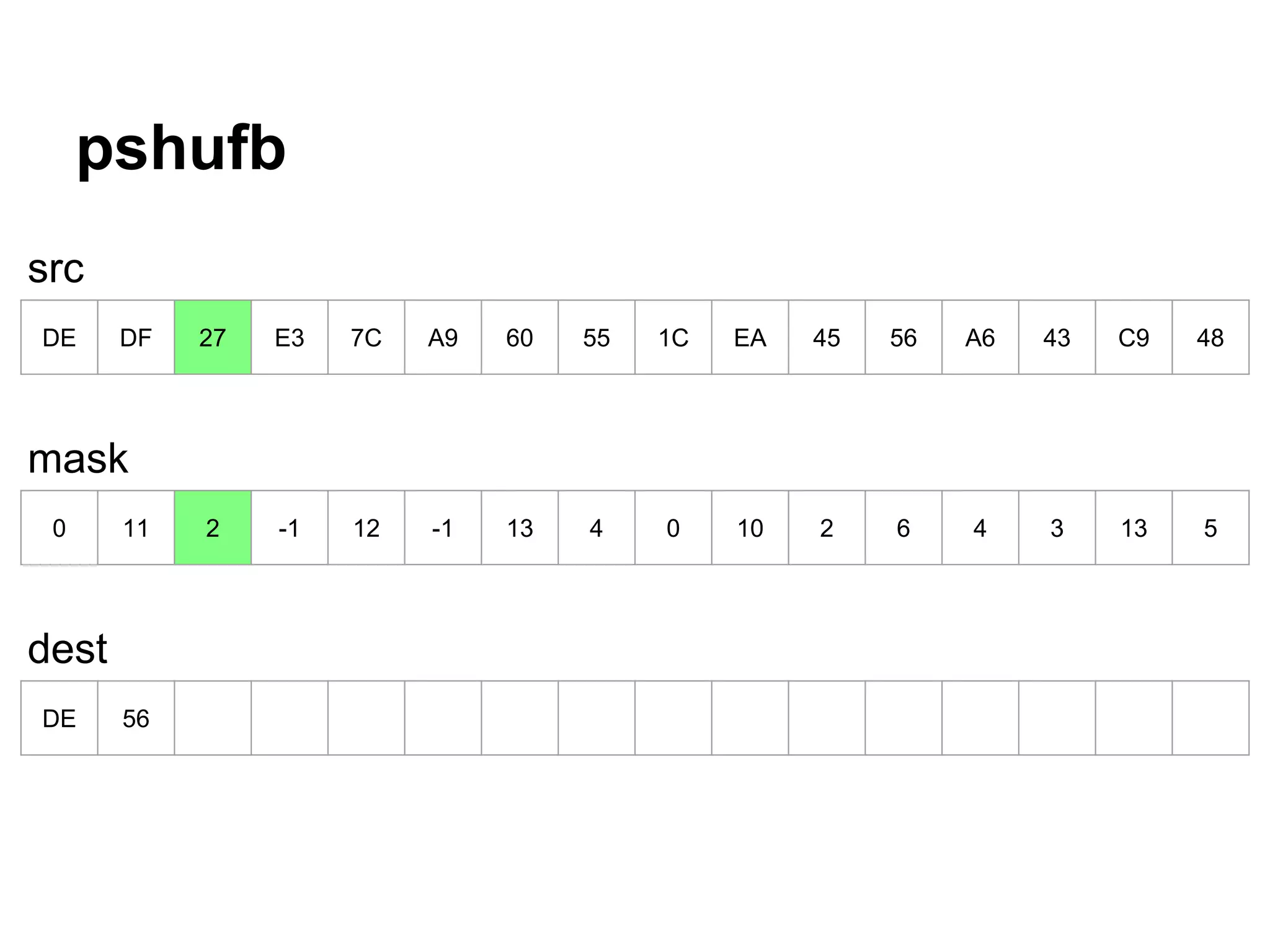

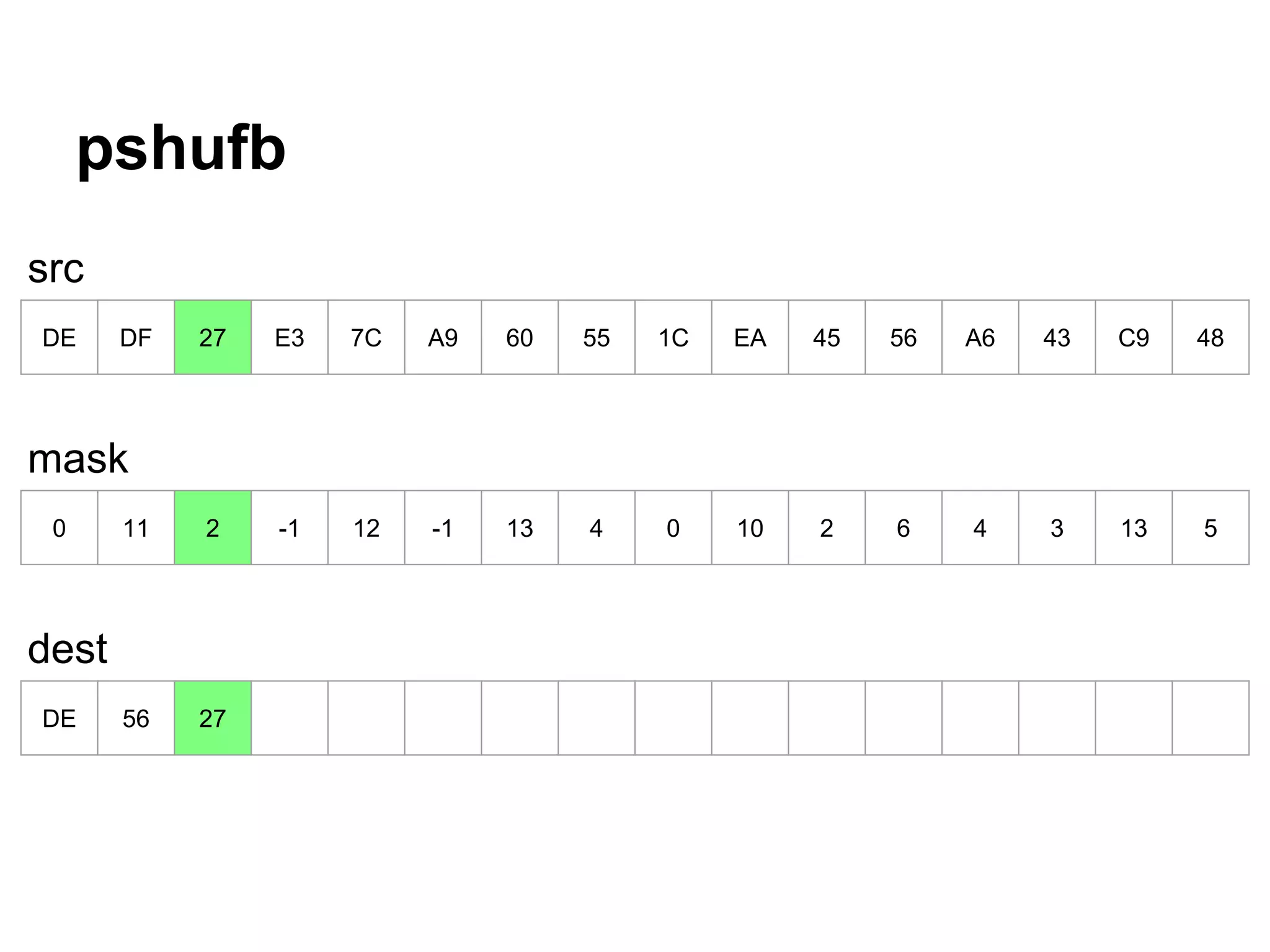

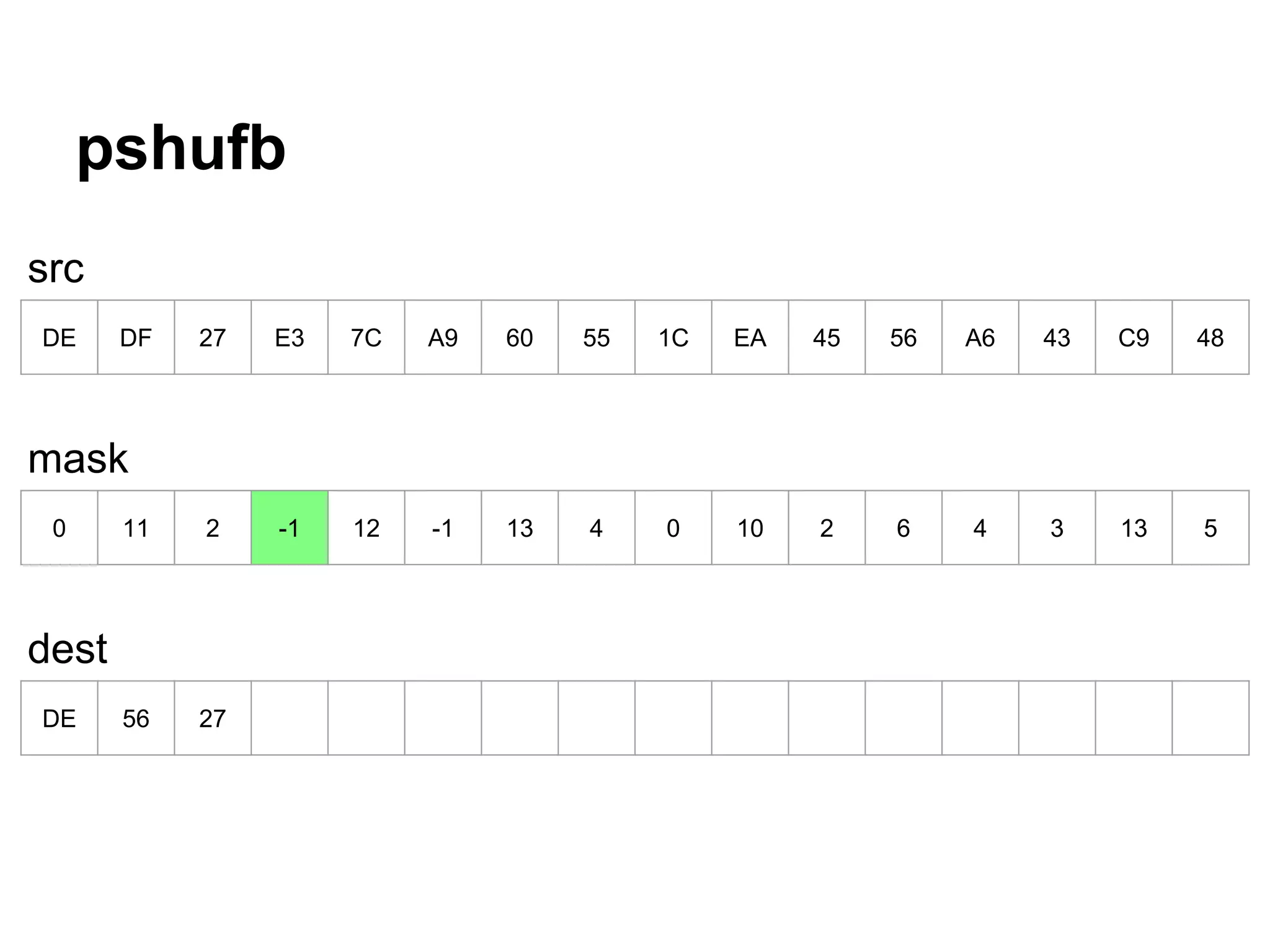

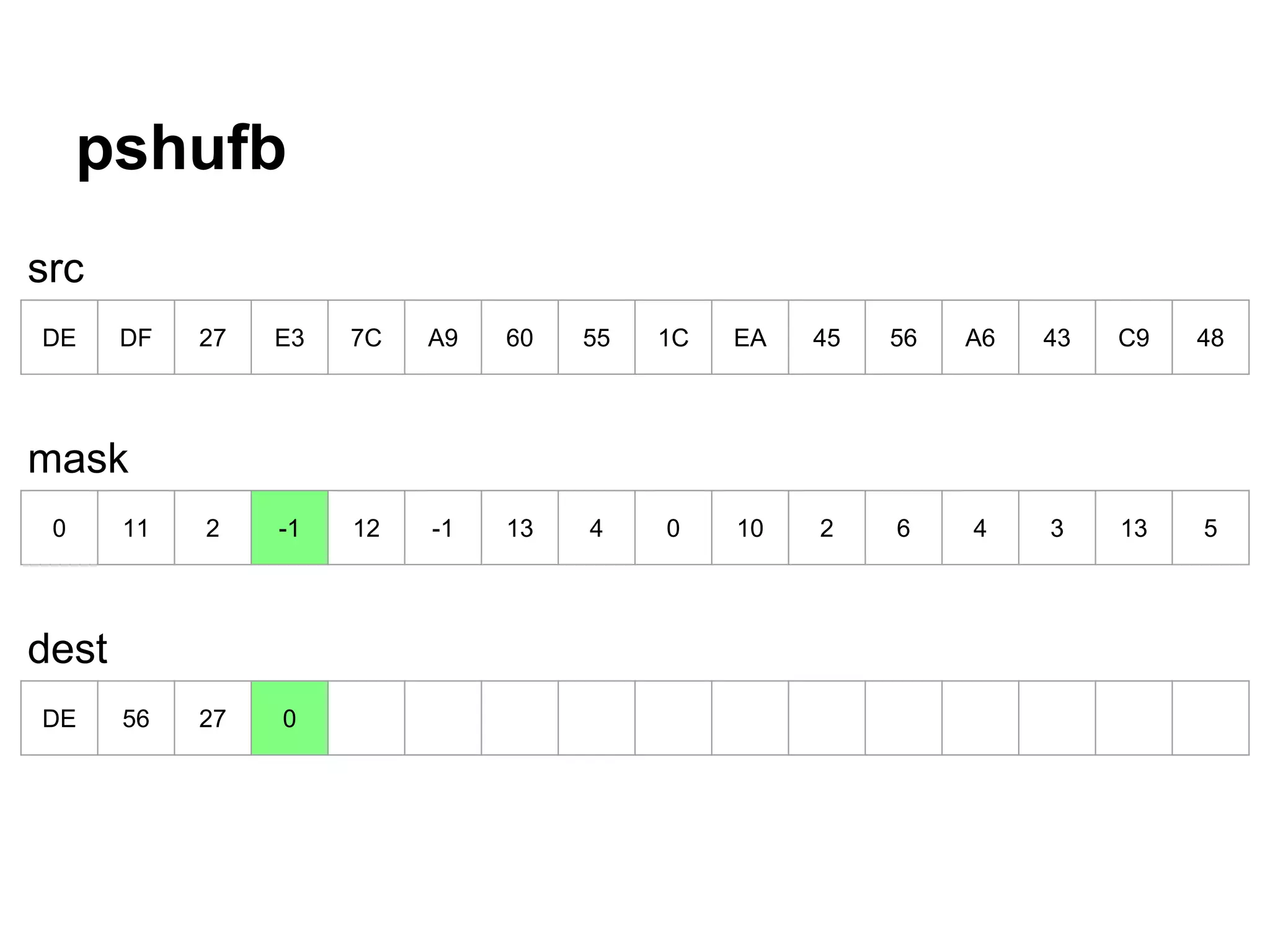

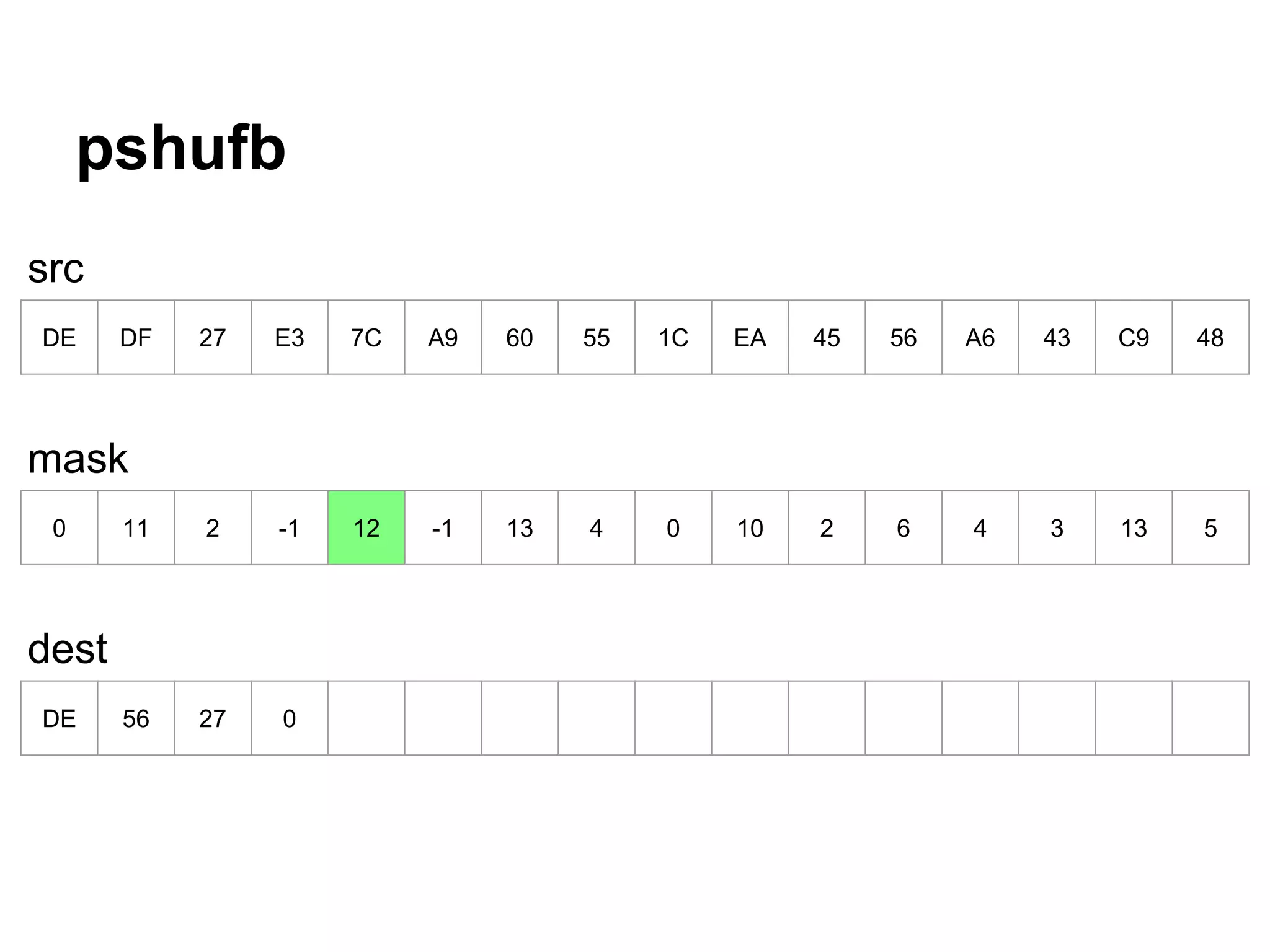

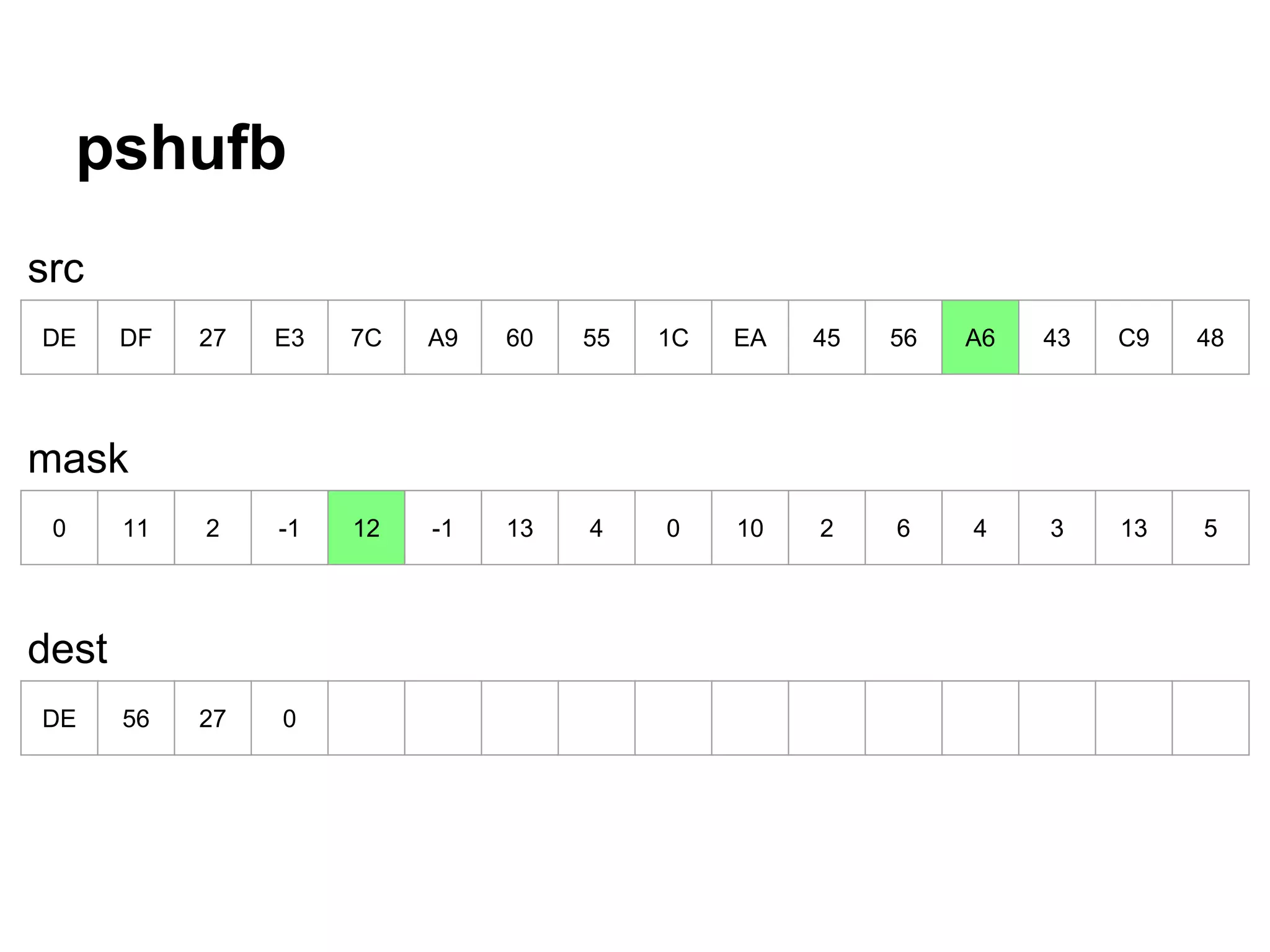

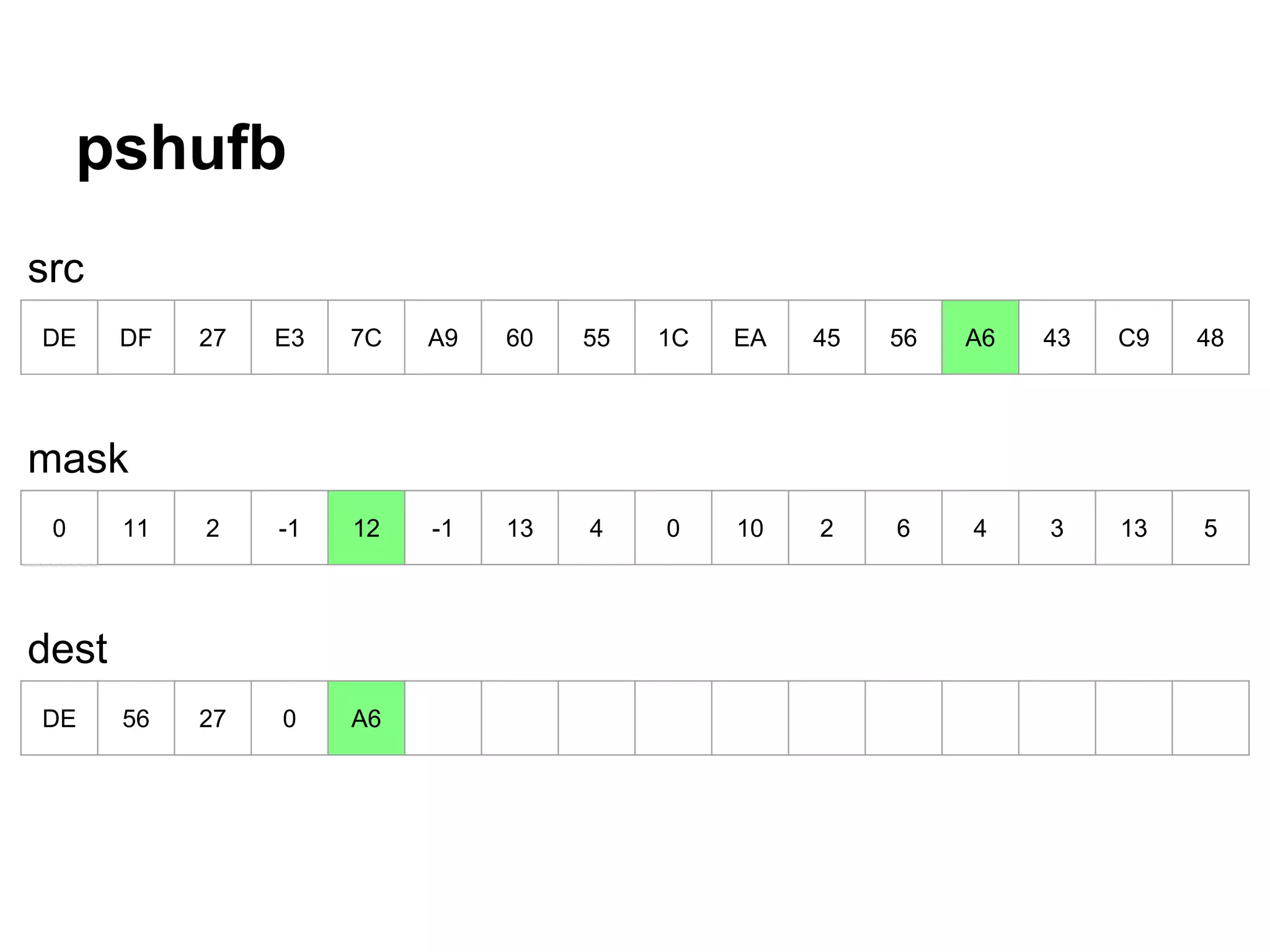

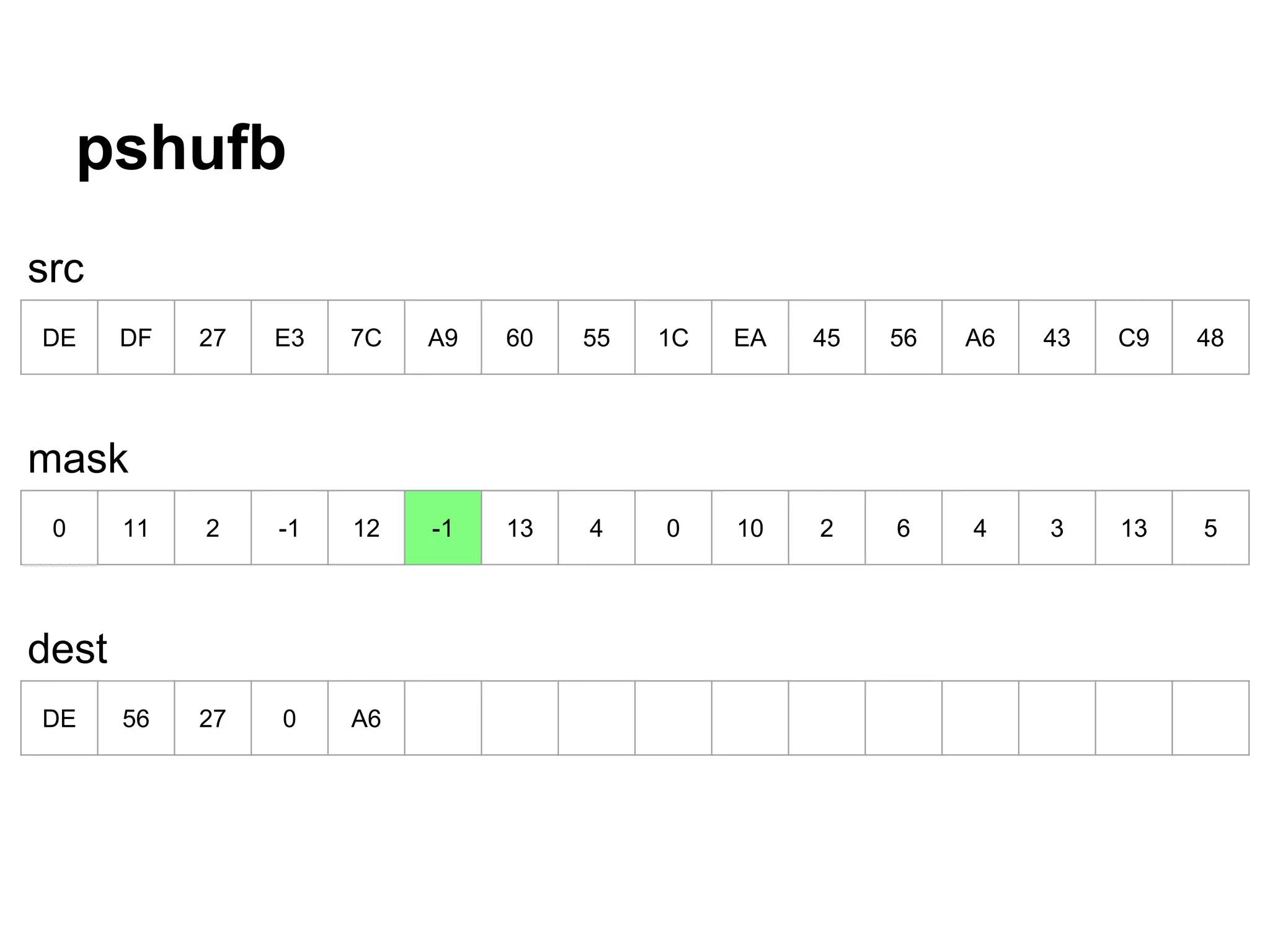

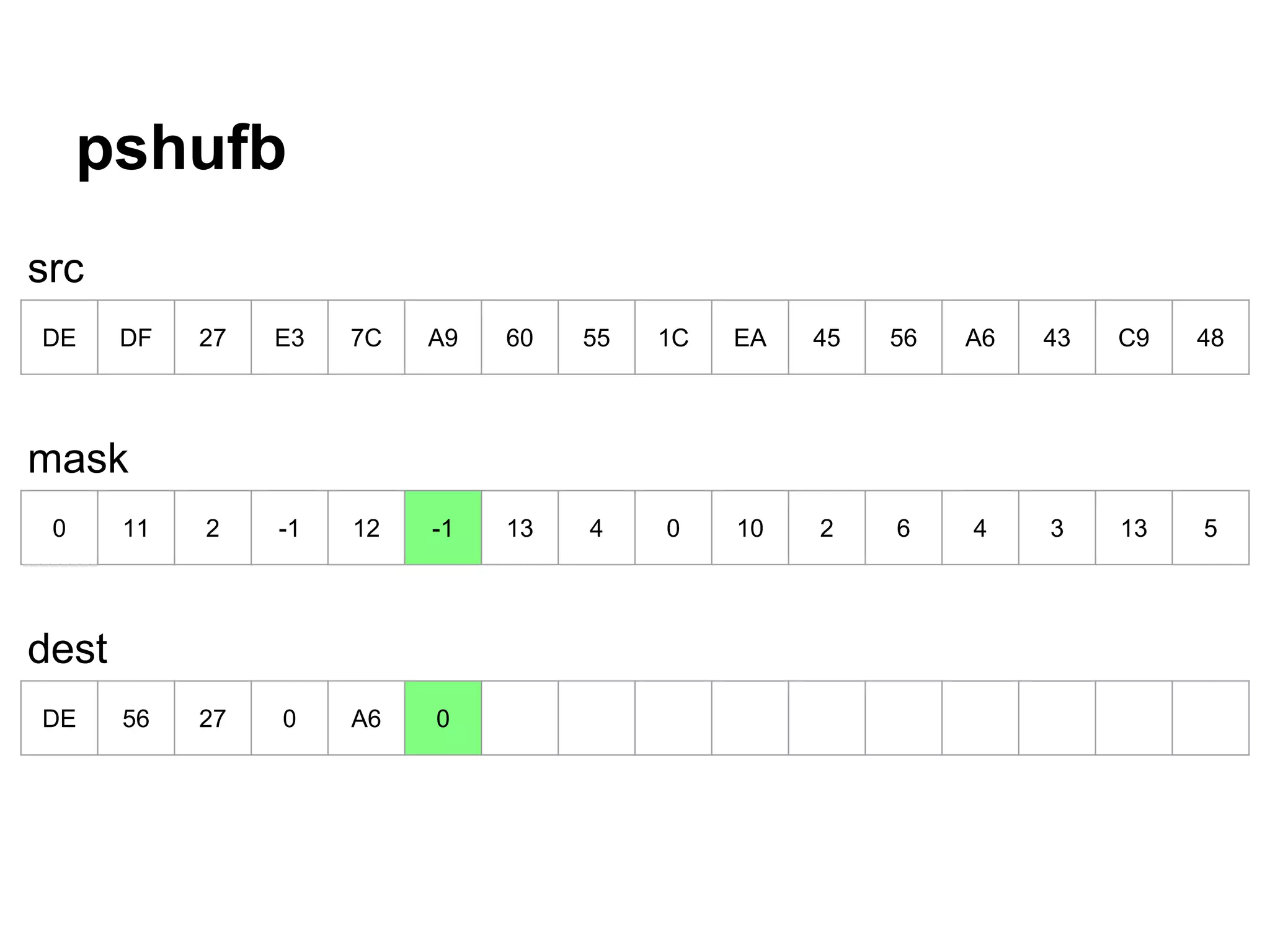

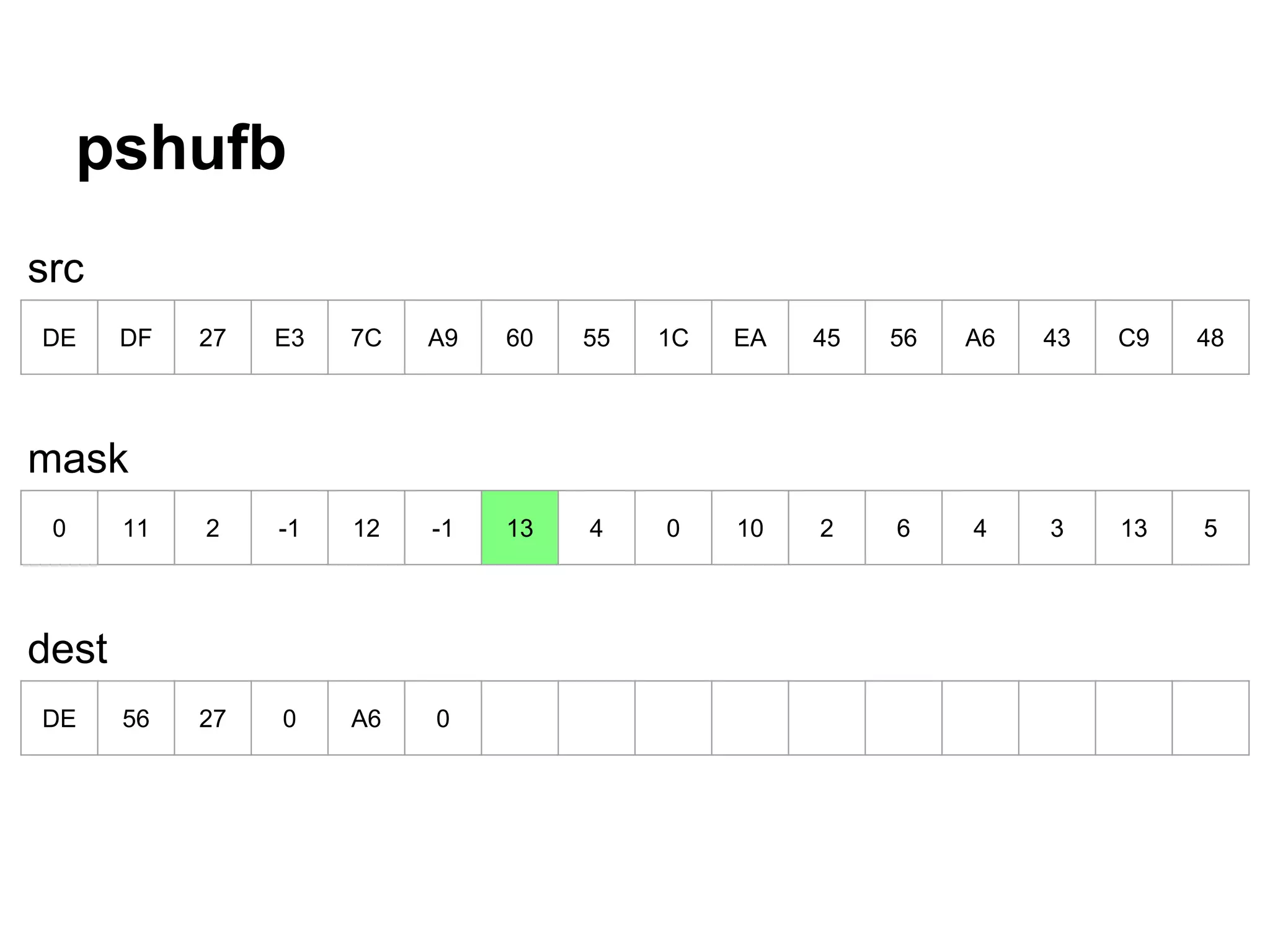

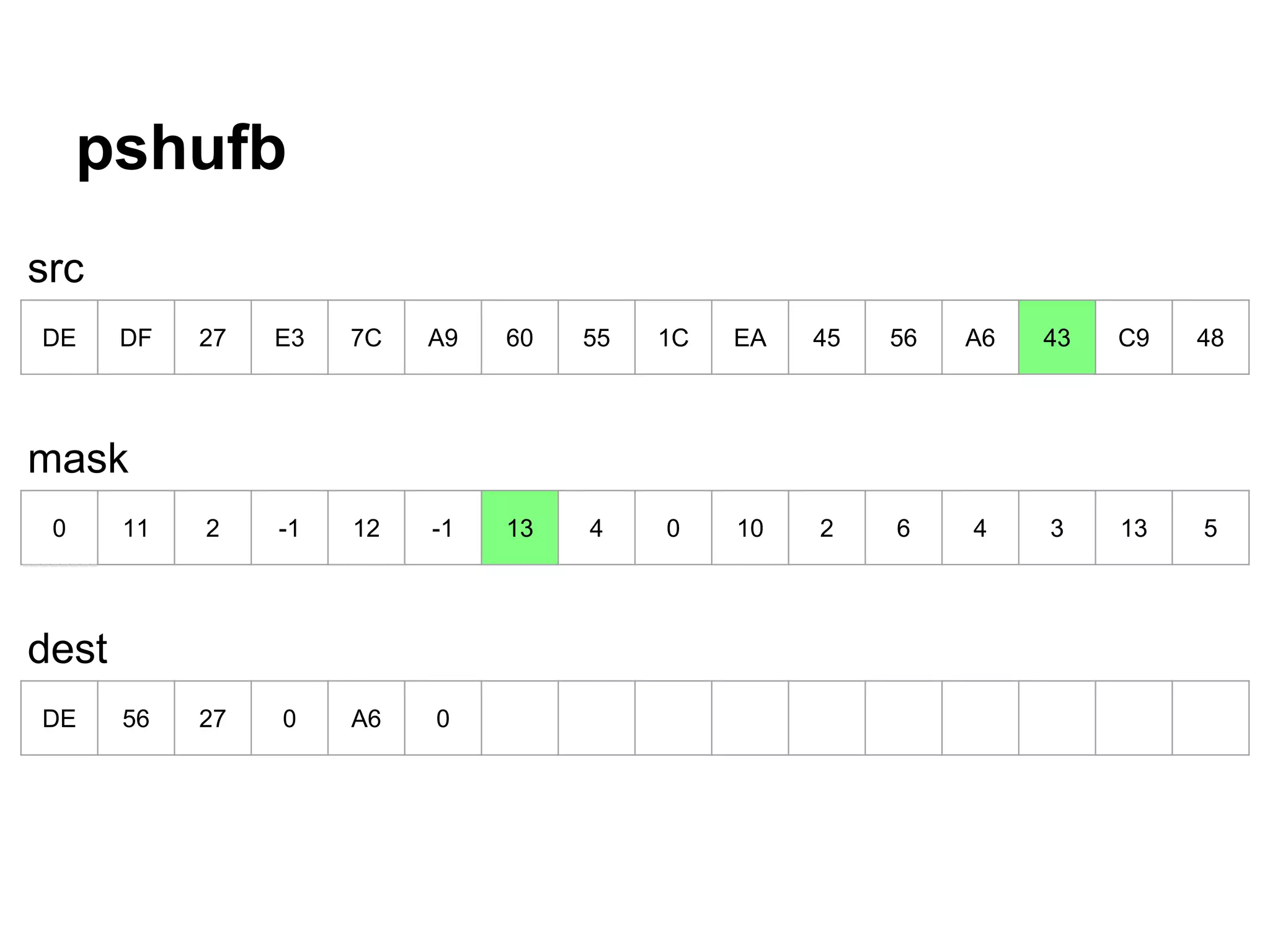

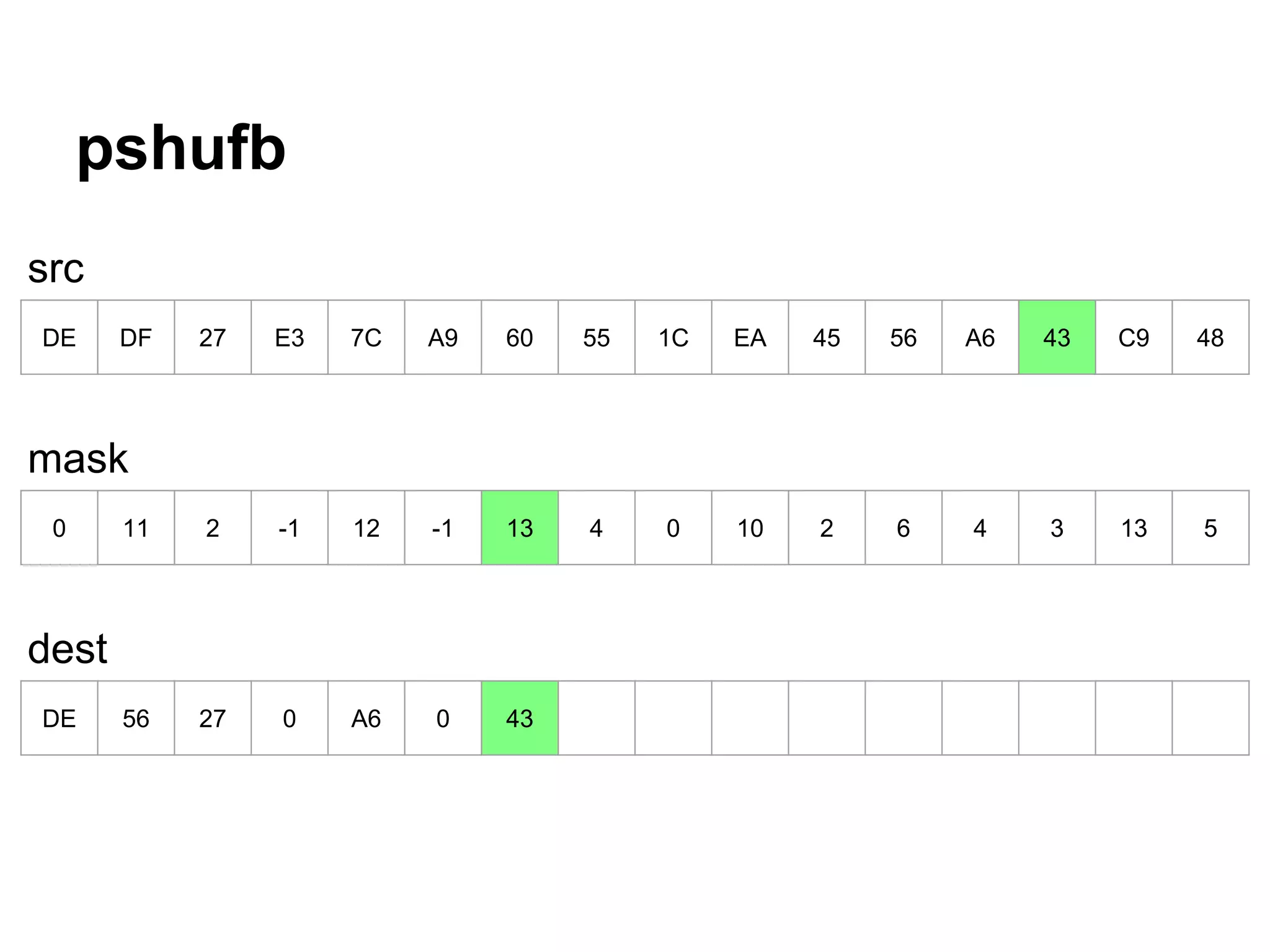

![for (i = 0; i < 16; i++) {

if (mask[i] & 0x80) {

dest[i] = 0;

} else {

dest[i] = src[mask[i] & 0xF];

}

}

pshufb](https://image.slidesharecdn.com/vectorizedvbytedecoding-160308034357/75/MaskedVByte-SIMD-accelerated-VByte-57-2048.jpg)