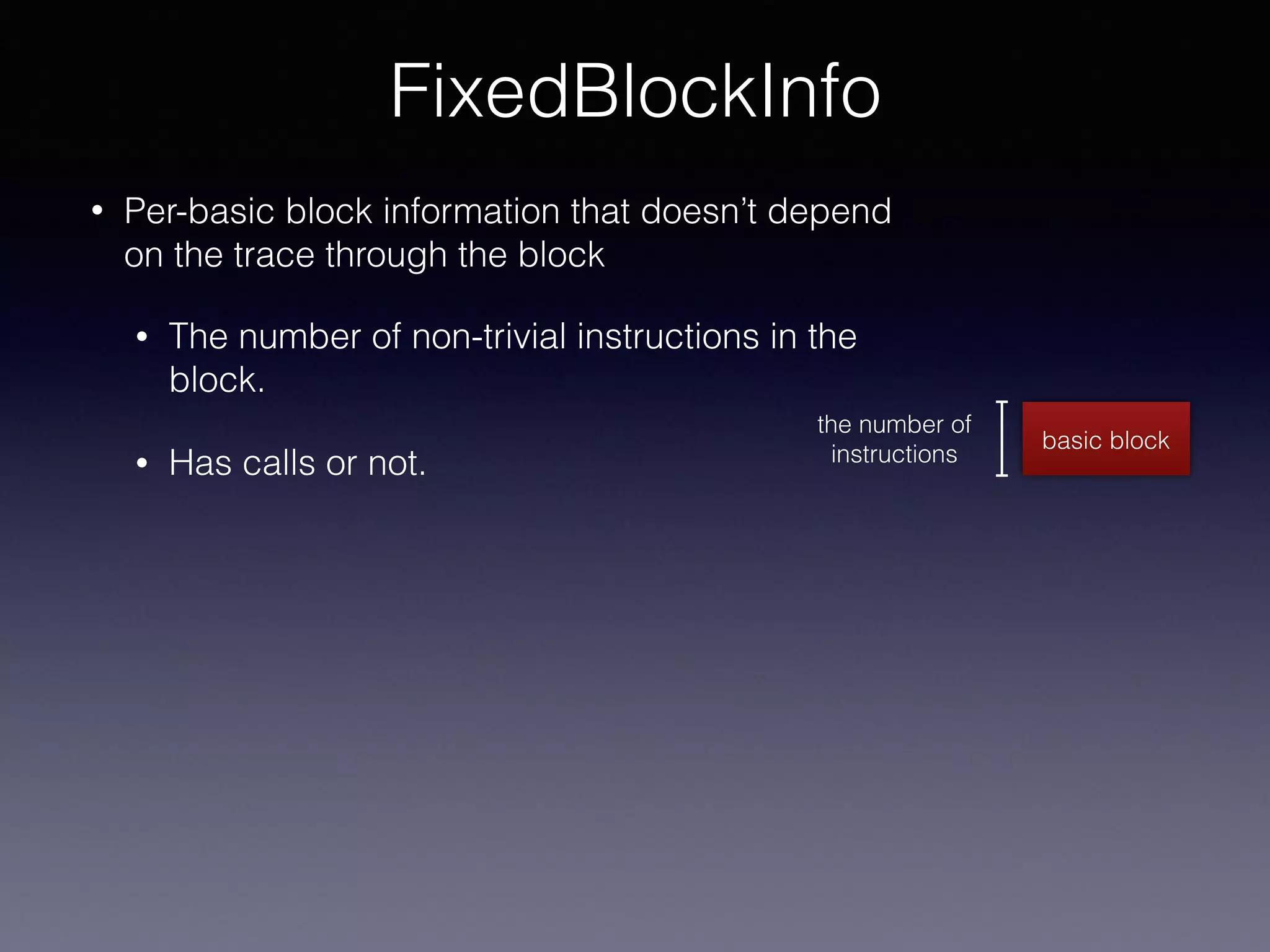

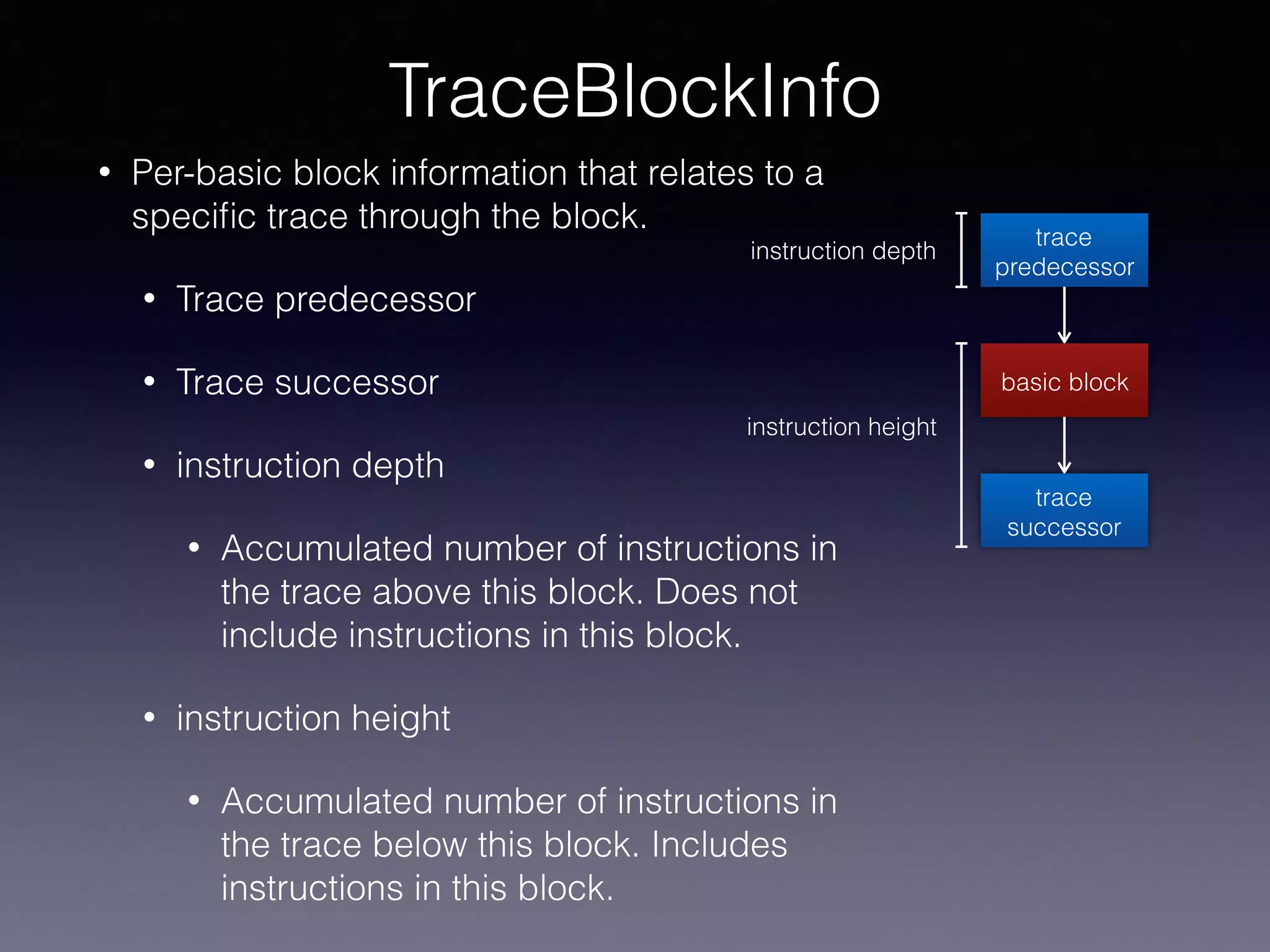

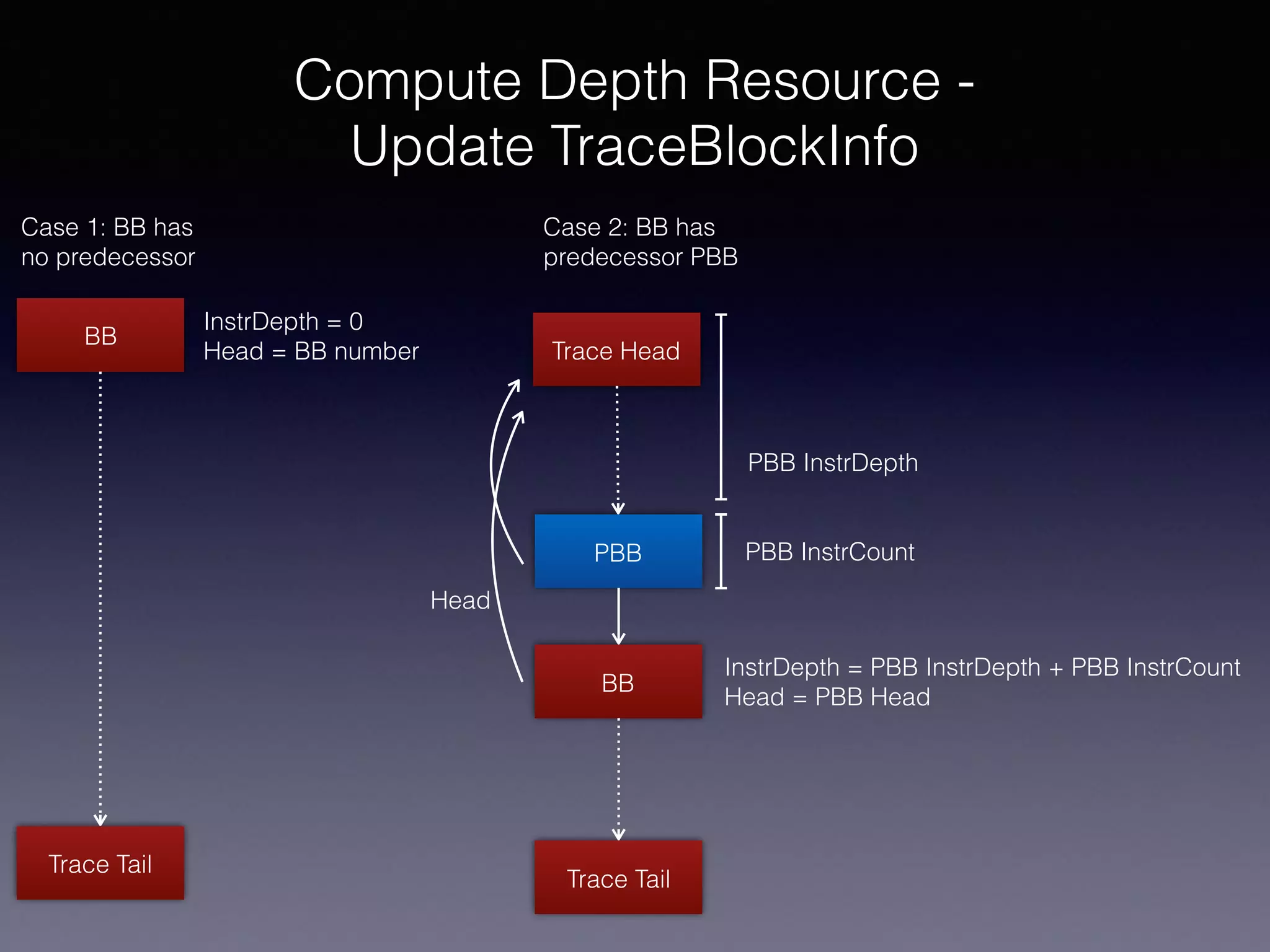

1. The document describes methods for computing trace metrics like instruction depth, height, and critical path length for basic blocks. It involves analyzing data dependencies between instructions within and across blocks to determine earliest issue cycles while traversing the trace in postorder and inverse postorder.

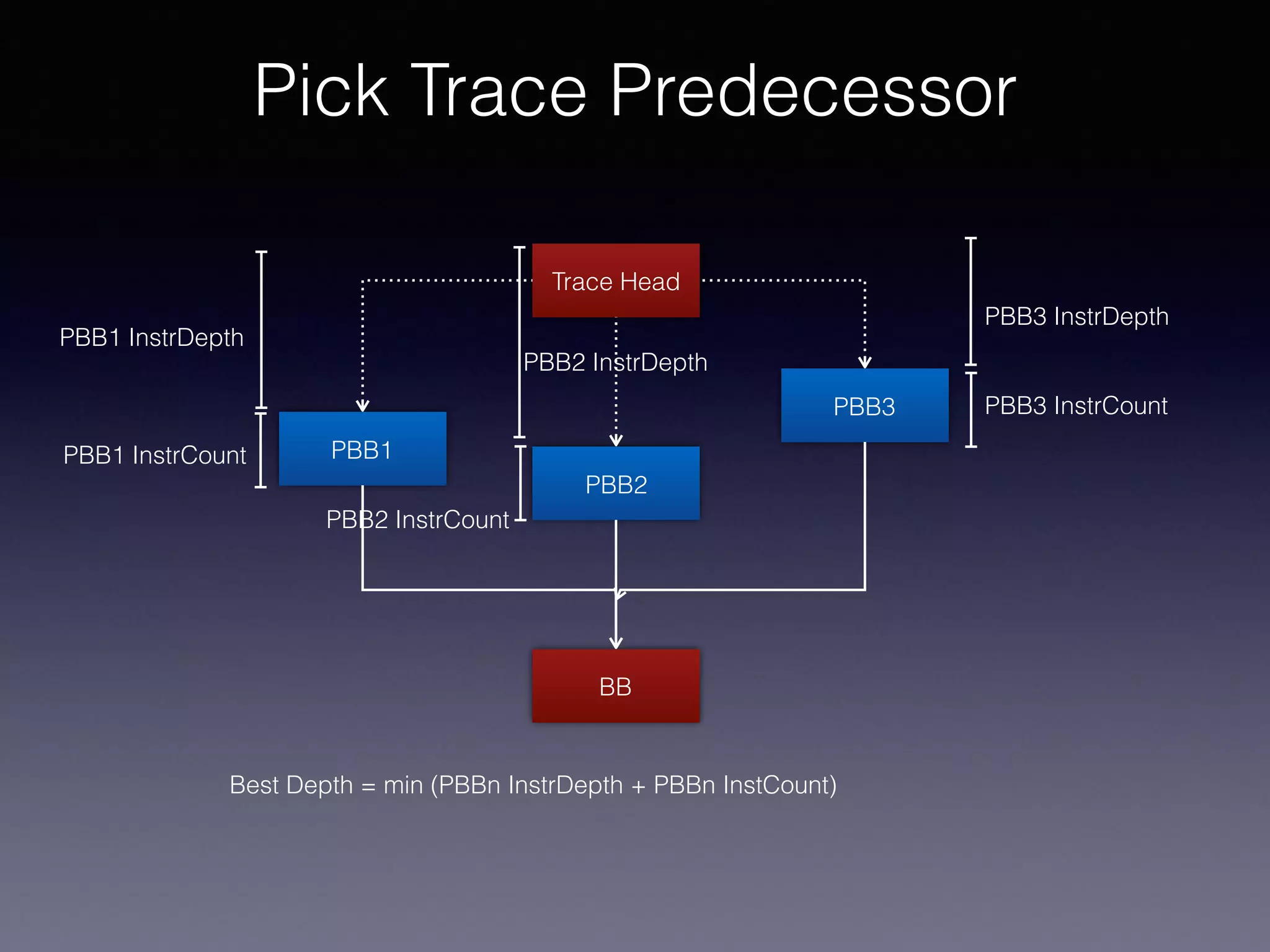

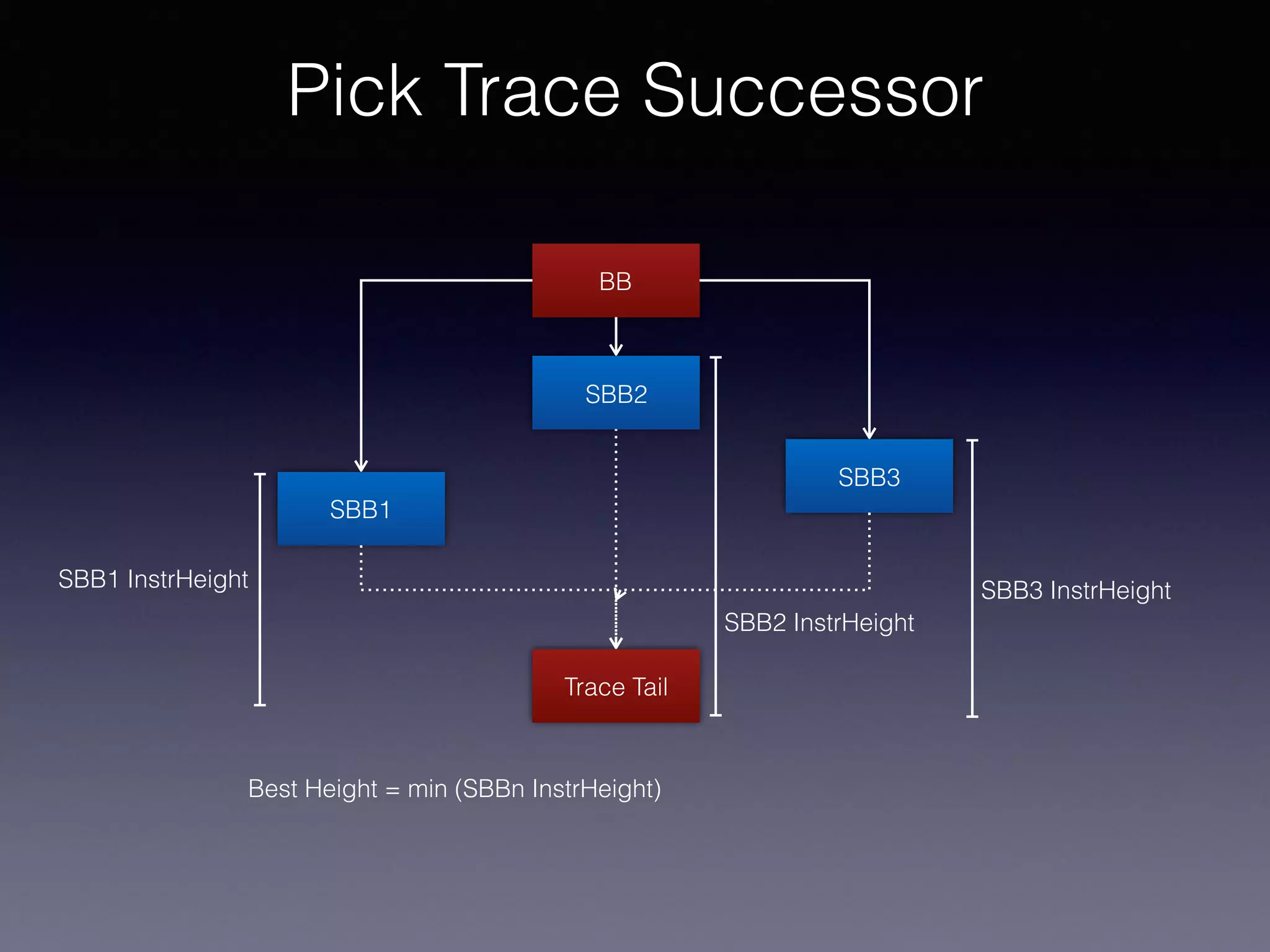

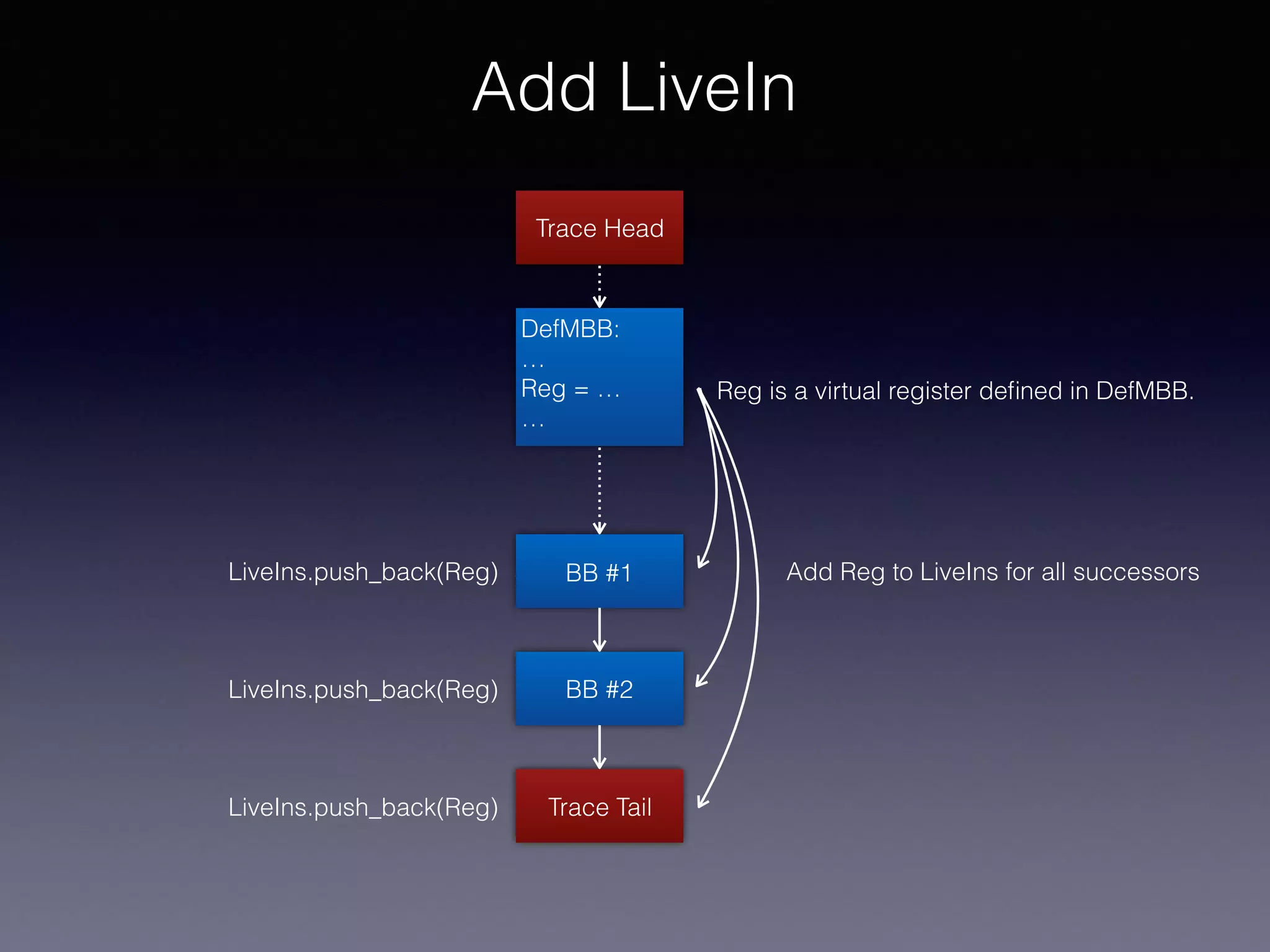

2. Key steps include finding the best predecessor and successor blocks for each block, computing depth and height values bottom-up and top-down based on dependency latencies, and tracking register liveness across blocks to determine the overall critical path.

![ProcResourceCycles (PRKinds = 5)

PRCycles

block 0

block 1

ProcResourceIdx

The number of cycles consumed by

block B on processor resource R is at

ProcResourceCycles[B x Kinds + R]

Processor Resources Cycles](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-3-2048.jpg)

![• Inverse post-order traversal of predecessors.

• Call pickTracePred() to find the best predecessor.

• Compute depth resources

• TraceBlockInfo

• instruction depth, trace head, etc.

• ProcResourceDepths[]

• cycles count for each processor resources from trace head to the basic block, does

not include cycles in the basic block.

• Post-order traversal of successors.

• Call pickTraceSucc() to find the best successor.

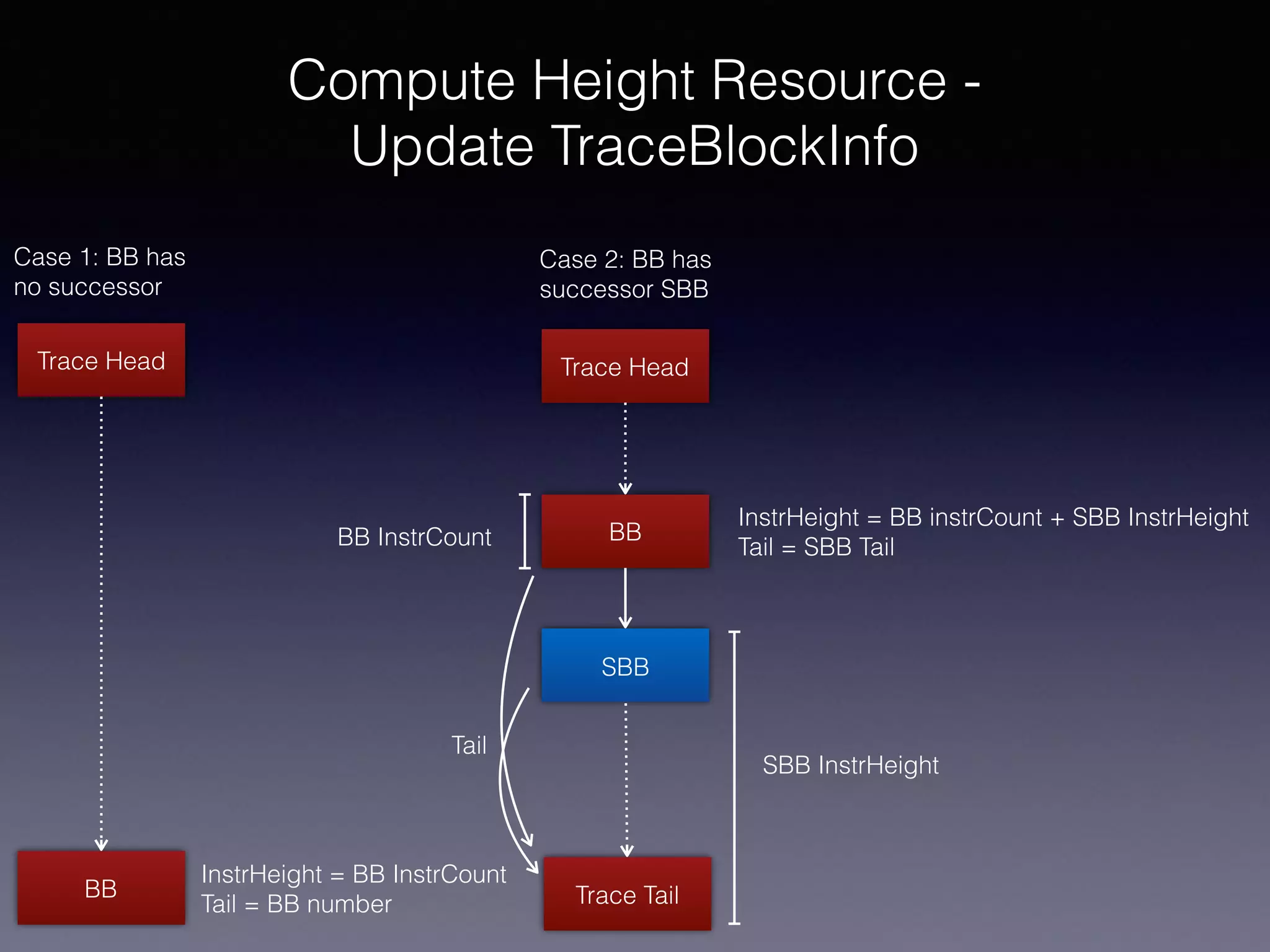

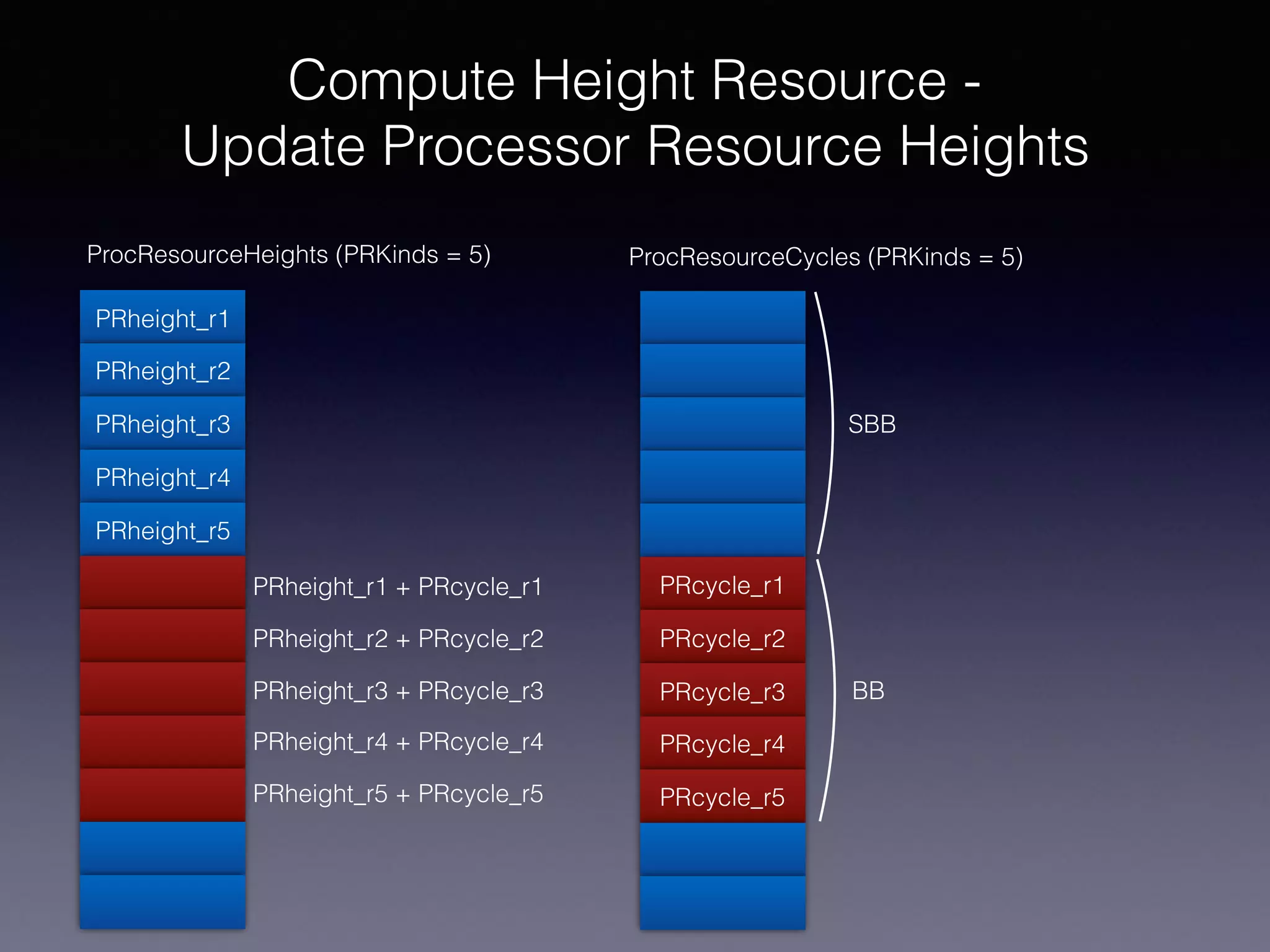

• Compute height resources

• TraceBlockInfo

• instruction height, trace tail, etc.

• ProcResourceHeights[]

• cycles count for each processor resources from the basic block to trace tail, including

cycles in the basic block.

Compute Trace for Basic Block](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-11-2048.jpg)

![MIHeightMap & RegUnits

…

MI: DefOp, UseOp1, UseOp2

…

I: DefOp2, DefOp, …

…

DefOp.Cycle (Height of I)

Latency of DefOp (MI, I)

Height = Latency + DefOp.Cycle

// UseOp2 is a physical register.

RegUnits[UseOp2].Cycle = max (RegUnits[UseOp2].Cycle, Height)

RegUnits[UseOp2].MI = MI

RegUnits[UseOp2[.Op = 2

Trace Tail

…

DI: UseOp1, …

…

Data

dependency

(DI, 0, 1)

UseOp1 is virtual register

DefOp is physical register

Latency of UseOp1 (DI, MI)

MIHeightMap.insert (DI, Latency of UseOp1 + Latency of DefOp + DefOp.Cycle)](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-14-2048.jpg)

![MIHeightMap & RegUnits

…

MI: DefOp, UseOp1, UseOp2

…

I: DefOp2, DefOp, …

…

DefOp.Cycle (Height of I)

Latency of DefOp (MI, I)

Height = Latency + DefOp.Cycle

// UseOp2 is a physical register.

RegUnits[UseOp2].Cycle = max (RegUnits[UseOp2].Cycle, Height)

RegUnits[UseOp2].MI = MI

RegUnits[UseOp2[.Op = 2

Trace Tail

…

DI: UseOp1, …

…

Data

dependency

(DI, 0, 1)

DefOp is physical register

Latency of UseOp1 (DI, MI)

MIHeightMap.insert (DI, Latency of UseOp1 + Latency of DefOp + DefOp.Cycle)

Computed by updatePhysDepsUpwards()

UseOp1 is virtual register](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-15-2048.jpg)

![MIHeightMap & RegUnits

…

MI: DefOp, UseOp1, UseOp2

…

I: DefOp2, DefOp, …

…

DefOp.Cycle (Height of I)

Latency of DefOp (MI, I)

Height = Latency + DefOp.Cycle

// UseOp2 is a physical register.

RegUnits[UseOp2].Cycle = max (RegUnits[UseOp2].Cycle, Height)

RegUnits[UseOp2].MI = MI

RegUnits[UseOp2[.Op = 2

Trace Tail

…

DI: UseOp1, …

…

Data

dependency

(DI, 0, 1)

DefOp is physical register

Latency of UseOp1 (DI, MI)

MIHeightMap.insert (DI, Latency of UseOp1 + Latency of DefOp + DefOp.Cycle)

Computed by getDataDep()

UseOp1 is virtual register](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-16-2048.jpg)

![MIHeightMap & RegUnits

…

MI: DefOp, UseOp1, UseOp2

…

I: DefOp2, DefOp, …

…

DefOp.Cycle (Height of I)

Latency of DefOp (MI, I)

Height = Latency + DefOp.Cycle

// UseOp2 is a physical register.

RegUnits[UseOp2].Cycle = max (RegUnits[UseOp2].Cycle, Height)

RegUnits[UseOp2].MI = MI

RegUnits[UseOp2[.Op = 2

Trace Tail

…

DI: UseOp1, …

…

Data

dependency

(DI, 0, 1)

DefOp is physical register

Latency of UseOp1 (DI, MI)

MIHeightMap.insert (DI, Latency of UseOp1 + Latency of DefOp + DefOp.Cycle)

Computed by pushDepHeight()

UseOp1 is virtual register

MIHeightMap[MI] or

computed by

updatePhysDepsUp

wards() if MI

contains physical

registers](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-17-2048.jpg)

![Compute Instruction Depth

BB

Trace Head

BB #2

BB #1:

…

UseMI…

for all instruction UseMI in BB #1:

for all data dependency:

Cycle = max (Cycles[DefMI].Depth + Latency (DefMI, UseMI))

Has valid

instruction Depth.

compute

instruction depth

from BB #1.

Critical path length for basic block is

maximum of Cycles[MI].Depth + Cycles[MI].Height for all

instructions MI in basic block.

…

DefMI…

data dependency

Latency of (DefMI, UseMI)

Cycles[DefMI].Depth

Cycles[UseMI].Depth = Cycle](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-18-2048.jpg)

![Compute Instruction Depth

BB

Trace Head

BB #2

BB #1:

…

UseMI…

for all instruction UseMI in BB #1:

for all data dependency:

Cycle = max (Cycles[DefMI].Depth + Latency (DefMI, UseMI))

Has valid

instruction Depth.

compute

instruction depth

from BB #1.

Critical path length for basic block is

maximum of Cycles[MI].Depth + Cycles[MI].Height for all

instructions MI in basic block.

…

DefMI…

data dependency

Latency of (DefMI, UseMI)

Cycles[DefMI].Depth

Cycles[UseMI].Depth = Cycle

1. Get data dependency](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-19-2048.jpg)

![Compute Instruction Depth

BB

Trace Head

BB #2

BB #1:

…

UseMI…

for all instruction UseMI in BB #1:

for all data dependency:

Cycle = max (Cycles[DefMI].Depth + Latency (DefMI, UseMI))

Has valid

instruction Depth.

compute

instruction depth

from BB #1.

Critical path length for basic block is

maximum of Cycles[MI].Depth + Cycles[MI].Height for all

instructions MI in basic block.

…

DefMI…

data dependency

Latency of (DefMI, UseMI)

Cycles[DefMI].Depth

Cycles[UseMI].Depth = Cycle

2. Calculate UseMI’s cycle](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-20-2048.jpg)

![Compute Instruction Depth

BB

Trace Head

BB #2

BB #1:

…

UseMI…

for all instruction UseMI in BB #1:

for all data dependency:

Cycle = max (Cycles[DefMI].Depth + Latency (DefMI, UseMI))

Has valid

instruction Depth.

compute

instruction depth

from BB #1.

Critical path length for basic block is

maximum of Cycles[MI].Depth + Cycles[MI].Height for all

instructions MI in basic block.

…

DefMI…

data dependency

Latency of (DefMI, UseMI)

Cycles[DefMI].Depth

Cycles[UseMI].Depth = Cycle

3. Update UseMI’s Depth](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-21-2048.jpg)

![Compute Instruction Height

Trace Tail

BB

BB #2

BB #1:

MI…

Has valid

instruction Height.

Succ

compute through

the trace blocks in

bottom-up order

if MI has no physical registers:

Cycle = Heights[MI]

else

Cycle = updatePhysDepsUpwards()

update Heights

according to data

dependency

Cycles[MI].Height = Cycle

if LiveInReg is virtual register:

LiveInReg.Height = Heights[DefMI]

if LiveInReg is physical register

LiveInReg.Height = RegUnit.Cycle](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-22-2048.jpg)

![Compute Instruction Height

Trace Tail

BB

BB #2

BB #1:

MI…

Has valid

instruction Height.

Succ

compute through

the trace blocks in

bottom-up order

if MI has no physical registers:

Cycle = Heights[MI]

else

Cycle = updatePhysDepsUpwards()

update Heights

according to data

dependency

Cycles[MI].Height = Cycle

if LiveInReg is virtual register:

LiveInReg.Height = Heights[DefMI]

if LiveInReg is physical register

LiveInReg.Height = RegUnit.Cycle

1. Get data dependency](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-23-2048.jpg)

![Compute Instruction Height

Trace Tail

BB

BB #2

BB #1:

MI…

Has valid

instruction Height.

Succ

compute through

the trace blocks in

bottom-up order

if MI has no physical registers:

Cycle = Heights[MI]

else

Cycle = updatePhysDepsUpwards()

update Heights

according to data

dependency

Cycles[MI].Height = Cycle

if LiveInReg is virtual register:

LiveInReg.Height = Heights[DefMI]

if LiveInReg is physical register

LiveInReg.Height = RegUnit.Cycle

2. Compute cycles of MI](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-24-2048.jpg)

![Compute Instruction Height

Trace Tail

BB

BB #2

BB #1:

MI…

Has valid

instruction Height.

Succ

compute through

the trace blocks in

bottom-up order

if MI has no physical registers:

Cycle = Heights[MI]

else

Cycle = updatePhysDepsUpwards()

update Heights

according to data

dependency

Cycles[MI].Height = Cycle

if LiveInReg is virtual register:

LiveInReg.Height = Heights[DefMI]

if LiveInReg is physical register

LiveInReg.Height = RegUnit.Cycle

3. Update Heights[]](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-25-2048.jpg)

![Compute Instruction Height

Trace Tail

BB

BB #2

BB #1:

MI…

Has valid

instruction Height.

Succ

compute through

the trace blocks in

bottom-up order

if MI has no physical registers:

Cycle = Heights[MI]

else

Cycle = updatePhysDepsUpwards()

update Heights

according to data

dependency

Cycles[MI].Height = Cycle

if LiveInReg is virtual register:

LiveInReg.Height = Heights[DefMI]

if LiveInReg is physical register

LiveInReg.Height = RegUnit.Cycle

4. Update MI’s Height](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-26-2048.jpg)

![Compute Instruction Height

Trace Tail

BB

BB #2

BB #1:

MI…

Has valid

instruction Height.

Succ

compute through

the trace blocks in

bottom-up order

if MI has no physical registers:

Cycle = Heights[MI]

else

Cycle = updatePhysDepsUpwards()

update Heights

according to data

dependency

Cycles[MI].Height = Cycle

if LiveInReg is virtual register:

LiveInReg.Height = Heights[DefMI]

if LiveInReg is physical register

LiveInReg.Height = RegUnit.Cycle

5. Update LiveInReg’s Height](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-27-2048.jpg)

![Compute Cross Block Critical Path

BB

LIR in BB’s LiveIns

…

LIR.Reg = … (DefMI)

…

Len = LIR.Height + Cycles[DefMI].Depth

for all LIR in LiveIns, the maximum of Len is critical

path length for the basic block BB.

LIR.Height:

Height of defining instruction

Trace Head Cycles[DefMI].Depth:

Earliest issue cycle as determined by data

dependencies and instruction latencies

from the beginning of the trace.

Trace Tail

LIR.Reg is a virtual register](https://image.slidesharecdn.com/machinetracemetrics-171225060820/75/Machine-Trace-Metrics-28-2048.jpg)