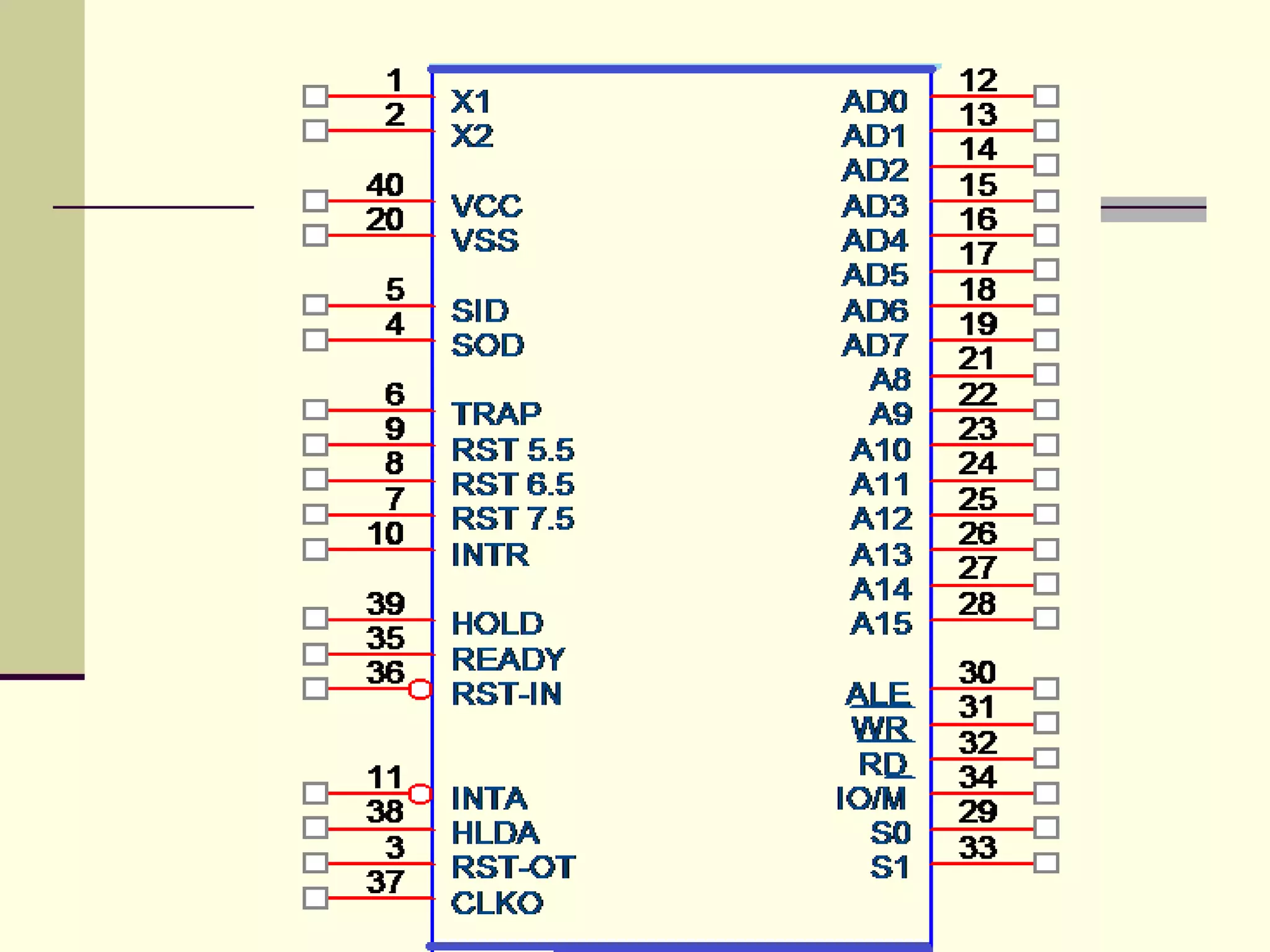

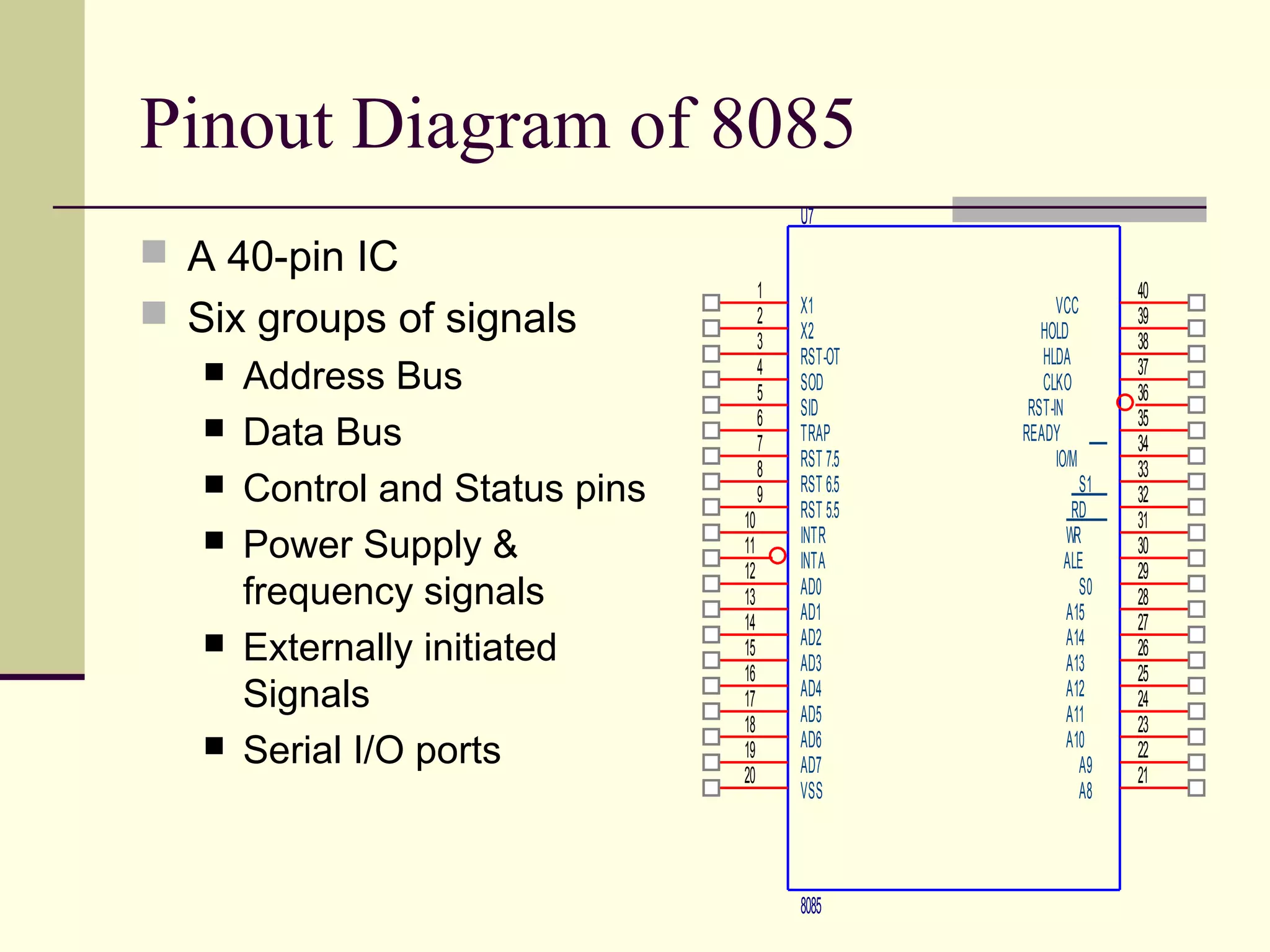

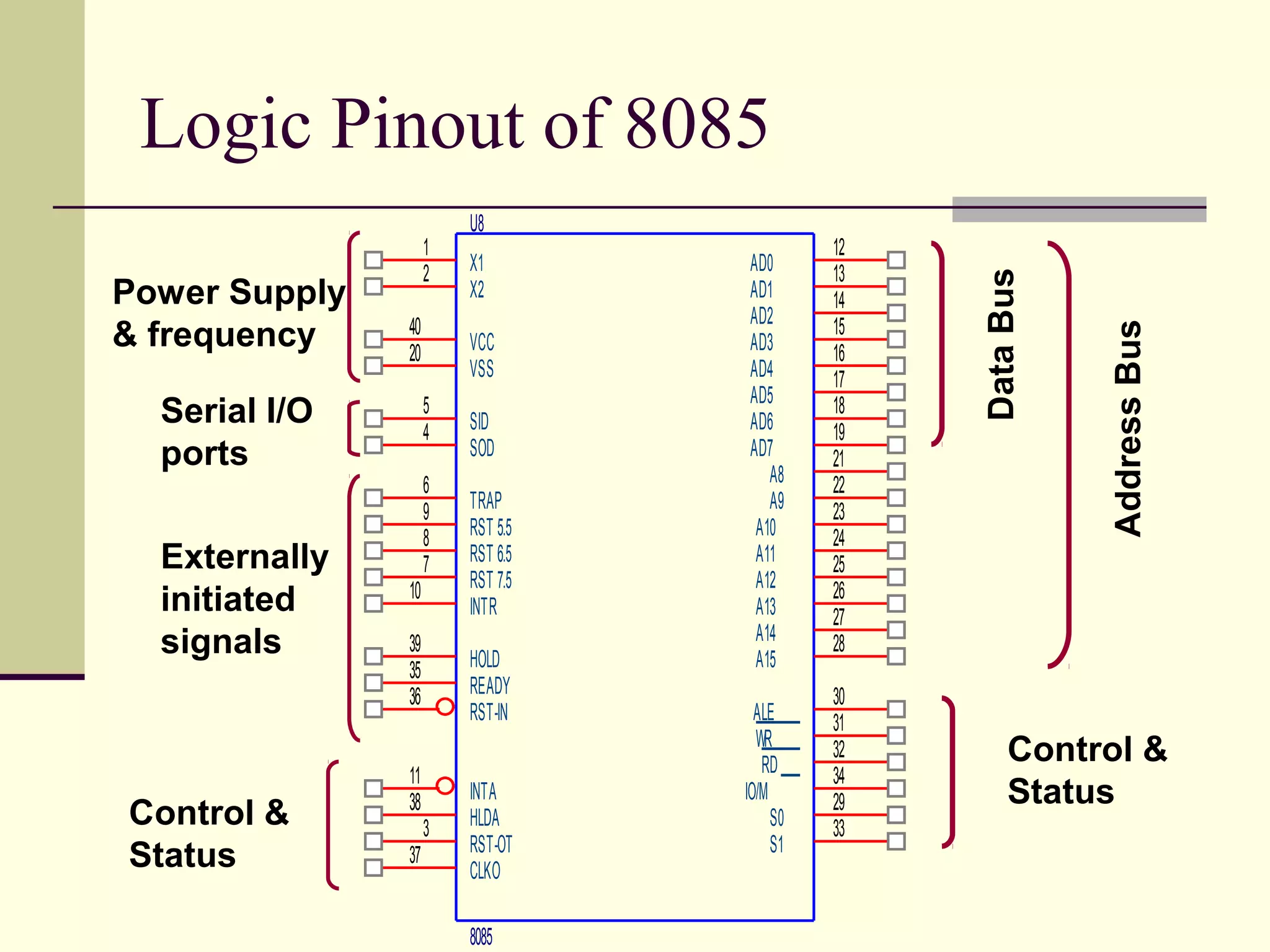

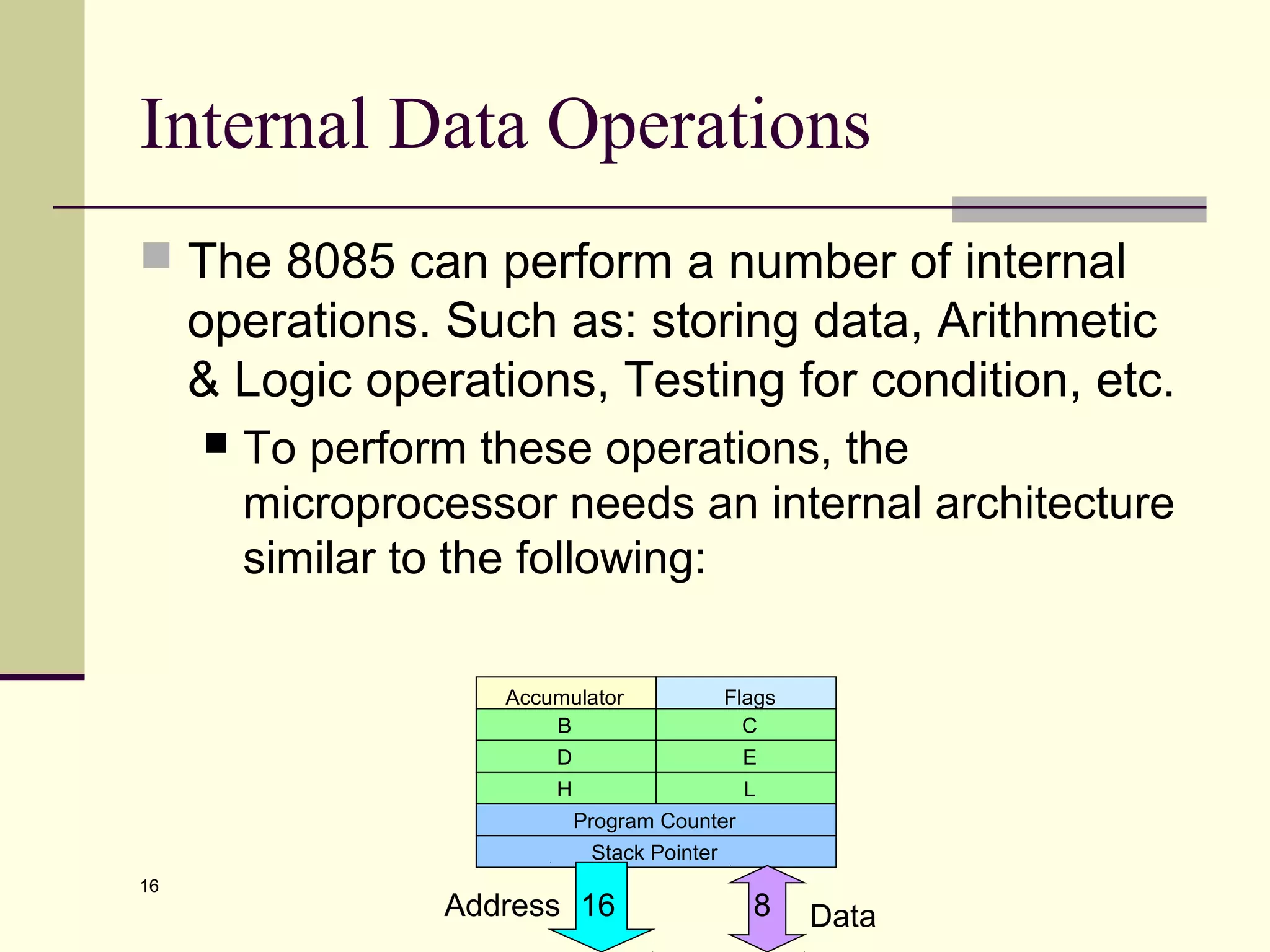

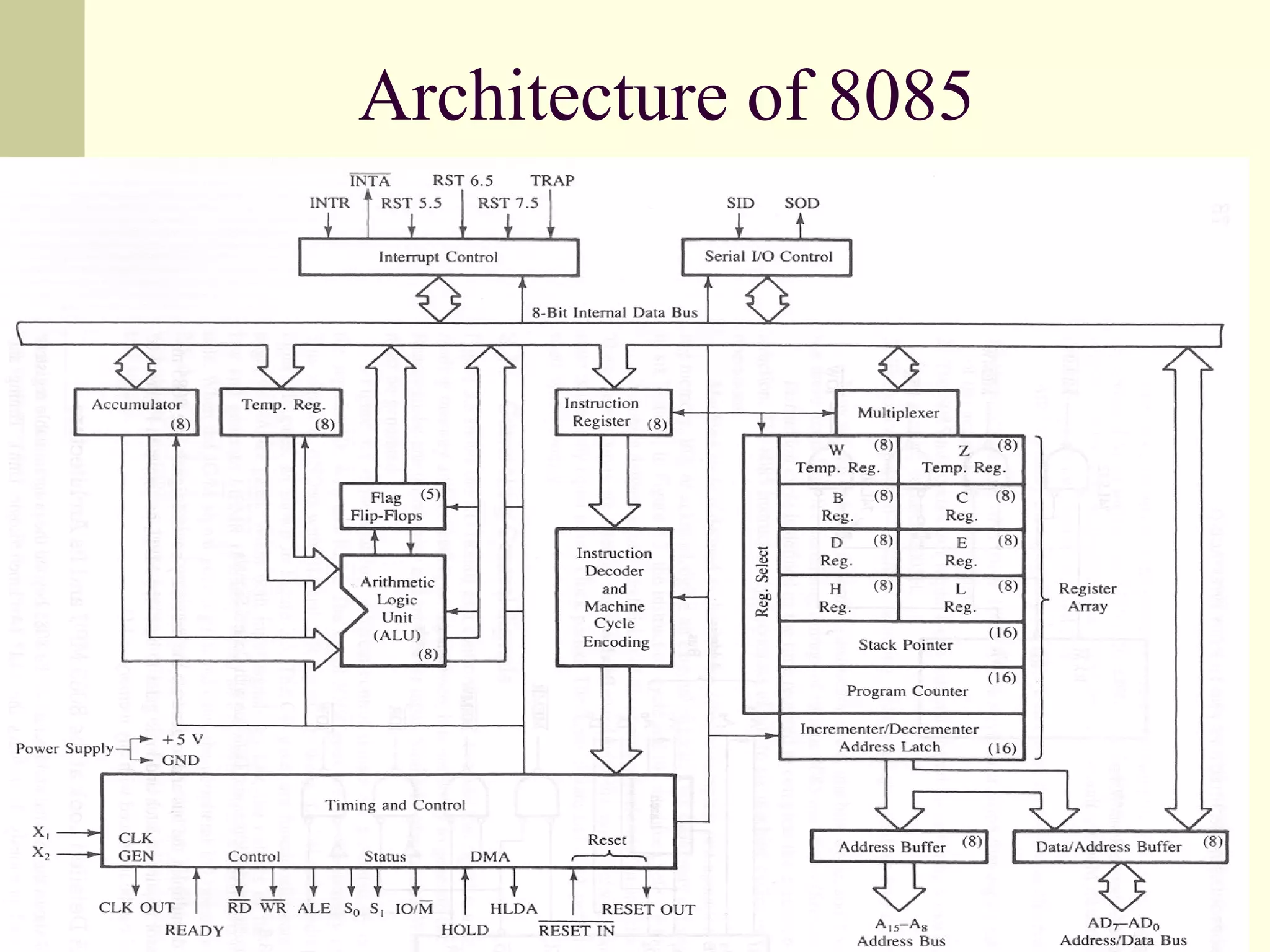

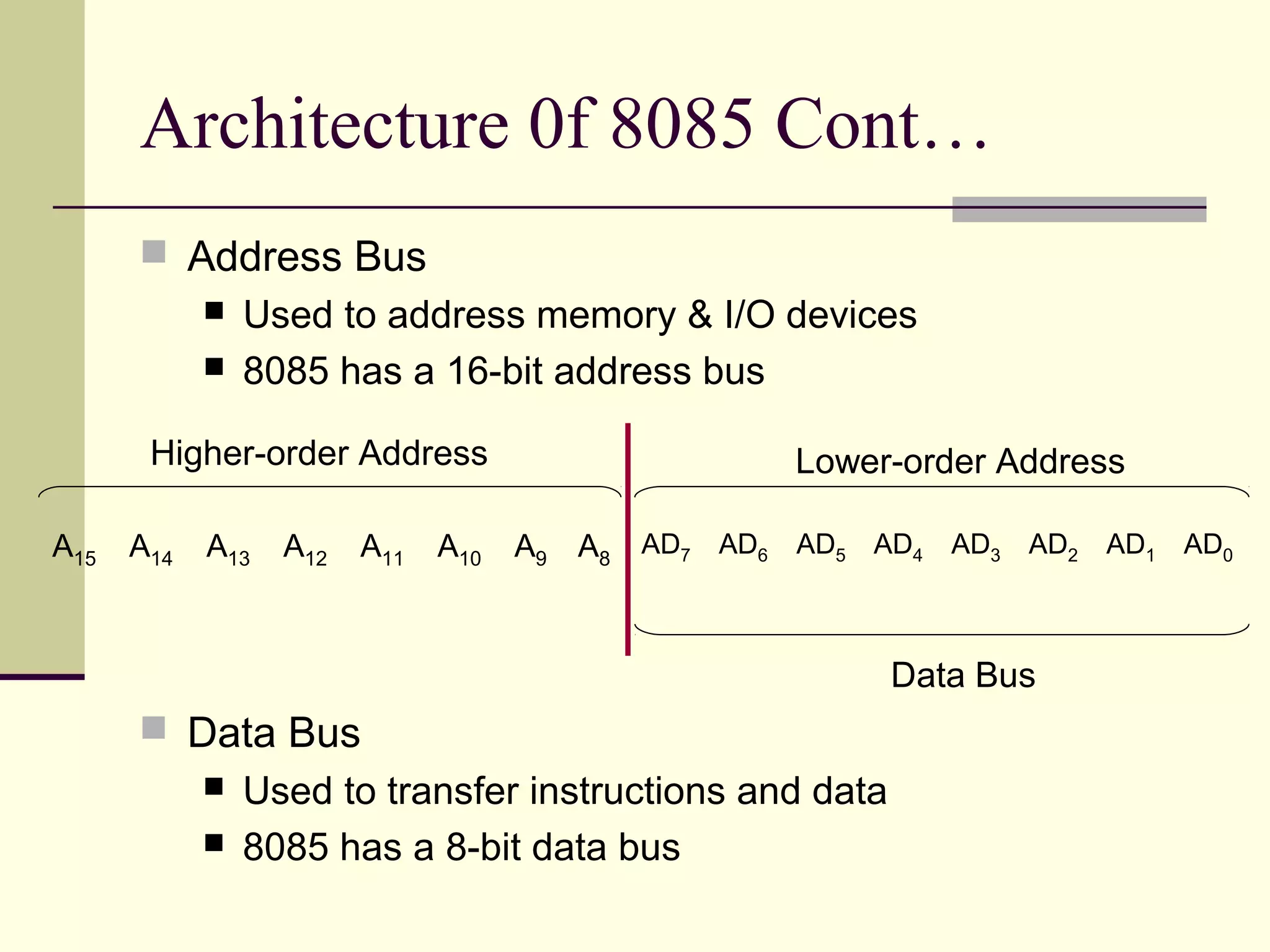

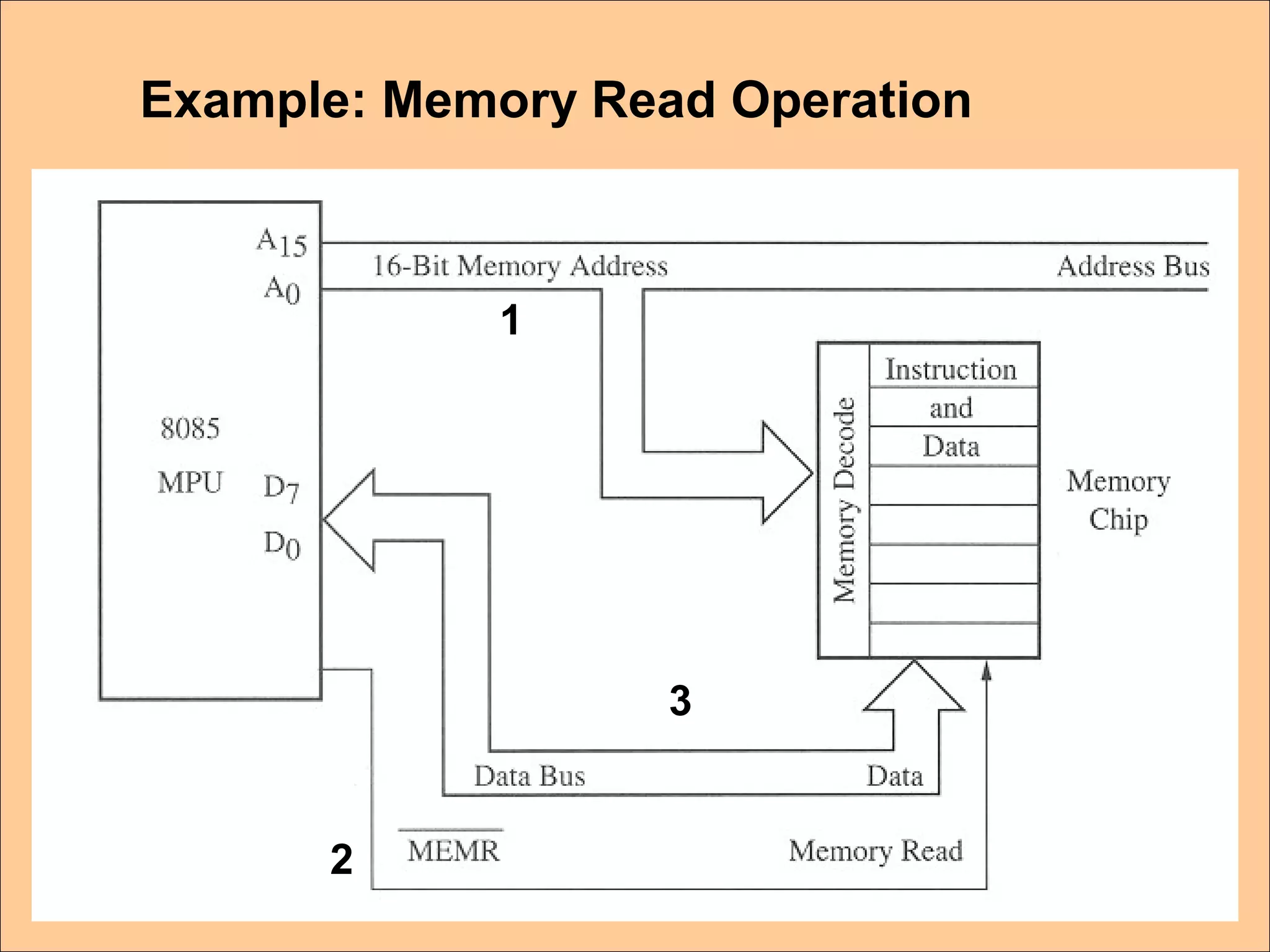

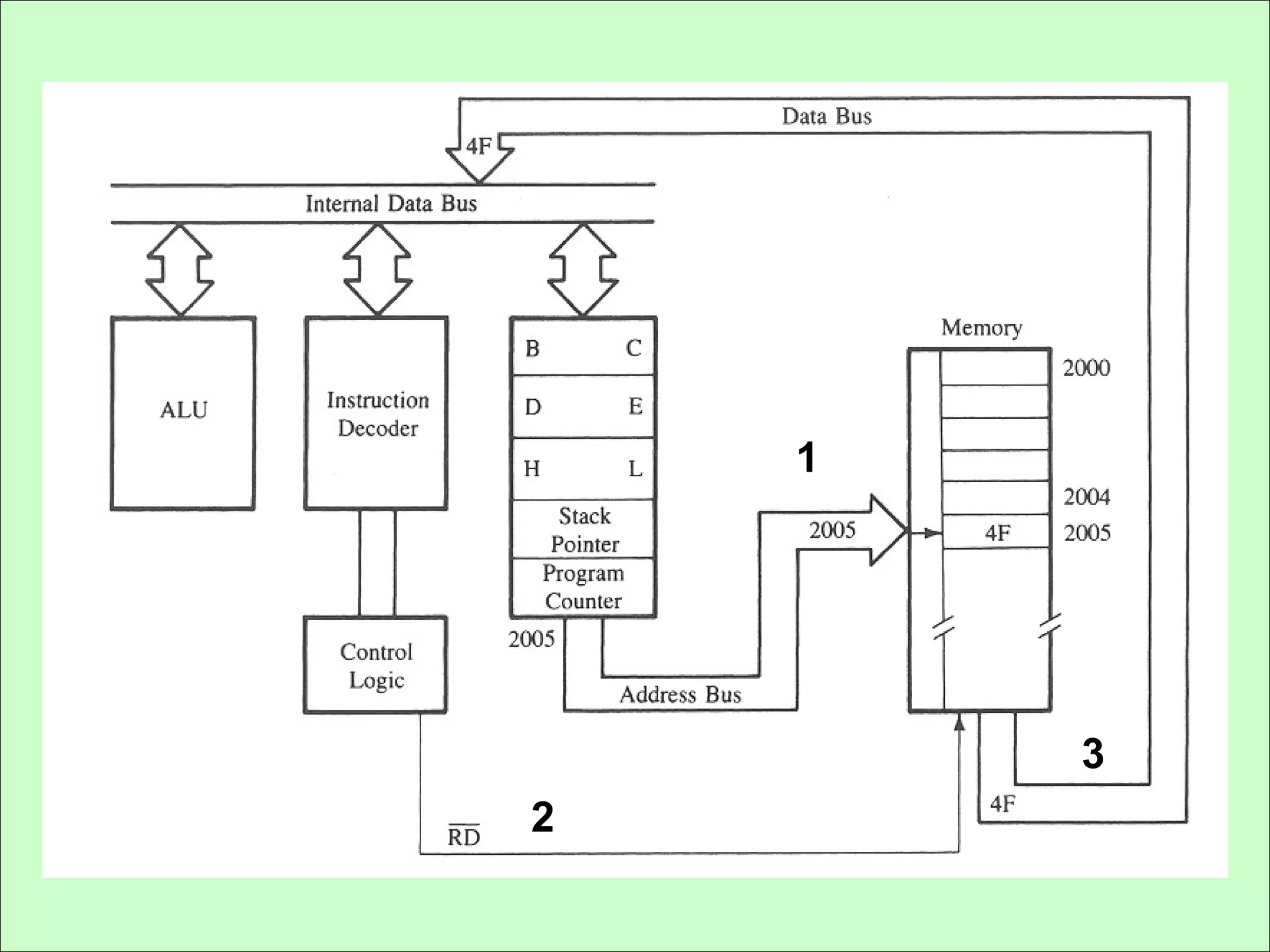

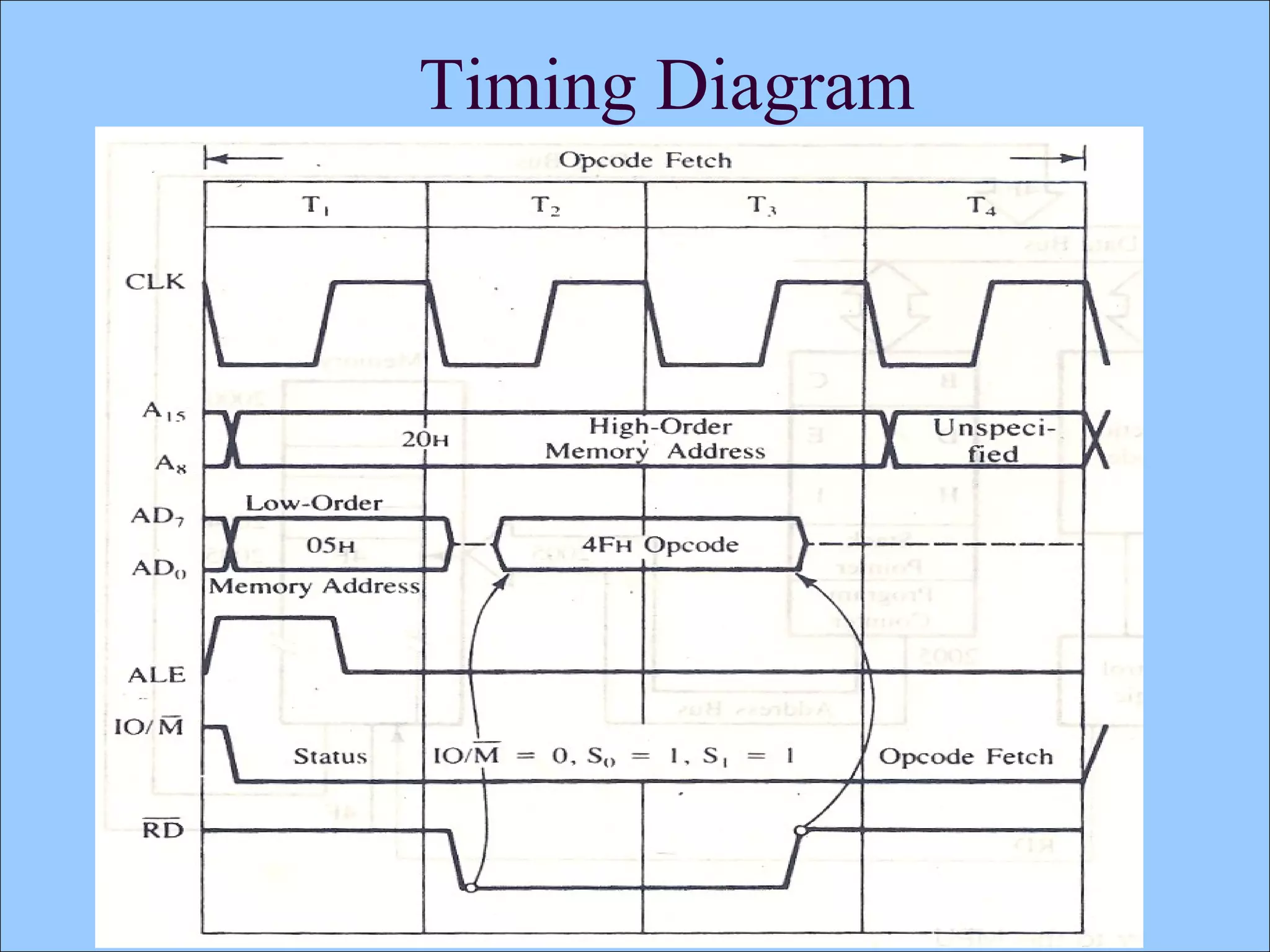

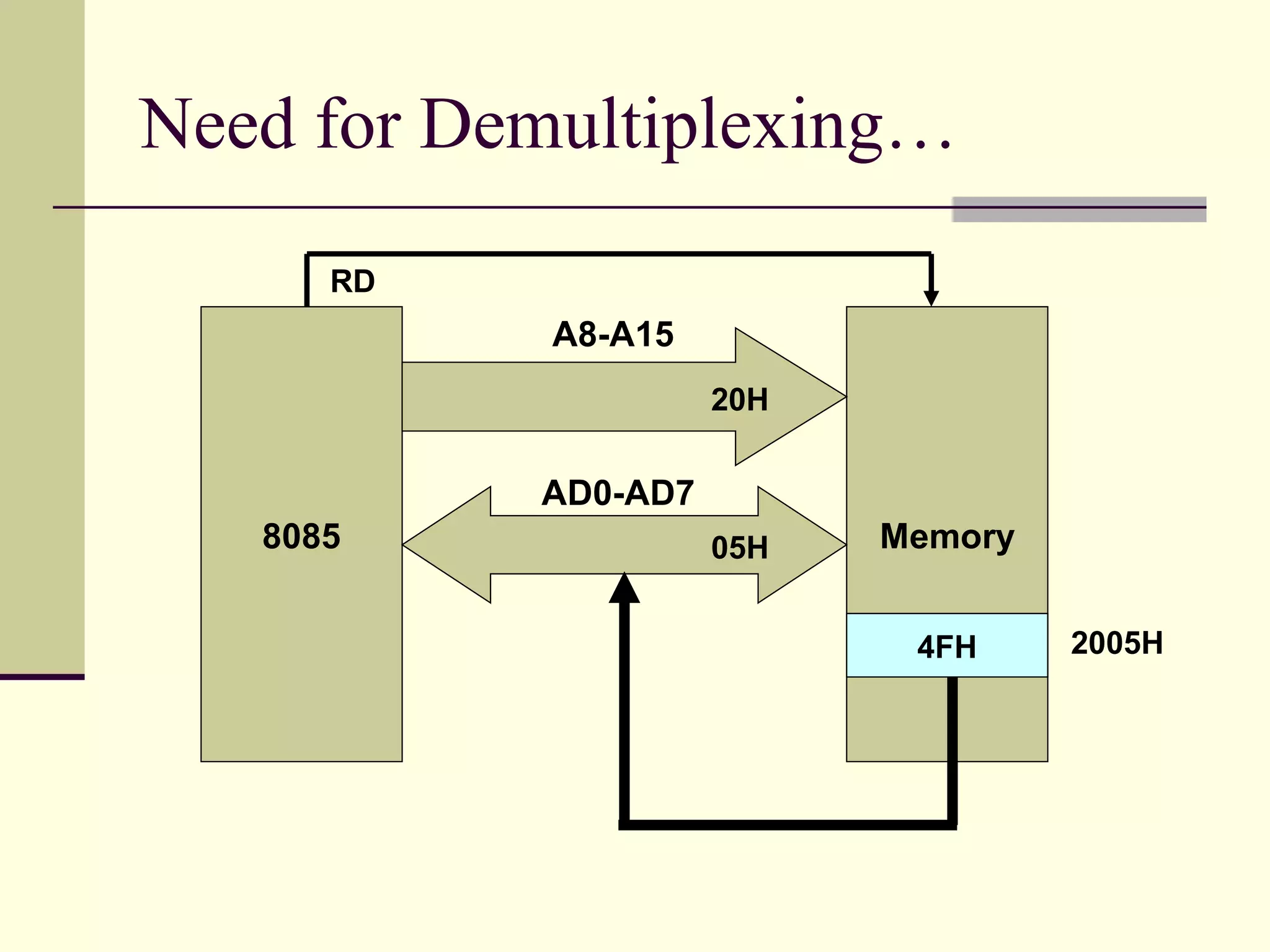

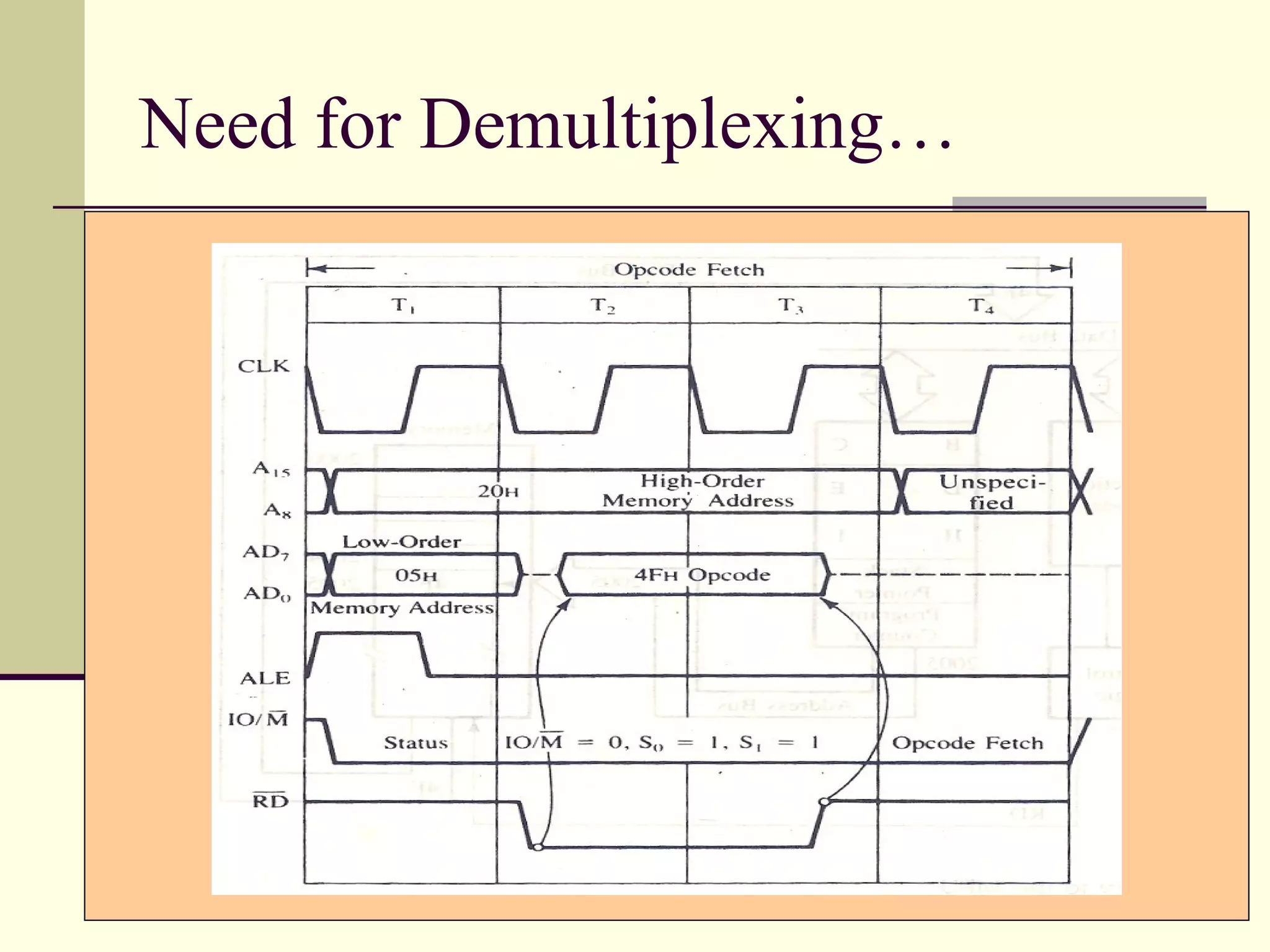

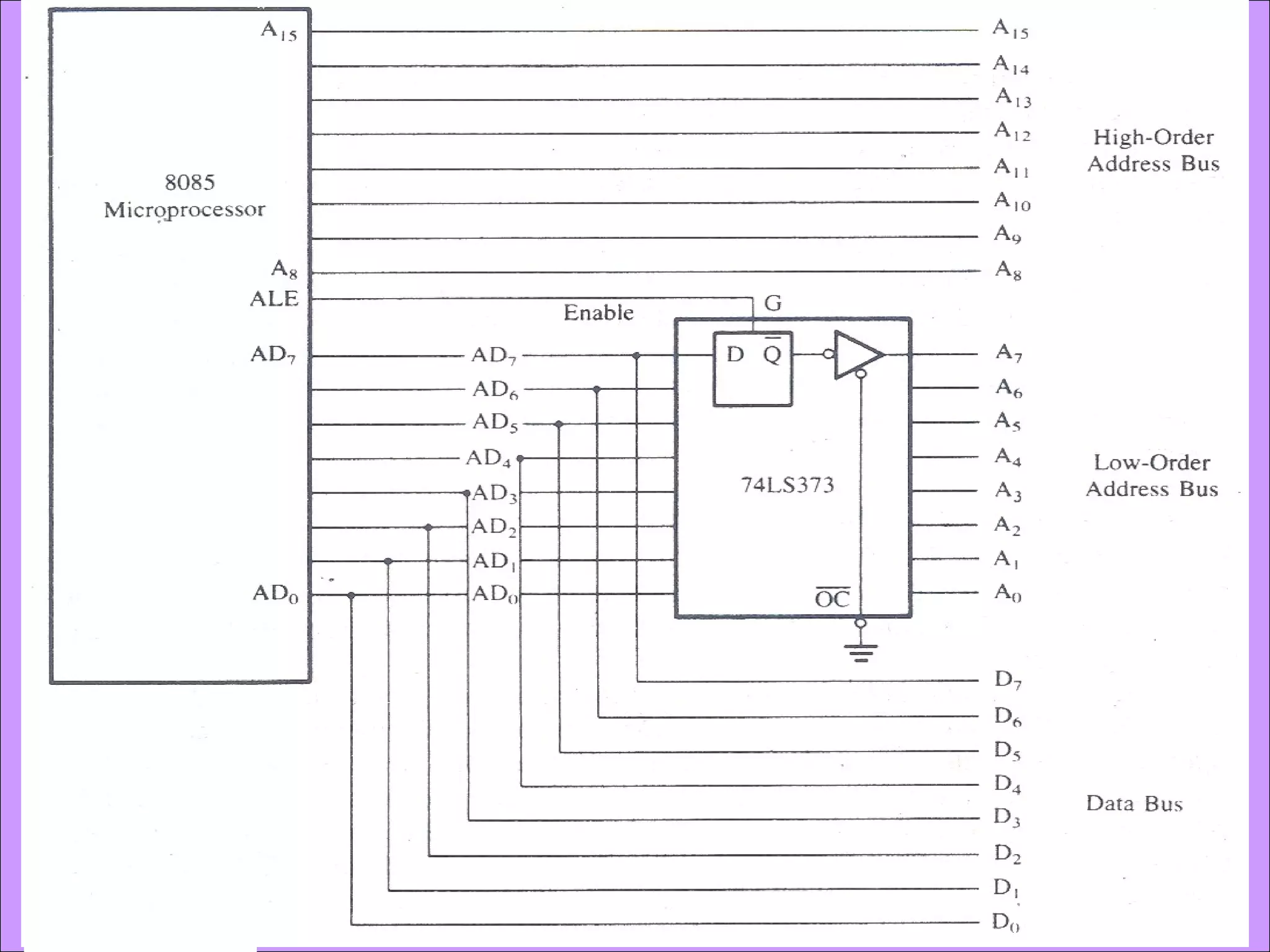

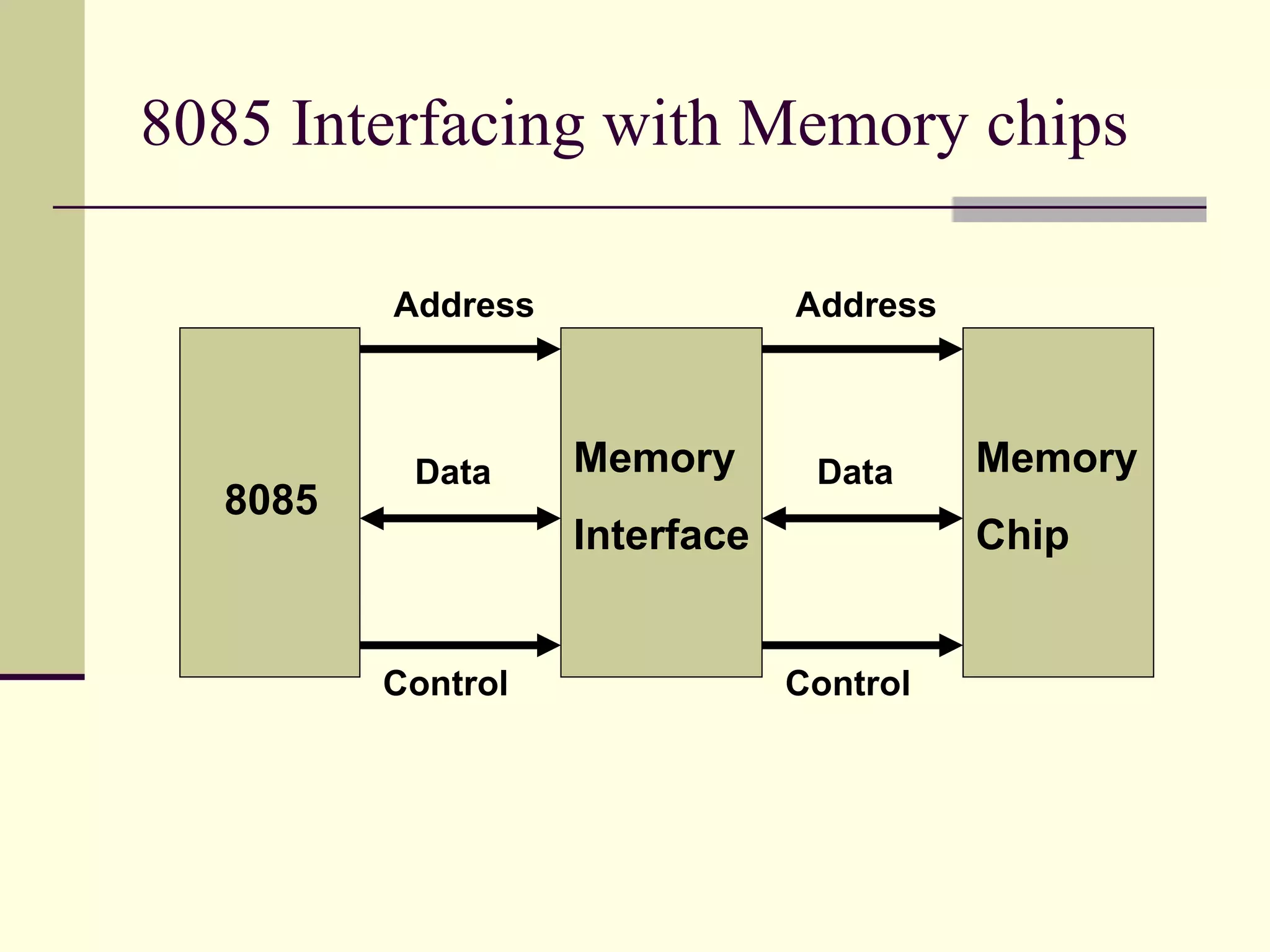

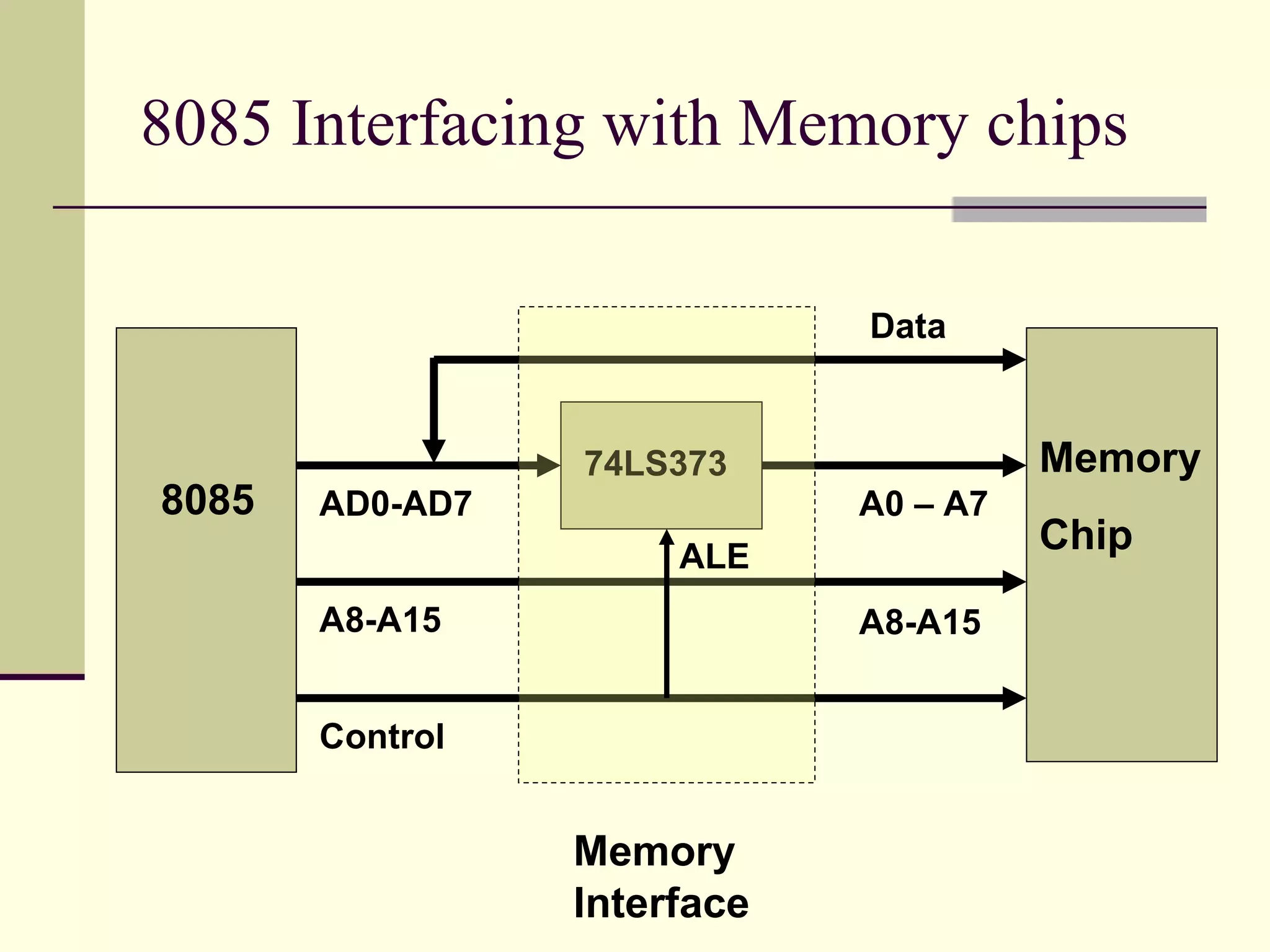

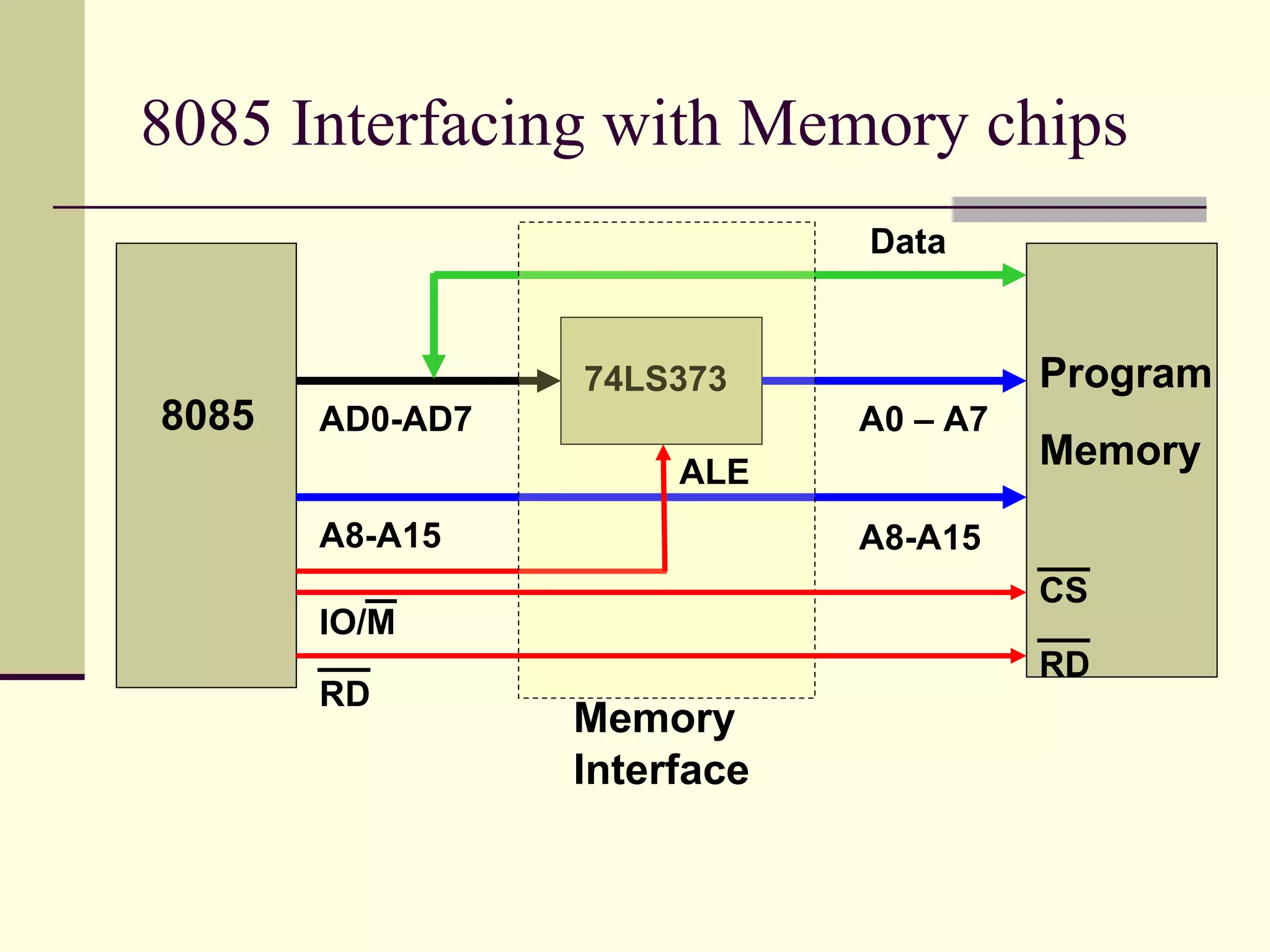

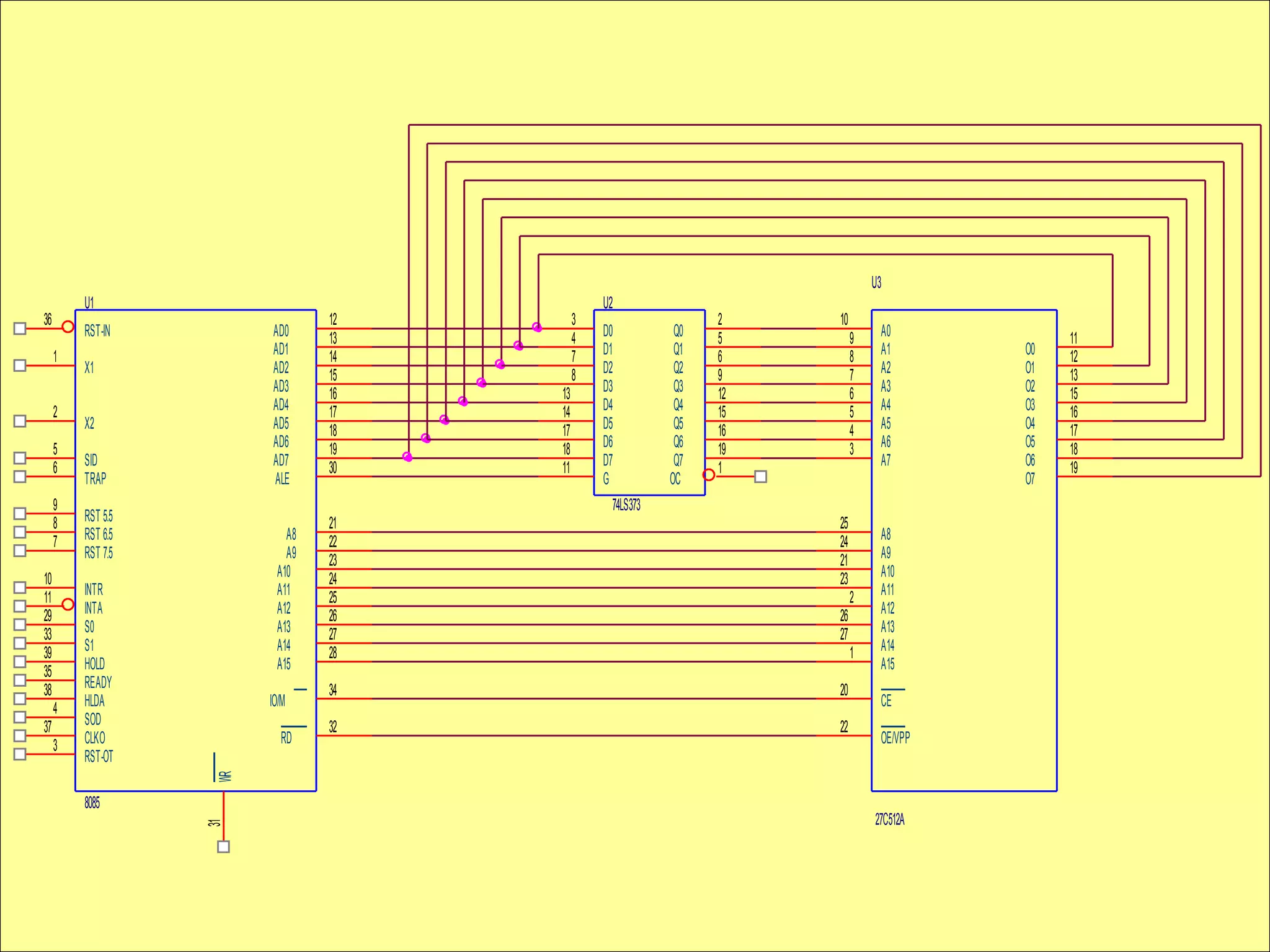

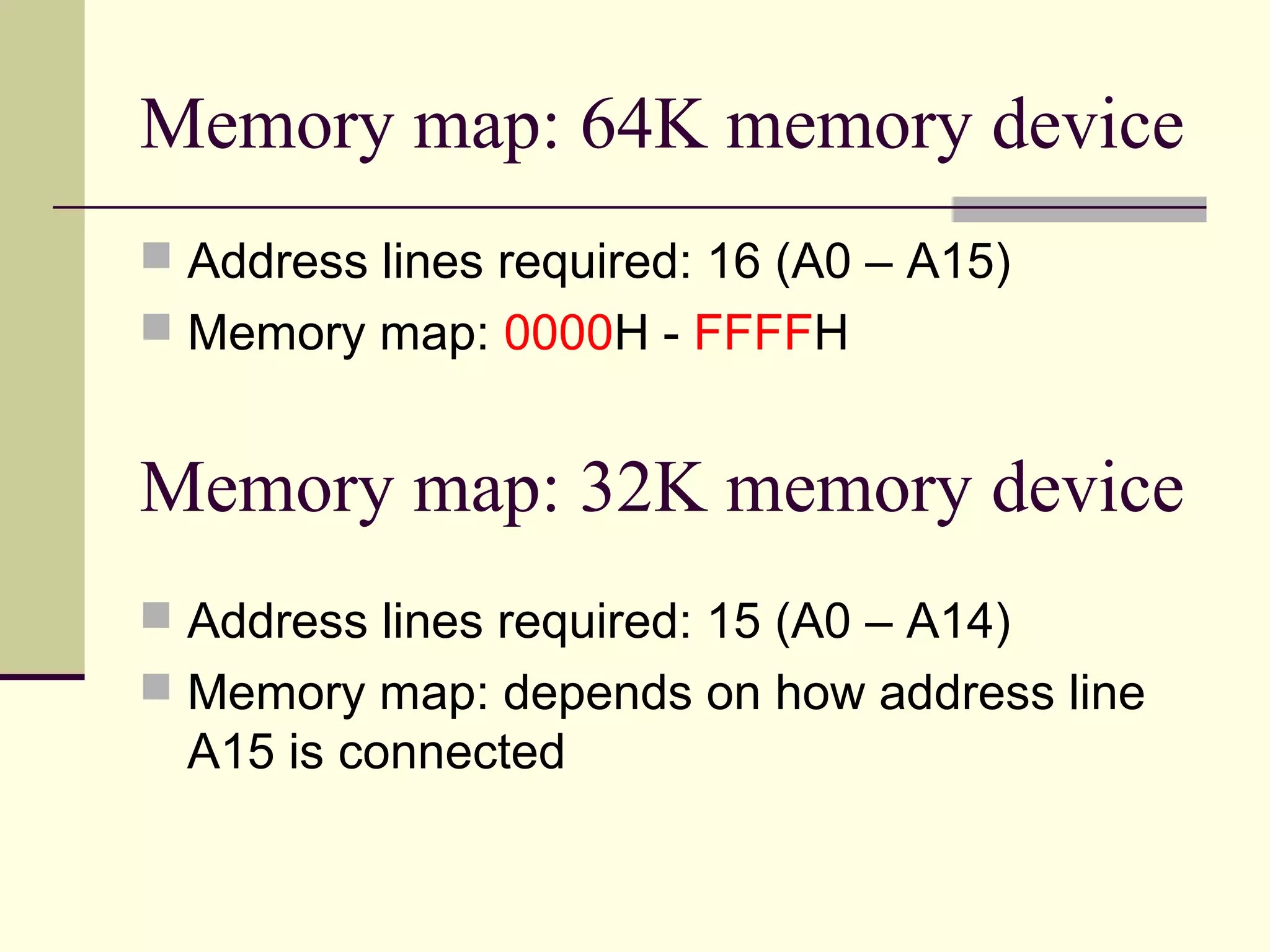

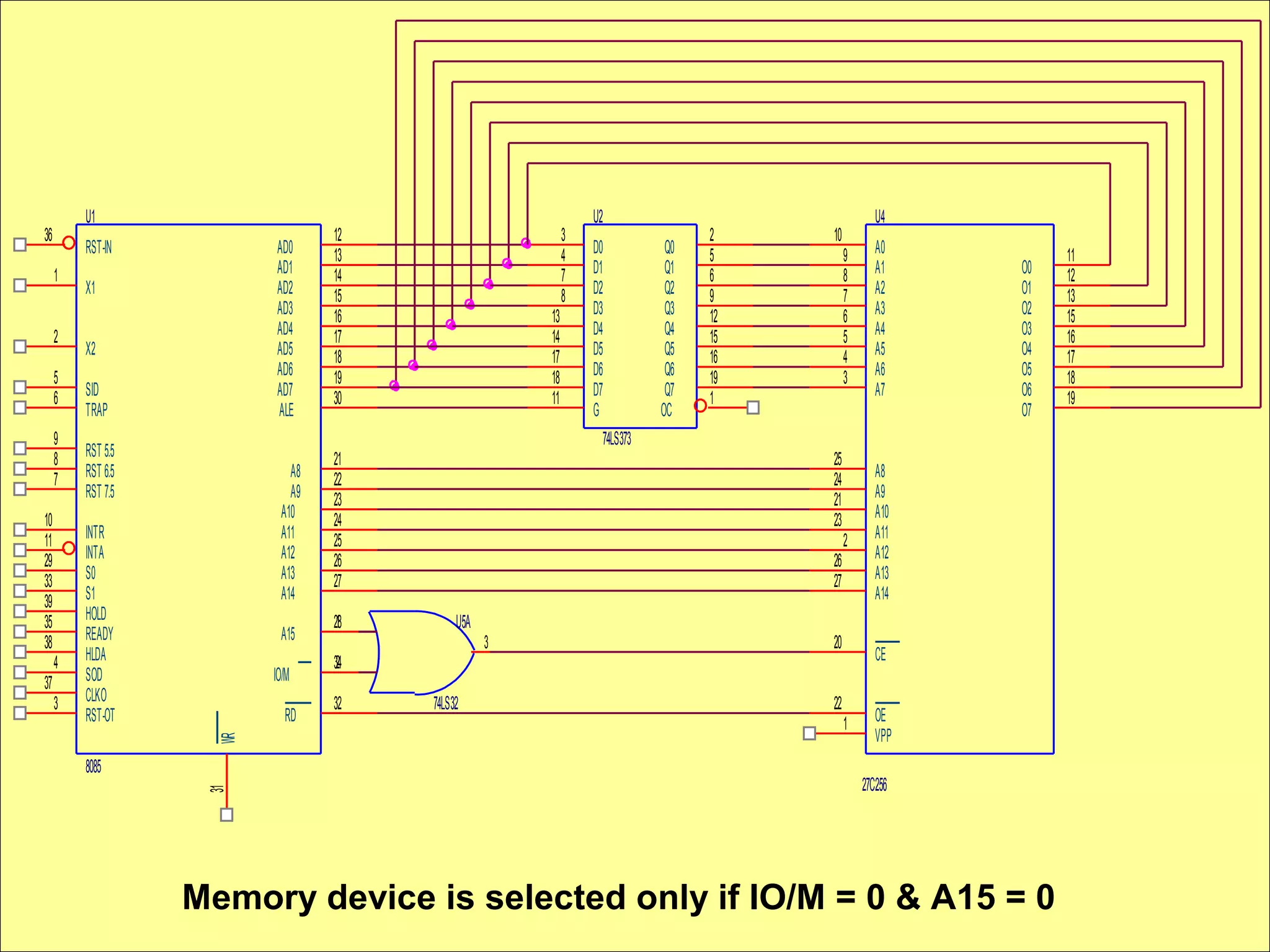

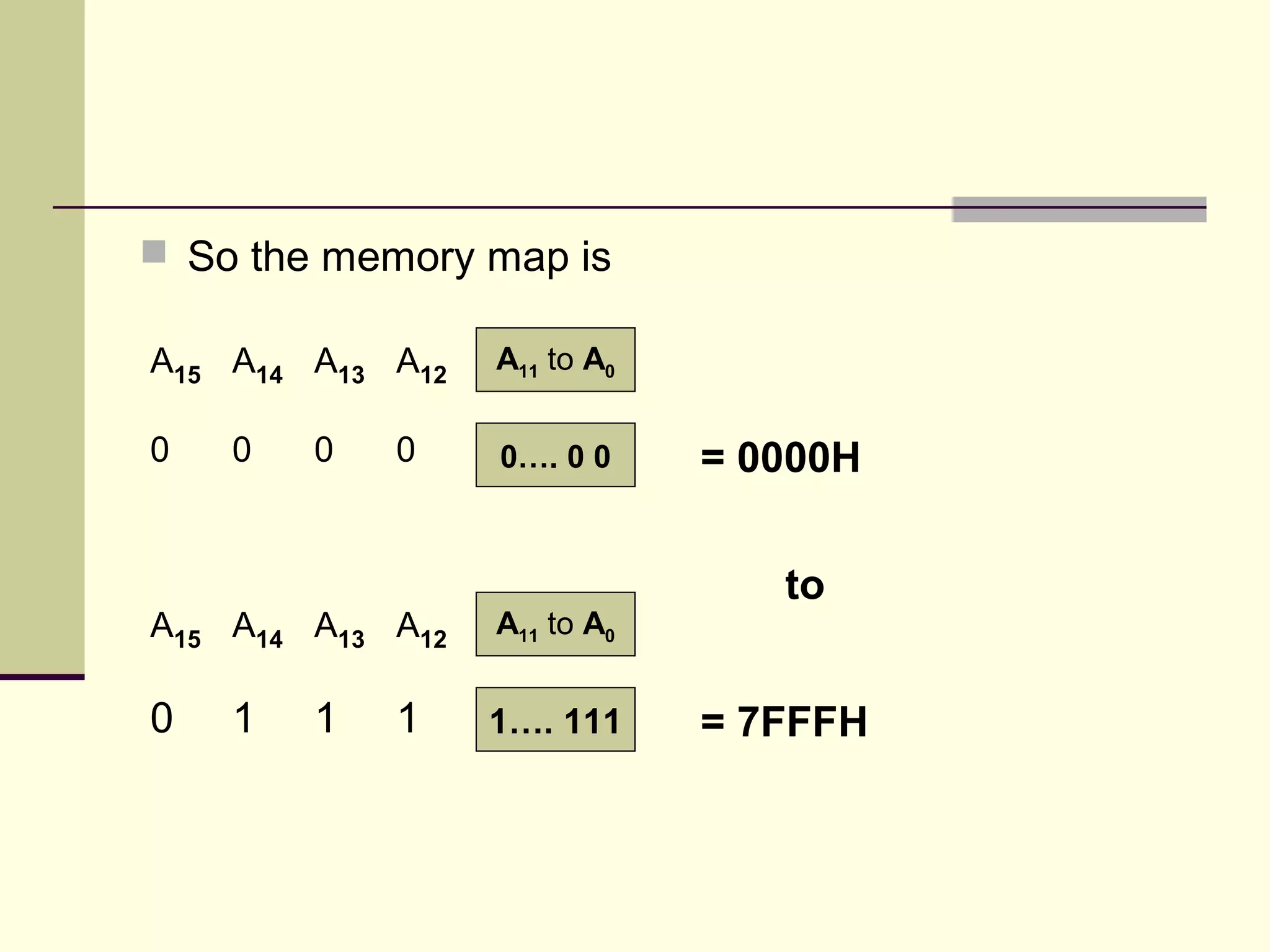

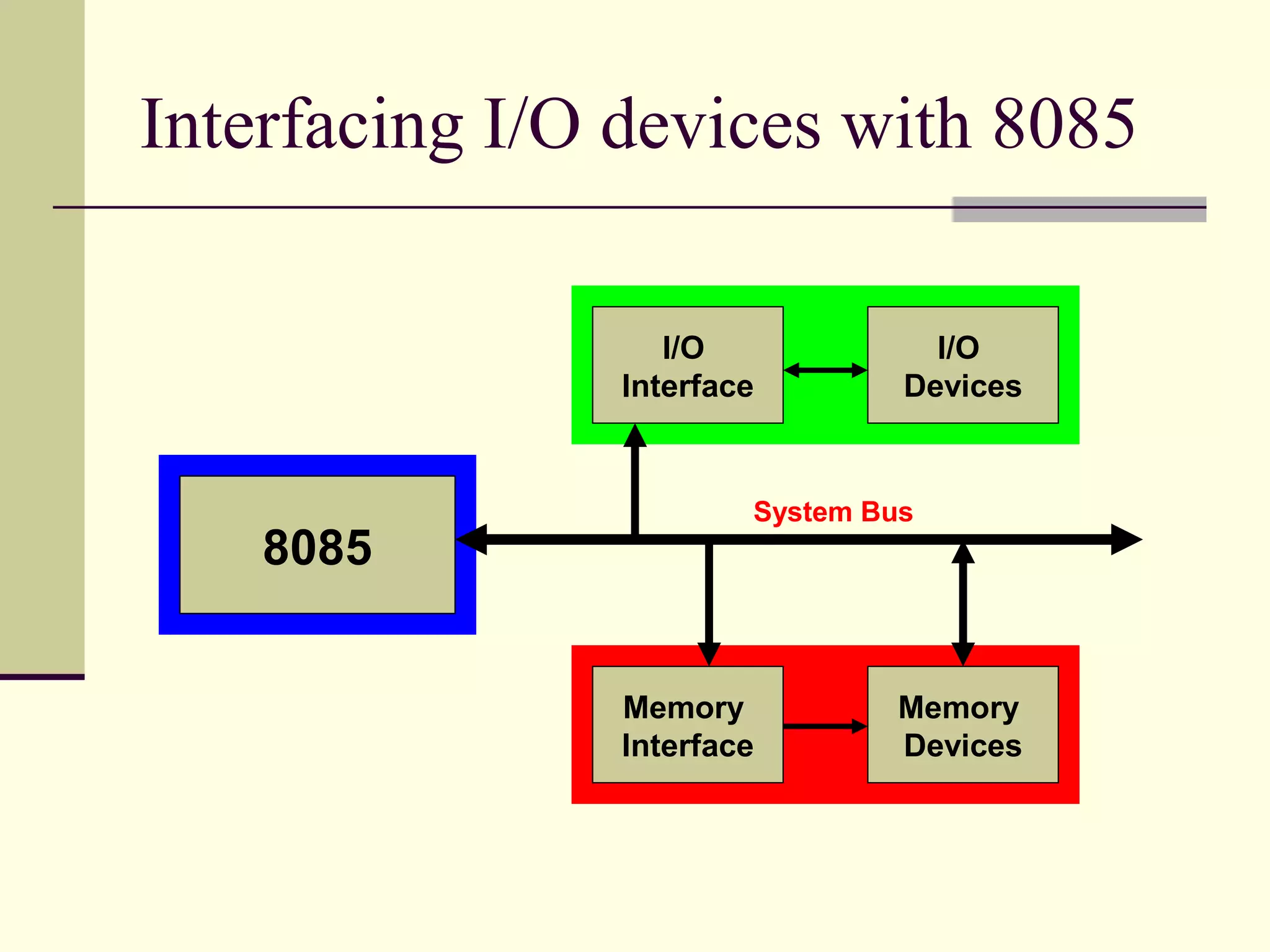

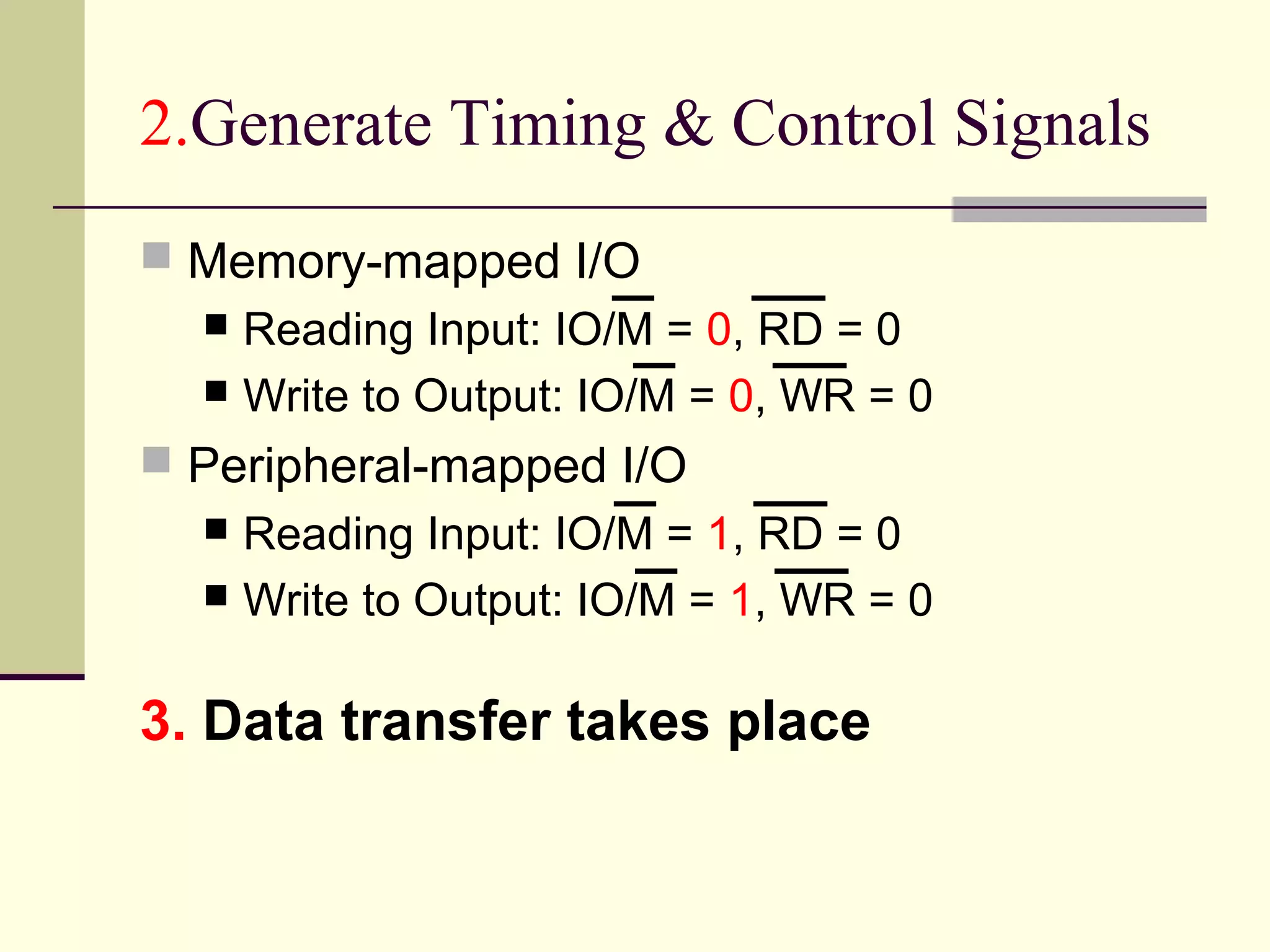

The document provides an overview of the 8085 microprocessor architecture, detailing its components, operation, and interfacing methods. It explains the roles of the address bus, data bus, and control bus, as well as the internal architecture including registers and arithmetic logic unit. Additionally, it discusses memory organization, the concept of memory-mapped versus peripheral-mapped I/O, and outlines the processes for memory and I/O operations.