Field Programmable Gate Array (FPGA) Market Size and Share

Field Programmable Gate Array (FPGA) Market Analysis by Mordor Intelligence

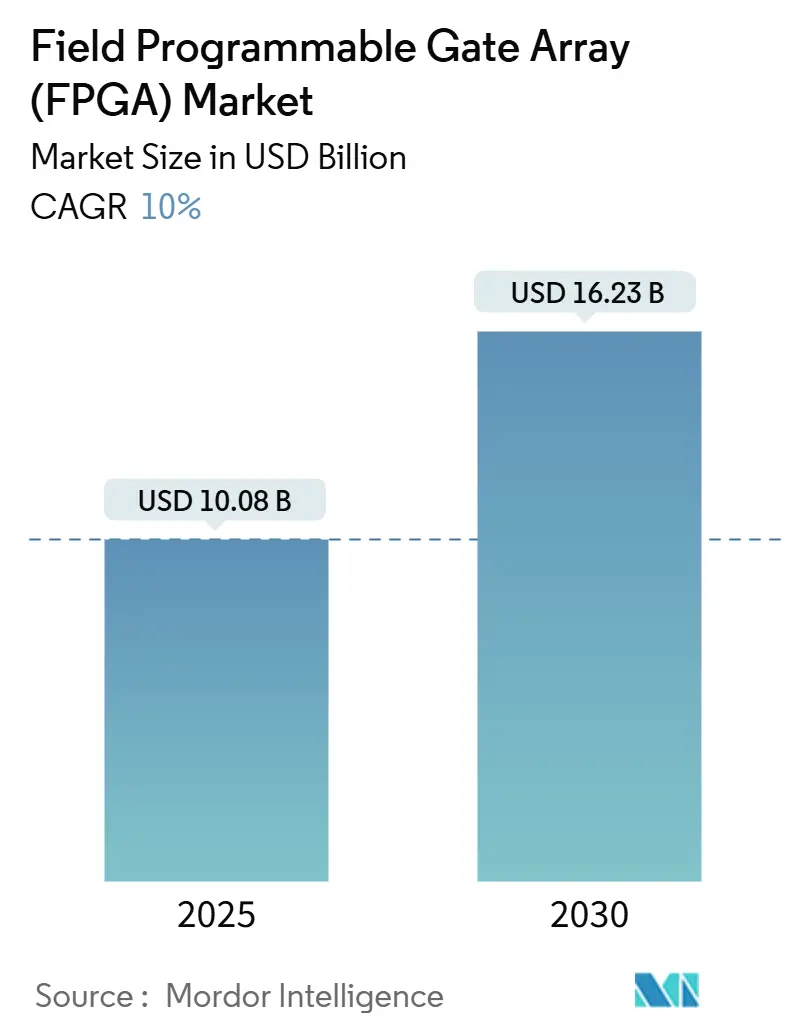

The field programmable gate array market size reached USD 10.08 billion in 2025 and is forecast to expand to USD 16.23 billion by 2030 at a 10.00% CAGR. Rapid adoption of edge-AI inference in hyperscale data centers, the migration to 5G open radio architectures, and the rising need for post-deployment reconfigurability in automotive and aerospace electronics gave the market clear momentum.[1]AMD, “From Invention to AI Acceleration,” amd.com High-end devices continued to anchor revenues, yet mid-range and low-end products climbed quickly as design teams pushed FPGA technology into cost-sensitive industrial, IoT, and consumer systems. Asia-Pacific emerged as both the largest manufacturing base and the fastest-growing demand center, benefiting from electric-vehicle powertrains and new-space constellations. Competitive intensity increased after Intel agreed to carve out Altera, reshaping supplier dynamics while export controls spurred parallel domestic development in China. Tighter 300 mm foundry capacity and the costly transition to ≤16 nm nodes also forced vendors to prioritize high-margin applications and long-term wafer reservations with TSMC and Samsung.

Key Report Takeaways

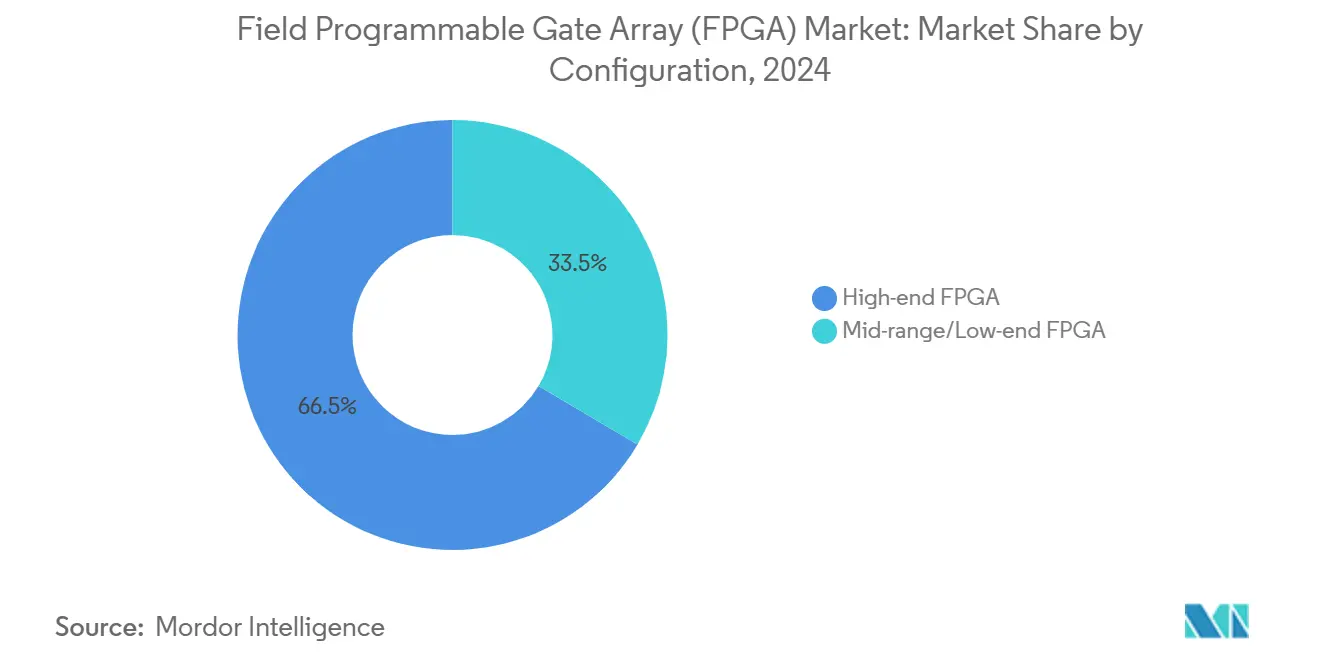

- By configuration, high-end devices led with 66.5% of field programmable gate array market share in 2024, while mid-range and low-end devices are projected to grow at 11.2% CAGR through 2030.

- By architecture, SRAM-based devices held 55.4% revenue share in 2024; flash-based offerings are expected to post the fastest growth given lower static power budgets.

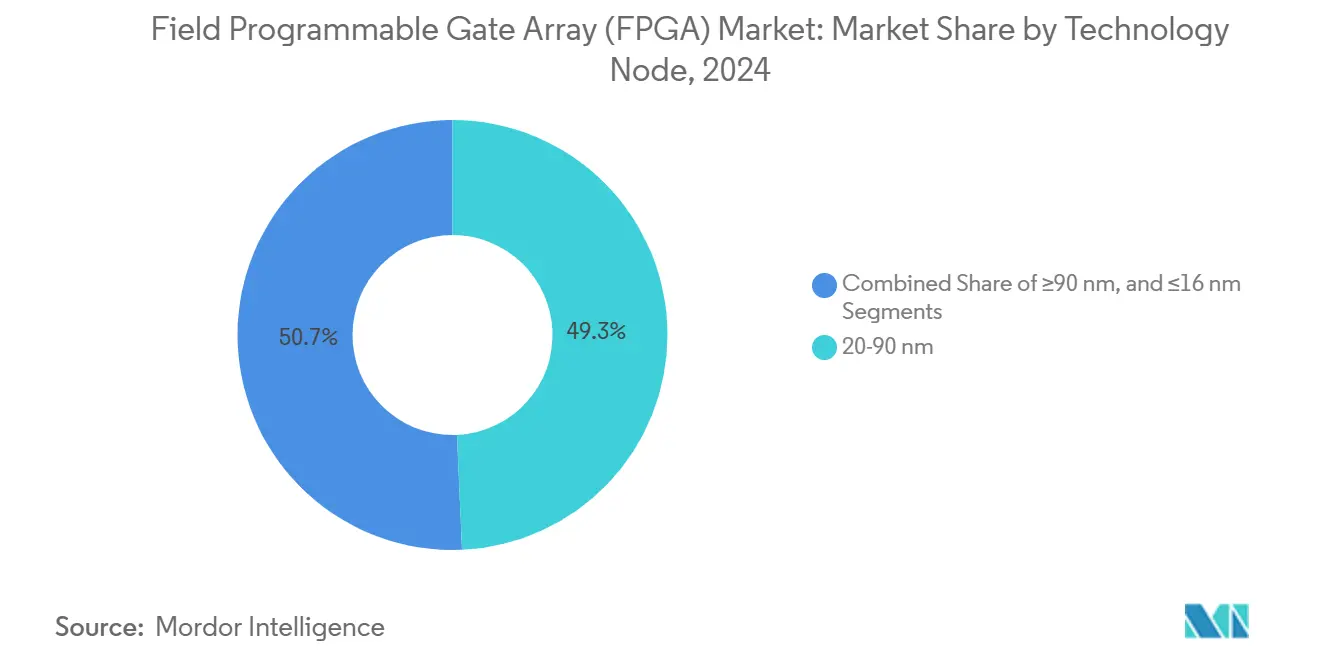

- By technology node, the 20-90 nm segment commanded 49.3% of the field programmable gate array market size in 2024, whereas the ≤16 nm segment is forecast to advance at 15.1% CAGR between 2025-2030.

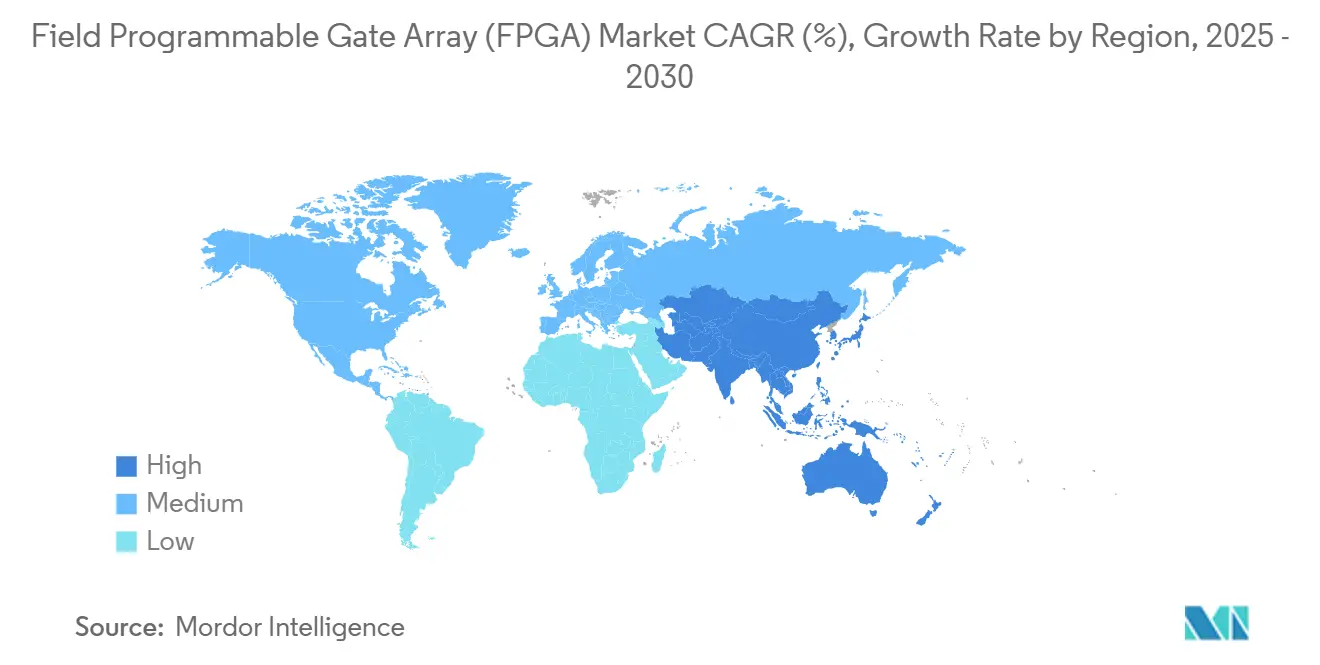

- By geography, Asia-Pacific accounted for 39.3% revenue in 2024 and is set to expand at 17.1% CAGR through 2030.

- By end market, data center and cloud applications captured 29.2% of the field programmable gate array market size in 2024; automotive ADAS and electrification is slated to expand at 13.4% CAGR to 2030.

Global Field Programmable Gate Array (FPGA) Market Trends and Insights

Drivers Impact Analysis

| Driver | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Edge-AI Inference Demand in Hyperscale Data Centres | +2.8% | Global, concentrated in North America and APAC | Medium term (2-4 years) |

| 5G ORAN Shift Requiring Re-programmable Logic in Radios | +2.1% | Global, led by North America, Europe, APAC | Medium term (2-4 years) |

| Rapid Prototyping Needs for ASIC/SoC Shrink Cycles (≤7 nm) | +1.7% | Global, concentrated in North America and APAC | Short term (≤ 2 years) |

| Functional Safety Compliance in Automotive (ISO 26262) | +1.4% | Global, led by Europe, North America, China | Long term (≥ 4 years) |

| Radiation-Tolerant Designs for New-Space Constellations | +0.9% | Global, led by North America, Europe | Long term (≥ 4 years) |

| Chinese EV Power-train OEMs Adopting eFPGAs for Motor Control | +0.6% | APAC, primarily China | Medium term (2-4 years) |

| Source: Mordor Intelligence | |||

Edge-AI inference demand in hyperscale data centers

Hyperscale operators deployed FPGAs to accelerate AI inference once latency and power budgets began outweighing raw throughput requirements. AMD’s Versal AI Edge Gen 2 devices delivered up to 3 × higher TOPS-per-watt than first-generation parts, enabling real-time vision analytics while containing operating expenses. Achronix reported 200 % cost and power advantages versus GPU alternatives when running large language models, underscoring FPGA efficiency in memory-bound workloads. This shift unlocked a distributed compute model where inference processing moved closer to data sources, easing bandwidth constraints and data-sovereignty risks. Integration of on-package HBM and hardened AI engines within leading FPGA families strengthened their position in cloud-edge topologies. Consequently, the field programmable gate array market found a durable growth pillar in hyperscale capital expenditure plans.

5G ORAN shift requiring re-programmable logic in radios

Open radio access network initiatives pushed carriers to adopt vendor-agnostic radio units that could evolve with software upgrades rather than forklift replacements. Intel’s Agilex portfolio used 10 nm SuperFin technology to deliver software-defined radios that adapt to new 5G releases at a lower total cost of ownership. Lattice Semiconductor complemented that hardware with a reference stack providing zero-trust security and real-time encryption for disaggregated networks. AMD’s Zynq RFSoC DFE doubled performance per watt versus prior devices, letting operators support multi-band operation inside compact, power-constrained radio heads. Flexible logic shortened rollout cycles, a critical factor as carriers blended private-5G, fixed-wireless access, and mmWave services. That flexibility secured a new volume opportunity for the field programmable gate array market across telecom infrastructure.

Rapid prototyping needs for ASIC/SoC shrink cycles (≤7 nm)

The time between new process introductions dropped below 24 months, raising the penalty for design missteps. Before ordering masks that cost more than USD 10 million at 3 nm, chip teams used large FPGAs to validate timing, power, and interface behavior. Achronix shipped Speedster7t devices on TSMC 7 nm that provide multi-terabit bandwidth for realistic emulation of next-generation SoCs. TSMC’s forthcoming A16 gate-all-around node promised another 10 % performance uplift and 20 % lower power, yet also increased verification complexity, cementing FPGA platforms as de-risking tools during tape-out. The practice spread beyond server-class accelerators into mixed-signal automotive and industrial ASICs, broadening the field programmable gate array market footprint inside semiconductor design flows.

Functional safety compliance in automotive (ISO 26262)

Advanced driver assistance and electric-vehicle powertrains required real-time, deterministic control that met the ASIL D integrity target. AMD provided TÜV SÜD-certified design flows and IP that reduced development time while meeting ISO 26262 and IEC 61508 mandates. Microchip’s Libero SoC suite carried analogous TÜV Rheinland certificates across PolarFire and SmartFusion 2 families, giving tier-ones a second source for safety-critical logic. Subaru selected Versal AI Edge Gen 2 to power next-generation EyeSight vision, reinforcing OEM confidence in adaptive compute for mission-critical perception. Long product lifecycles in automotive multiply lifetime revenue per design win, supporting the long-run expansion of the field programmable gate array market.

Restraints Impact Analysis

| Restraint | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| US–EU Export Controls on High-performance FPGAs to China | -1.8% | Global, concentrated impact on China-US trade | Short term (≤ 2 years) |

| Volatility in 300 mm Foundry Capacity Allocation | -1.2% | Global, concentrated in APAC foundry hubs | Medium term (2-4 years) |

| Higher Static Power Consumption vs. Dedicated ASIC | -0.7% | Global, across all end markets | Long term (≥ 4 years) |

| Source: Mordor Intelligence | |||

US–EU export controls on high-performance FPGAs to China

New Bureau of Industry and Security rules removed civilian exemptions for advanced FPGA shipments to China in late 2023, restricting devices suited for AI or military use.[2]Federal Register, “Additional Export Controls,” federalregister.gov The shift forced AMD-Xilinx and Intel-Altera to halt or license-screen many orders, reducing near-term unit volumes. Chinese suppliers such as GOWIN and Pango sought to close the gap, yet hurdles in design tools, IP, and advanced process access limited immediate substitution. Multinational customers moved sensitive production away from China or redesigned systems to qualify non-US devices, fracturing previously global supply chains. The resulting uncertainty weighed on the field programmable gate array market until new trade norms stabilized.

Volatility in 300 mm foundry capacity allocation

Advanced FPGA fabrication is clustered at TSMC and Samsung, whose capacity decisions often favored high-volume smartphone APs or GPU accelerators. When AI chip demand surged, wafer slots for mid-volume FPGA products tightened, and lead times lengthened. Vendors placed multi-year deposits or sought secondary sources, raising working capital needs. Schedule risks complicated product-launch roadmaps for automotive and industrial customers that require long-term availability. Although both foundries announced aggressive expansion, yield learning at new nodes and geopolitical site selection kept the supply fragile, creating a persistent constraint on the field programmable gate array market.

Segment Analysis

By Configuration: high-end dominance faces cost pressures

High-end devices held 66.5% of the field programmable gate array market share in 2024, reflecting their central role in data-center acceleration and 5G infrastructure. These platforms, often exceeding 1 million logic cells, carried premium ASPs yet delivered deterministic latency unavailable in GPUs, preserving their appeal for safety-critical aerospace and fintech workloads. Mid-range and low-end devices exhibited an 11.2% CAGR to 2030 as manufacturers like Lattice shipped cost-optimized parts with hardened AI engines that met edge-compute budgets. Design tools have grown more intuitive, letting embedded engineers adopt configurable logic without hardware backgrounds.

The value proposition evolved as AMD introduced Spartan UltraScale+ with 30% lower power and unrivaled I/O count, attacking the mid-range from above. Simultaneously, module vendors supplied pre-validated boards that abstracted pin-planning and PCB layout, trimming design cycles. These shifts are expected to compress the pricing gap between tiers, although high-end devices still command a majority of the field programmable gate array market size when new AI or networking standards emerge that only top-node silicon can satisfy.

By Architecture: SRAM supremacy challenged by power efficiency

SRAM-based solutions owned 55.4% revenue in 2024 and posted an 11.8% CAGR outlook thanks to unlimited reprogram cycles and a deep software ecosystem. Yet flash-based variants gained mindshare in wearables and automotive telematics, where instant-on behavior is vital. Microchip’s RT PolarFire achieved MIL-STD-883 Class B, offering 50% lower power than equivalent SRAM parts while tolerating 100 krad radiation. Anti-fuse platforms sustained a niche in defense avionics where one-time programmability eliminates tampering risk.

Software portability is shrinking historical barriers, so designers can now choose based on power and security rather than tool familiarity. Emerging heterogeneous architectures integrate SRAM fabric with on-die non-volatile domains, providing the best-of-both options. While SRAM devices will continue leading the field programmable gate array market revenue, flash and anti-fuse offerings should carve larger shares in low-power and harsh-environment deployments.

By Technology Node: Advanced nodes drive innovation

The 20-90 nm class held 49.3% field programmable gate array market share in 2024, balancing yield maturity and cost. However, the ≤16 nm category is on track for a 15.1% CAGR as AI inference, coherent interconnects, and 112 G SerDes demand logic density only advanced nodes can offer. AMD migrated select Spartan and Versal lines to 16 nm to blend cost efficiency with modern transceivers. TSMC’s A16 gate-all-around roadmap promises another notch in performance per watt that vendors plan to exploit for PCIe 6.0 and CXL 3.1-enabled products.

At ≥90 nm, legacy industrial controls and military retrofits favor stable supply chains over raw speed, keeping this node alive though shrinking. Moving below 10 nm adds mask and EDA cost burdens that only the largest suppliers can shoulder, raising competitive thresholds. That dynamic could consolidate the field programmable gate array market around players with scale to secure expensive wafers and develop re-targetable software stacks.

By End Market: Automotive electrification accelerates adoption

Data-center and cloud operators captured 29.2% of the field programmable gate array market size in 2024 by exploiting reconfigurable accelerators for AI inference and network virtualization. Automotive applications, including ADAS vision and inverter control, are projected to climb 13.4% CAGR through 2030 as OEMs embed configurable logic to satisfy fast-evolving safety and motor-control algorithms. Achronix’s embedded FPGA IP lets carmakers add late-stage features to custom SoCs, a flexibility highly valued within long vehicle platforms.

Telecommunications remained vibrant because of Open RAN radios seeking multi-band agility. Industrial automation and robotics relied on deterministic motor-control loops where FPGAs replaced legacy DSPs. Aerospace and defense growth centered on radiation-tolerant logic for low-earth orbit satellites. Wearables, test instrumentation, and medical imaging represented younger verticals that benefit from low-power personalized compute. The breadth of uses underscores that the field programmable gate array market continues to expand across cyclical macro environments.

Geography Analysis

Asia-Pacific dominated the field programmable gate array market with 39.3% revenue in 2024 and showed a 17.1% CAGR outlook to 2030. China’s push for semiconductor self-reliance, highlighted by domestic innovators in electric vehicle drives and satellite payloads, pulled in significant FPGA volumes. Taiwan and South Korea supplied advanced fabrication, while Japan specialized in automotive modules and factory automation subsystems. India’s design-service sector advanced after Lattice opened an R&D center in Pune, broadening engineering talent pools.[3]Lattice Semiconductor, “Full Year 2024 Results,” latticesemi.com

North America maintained leadership in data-center infrastructure, high-reliability aerospace, and EDA software. Hyperscalers directed large capital budgets toward adaptive accelerators to manage AI service costs, ensuring the region’s strong purchase share. Export-license reviews shaped shipment patterns but also prompted domestic investment in advanced packaging and OSAT capacity that supports the field programmable gate array market.

Europe leaned on Germany’s automotive supply chain and Nordic telecom equipment providers. ISO 26262 compliance spurred in-vehicle usage, while energy-transition projects created demand for low-loss power converters. EU Digital Decade policies encouraged sovereign edge computing platforms that favor reconfigurability. Although South America and the Middle East, and Africa hold smaller slices today, growth potential in 5G infrastructure and industrial modernization should boost their contribution over the forecast period.

Competitive Landscape

The field programmable gate array market remained concentrated, with AMD-Xilinx and Intel-Altera still generating the majority of revenue in 2024. Intel’s decision in April 2025 to sell 51% of Altera to Silver Lake for USD 8.75 billion aimed to accelerate standalone investments and sharpen focus on high-end acceleration segments. AMD celebrated 40 years of FPGA shipments and highlighted more than 3 billion cumulative units, leveraging its Versal and Spartan families to meet both edge-AI and safety-critical needs.

Lattice Semiconductor gained traction with low-power Nexus and Avant platforms, securing record design wins in generative AI and robotics. Achronix captured share in embedded FPGA IP and multi-terabit networking, while Microchip strengthened its presence by acquiring Neuronix AI Labs to optimize sparsity-aware neural networks on PolarFire devices.[4]Microchip Technology, “Acquires Neuronix AI Labs,” microchip.com Rapid Silicon and other start-ups introduced open-source toolchains, putting price pressure on legacy design suites.

Strategic alliances grew more important than transistor counts alone. Lattice collaborated with NVIDIA on reference stacks for AI inference at the edge, and AMD kept pace through Vitis unified programming flows. Vendors also invested in chiplet-ready packaging and UCIe interconnect standards to let customers assemble heterogeneous systems on common substrates. Such ecosystem moves are expected to define future success in the field programmable gate array market as much as raw logic density.

Field Programmable Gate Array (FPGA) Industry Leaders

-

Advanced Micro Devices, Inc.

-

Lattice Semiconductor Corporation

-

QuickLogic Corporation

-

Intel Corporation

-

Achronix Semiconductor Corporation

- *Disclaimer: Major Players sorted in no particular order

Recent Industry Developments

- June 2025: AMD celebrated 40 years of FPGA innovation, citing more than 3 billion cumulative shipments across automotive and aerospace edge AI platforms AMD.

- May 2025: Lattice Semiconductor reported Q1 2025 revenue of USD 120.1 million with record design wins in generative AI, robotics, automotive ADAS, and edge AI.

- April 2025: Intel agreed to sell 51% of Altera to Silver Lake for USD 8.75 billion, creating the largest standalone FPGA provider.

- March 2025: AMD introduced the Spartan UltraScale+ family for cost-sensitive edge use, citing 30% lower power and class-leading I/O.

Global Field Programmable Gate Array (FPGA) Market Report Scope

FPGAs are prefabricated silicon instruments that can be electrically programmed in the field to become almost any type of digital circuit or system. They are an array of configurable logic blocks (CLBs) linked together by programmable interconnects. After manufacturing, they can be reprogrammed to meet the needs of the desired application or functionality.

The field programmable gate array (FPGA) market is segmented by configuration (high-end FPGA, mid-range FPGA/low-end FPGA), by architecture (SRAM-based FPGA, anti-fuse based FPGA, flash-based FPGA), by end-user industry (IT and telecommunication, consumer electronics, automotive, industrial, military and aerospace, other end-user industries), by geography (North America [United States, Canada], Europe [Germany, United Kingdom, France, rest of Europe], Asia Pacific [China, Japan, India, South Korea, rest of the Asia Pacific], Latin America [Brazil, Argentina, Mexico, rest of Latin America], Middle East and Africa [United Arab Emirates, Saudi Arabia, South Africa, rest of Middle East and Africa]). The market sizes and forecasts are provided in terms of value in USD for all the above segments.

| High-end FPGA |

| Mid-range/Low-end FPGA |

| SRAM-based FPGA |

| Flash-based FPGA |

| Anti-fuse FPGA |

| ≥90 nm |

| 20-90 nm |

| ≤16 nm |

| Data Centre and Cloud Computing |

| Telecommunications and 5G Infrastructure |

| Automotive (ADAS, Electrification) |

| Industrial Automation and Robotics |

| Aerospace and Defense (Avionics, SATCOM) |

| Consumer Electronics and Wearables |

| Test, Measurement and Medical Devices |

| North America | United States | |

| Canada | ||

| Europe | Germany | |

| United Kingdom | ||

| France | ||

| Italy | ||

| Nordics (Sweden, Norway, Finland, Denmark) | ||

| Rest of Europe | ||

| Asia-Pacific | China | |

| Taiwan | ||

| Japan | ||

| South Korea | ||

| India | ||

| ASEAN | ||

| Rest of Asia-Pacific | ||

| South America | Mexico | |

| Brazil | ||

| Argentina | ||

| Rest of South America | ||

| Middle East and Africa | Middle East | Saudi Arabia |

| United Arab Emirates | ||

| Turkey | ||

| Rest of Middle East | ||

| Africa | South Africa | |

| Rest of Africa | ||

| By Configuration | High-end FPGA | ||

| Mid-range/Low-end FPGA | |||

| By Architecture | SRAM-based FPGA | ||

| Flash-based FPGA | |||

| Anti-fuse FPGA | |||

| By Technology Node | ≥90 nm | ||

| 20-90 nm | |||

| ≤16 nm | |||

| By End Market | Data Centre and Cloud Computing | ||

| Telecommunications and 5G Infrastructure | |||

| Automotive (ADAS, Electrification) | |||

| Industrial Automation and Robotics | |||

| Aerospace and Defense (Avionics, SATCOM) | |||

| Consumer Electronics and Wearables | |||

| Test, Measurement and Medical Devices | |||

| By Geography | North America | United States | |

| Canada | |||

| Europe | Germany | ||

| United Kingdom | |||

| France | |||

| Italy | |||

| Nordics (Sweden, Norway, Finland, Denmark) | |||

| Rest of Europe | |||

| Asia-Pacific | China | ||

| Taiwan | |||

| Japan | |||

| South Korea | |||

| India | |||

| ASEAN | |||

| Rest of Asia-Pacific | |||

| South America | Mexico | ||

| Brazil | |||

| Argentina | |||

| Rest of South America | |||

| Middle East and Africa | Middle East | Saudi Arabia | |

| United Arab Emirates | |||

| Turkey | |||

| Rest of Middle East | |||

| Africa | South Africa | ||

| Rest of Africa | |||

Key Questions Answered in the Report

What is the current value of the field programmable gate array market?

The market was valued at USD 10.08 billion in 2025 and is projected to reach USD 16.23 billion by 2030.

Which region is growing the fastest?

Asia-Pacific is forecast to expand at 17.1% CAGR through 2030 due to electric-vehicle powertrain and new-space satellite demand.

Why are FPGAs preferred for edge-AI inference?

They deliver higher performance per watt and deterministic latency versus GPUs, which improves total cost of ownership for hyperscale operators.

How will export controls affect the market?

US–EU restrictions on high-performance devices to China may cut near-term shipments, prompting Chinese firms to accelerate domestic alternatives.

Which configuration segment is advancing the fastest?

Mid-range and low-end devices are set to grow at 11.2% CAGR as cost-optimized platforms reach industrial and IoT applications.

What is the significance of ≤16 nm process nodes for FPGAs?

They enable higher logic density and advanced interfaces like PCIe 6.0, which are critical for AI inference and 5G baseband processing.

Page last updated on:

-Market-logo.webp)