-

Notifications

You must be signed in to change notification settings - Fork 349

Heap refinement Part2 -- Dw dma fixes #4664

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Conversation

lgirdwood

left a comment

lgirdwood

left a comment

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

@kv2019i can you check this with Zephyr. Thanks !

|

@aiChaoSONG are you able to update cmake to 3.20 for Zephyr build CI ? |

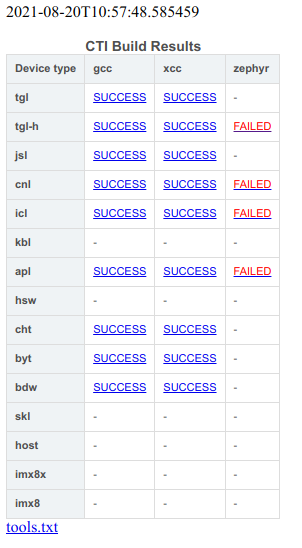

@lgirdwood For internal CI, CMake is updated 3.21.1, we are good to build and test now. For github actions, as no Ubuntu is shipped with a higher version CMake, you will see zephyr build failure in github actions before we can fix it, I will talk with Marc on this. Before we can fix the github action, you can check sof-ci/jenkins/pr-fw-build as an alternative. You can check all firmware build log in the Details. |

|

SOFCI TEST |

|

Looks this introduces regression on APL, let me take a look to it. |

@aiChaoSONG ubuntu CI can be forced to use a newer version of cmake by adding a private ppa for cmake. @marc-hb may have other or better ways to achieve this. |

|

@lgirdwood Test running with Zephyr, will report results today. UPDATE: tests pass cleanly on Zephyr (TGL). |

|

Zephyr Github Actions fixed by @aiChaoSONG in #4668 |

|

well, there is a point that even though for APL single core, it is preferred to use uncached lli address, this requires change for our cAVS heap definition @lgirdwood |

|

@lgirdwood let me fix this with the heap refinement together, so let's pick it in this order:

|

lyakh

left a comment

lyakh

left a comment

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Does this PR actually fix #4568? If yes - it should mention it, perhaps. Also, when fixing such hard to debug bugs it would be best to indicate which specific change fixes the problem. Also, to re-iterate, it would really be much better if we could figure out what exactly was broken...

src/platform/intel/cavs/lib/memory.c

Outdated

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

why do shared heaps have the CACHE capability set? Both .runtime_shared and .system_shared heaps return uncached aliases, don't they?

src/include/sof/drivers/dw-dma.h

Outdated

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Was aeda015 a guess or a documented feature? How did we come up with 128 bytes on TGL?

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Was aeda015 a guess or a documented feature? How did we come up with 128 bytes on TGL?

Unfortunately, It was a guess only.

src/drivers/dw/dma.c

Outdated

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

why does it have to be zeroed? It wasn't zeroed before. If that was causing problems because we expect zeroes somewhere, then that should be fixed explicitly! Otherwise rmalloc() should do just fine.

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

So you don't need alignment any longer? That seems very odd for hardware descriptors?

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

So you don't need alignment any longer? That seems very odd for hardware descriptors?

@plbossart the rmalloc() internal guarantees the return pointer is PLATFORM_DCACHE_ALIGN aligned, please see the source here:

Line 718 in 8fc5247

| return get_ptr_from_heap(heap, flags, caps, bytes, PLATFORM_DCACHE_ALIGN); |

|

@keyonjie looks like we need this to be well commented in the code due to the complexity of the problem along side the 1,2 and 3 fixes. Ok do do this a single PR that way we will keep your 1,22 3 ordering ? |

This reverts commit aeda015. Signed-off-by: Keyon Jie <yang.jie@linux.intel.com>

The lli structs are used by both DSP and DMAC, allocate them from the runtime_shared heap to avoid being corrupted by cache writing back. This helps to fix a lot of DMA xrun issue according to the validation. Signed-off-by: Keyon Jie <yang.jie@linux.intel.com>

src/drivers/dw/dma.c

Outdated

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

So you don't need alignment any longer? That seems very odd for hardware descriptors?

|

Let me close this, will submit others first. |

after this fix, the previous merged commit that enlarging the lli struct size is not needed any more. @lgirdwood FYI.