-

Notifications

You must be signed in to change notification settings - Fork 349

dw-dma: align ILL allocations #3645

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Conversation

src/drivers/dw/dma.c

Outdated

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Since you claim the problem is about alignment, why not rballoc_align with a specific alignment value that ought to solve it? Even if you pass it PLATFORM_DCACHE_ALIGN which thus makes it equivalent, I think it's better to be explicit in this particular case.

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

@paulstelian97 It depends on how rballoc() is defined. If it is a part of its definition, that returned memory is always cache-line size aligned, then I think the code is fine as is. If however it's just a kind of a hidden side-effect, that might change in the future, then yes, it would be better to change this. I'm fine either way. Let's wait for a couple of hours, if there are no opinions one way or another, if the CI "failure" doesn't mean this is breaking functionality, I can change it, sure.

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Oh it's completely equivalent, rballoc(...) is precisely rballoc_aligned(..., PLATFORM_DCACHE_ALIGN). However I wanted to see the alignment being explicitly specified for coding style points.

|

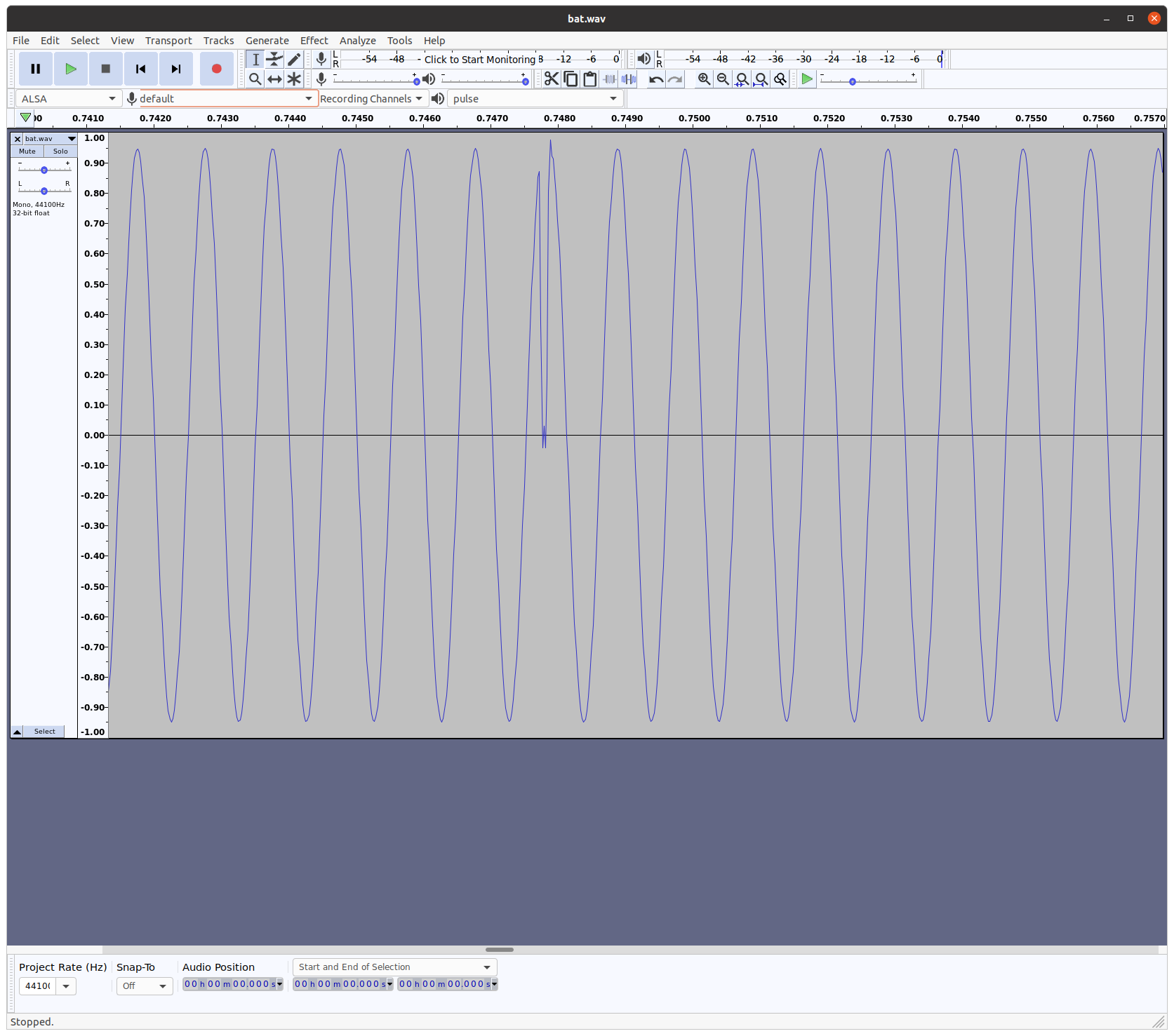

Do I understand it correctly, that the failure on BYT_MB_NOCODEC is because of the signal frequency being up to 10% off? Can it really be related to this PR? |

|

SOFCI TEST |

lgirdwood

left a comment

lgirdwood

left a comment

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Can we make the alignment obvious in the code.

@lgirdwood sure, let's wait for test completion first? |

ok, one unrelated failure, will have to file a bug... Pushing update |

|

Wondering if this could help with #3492. we could never figure out what causes the DMA to repeat samples. |

|

@lgirdwood yes, it looks like platform failure. Running rebuild right away. |

|

@zrombel Thanks for re-running. @lgirdwood The latest failure is unrelated: "[drm] ERROR CPU pipe A FIFO underrun" and a fix has been merged 2 days ago thesofproject/sof-test#535 so, actually, this shouldn't appear any more if the current sof-test is used |

ILL entries in the DW DMA driver are accessed both by the controller, using DMA and by the DSP. For this to work the DSP has to force cache synchronisation appropriately. Therefore the ILL area has to be allocated with cache-line size alignment. This isn't the case with the Zephyr allocator. This patch switches allocation from rmalloc() to rballoc() to force such alignment. Eventually a generic fix will be implemented in an SOF wrapper fpr the Zephyr allocator. Signed-off-by: Guennadi Liakhovetski <guennadi.liakhovetski@linux.intel.com>

|

SOFCI TEST |

|

Rerun CI, seems jenkins stalled. |

|

Jenkins known issue. |

ILL entries in the DW DMA driver are accessed both by the controller, using DMA and by the DSP. For this to work the DSP has to force cache synchronisation appropriately. Therefore the ILL area has to be allocated with cache-line size alignment. This patch switches allocation from rmalloc() to rballoc() to force such alignment.