-

获得4,693次点赞

-

内容获得56次评论

-

获得12,803次收藏

-

代码片获得14,434次分享

-

-

各类FPGA通信算法的学习与分析 付费1篇

各类FPGA通信算法的学习与分析 付费1篇 -

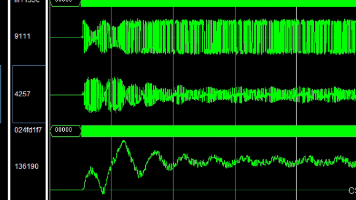

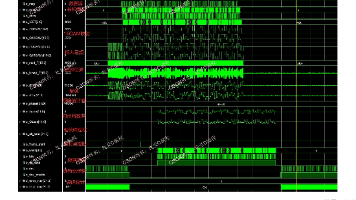

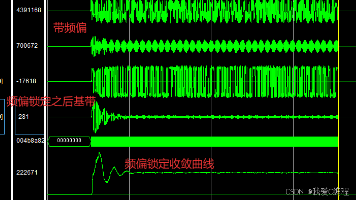

01.基于FPGA的Costas环开发案例 付费20篇

01.基于FPGA的Costas环开发案例 付费20篇 -

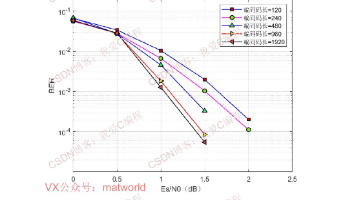

Matlab通信和信号 311篇

Matlab通信和信号 311篇 -

Matlab优化算法 120篇

Matlab优化算法 120篇 -

MATLAB图像处理 87篇

MATLAB图像处理 87篇 -

Matlab深度学习 168篇

Matlab深度学习 168篇 -

MATLAB加解密算法 5篇

MATLAB加解密算法 5篇 -

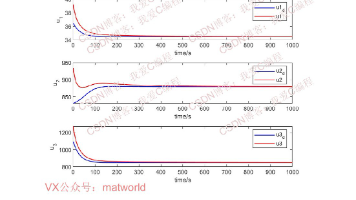

Matlab控制器 29篇

Matlab控制器 29篇 -

MATLAB激光雷达

MATLAB激光雷达 -

Matlab数值仿真 8篇

Matlab数值仿真 8篇 -

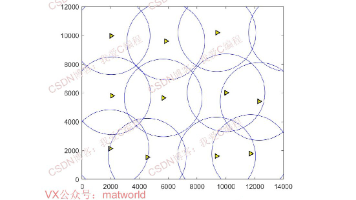

Matlab网络算法 35篇

Matlab网络算法 35篇 -

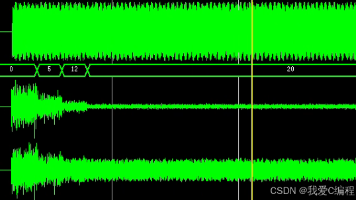

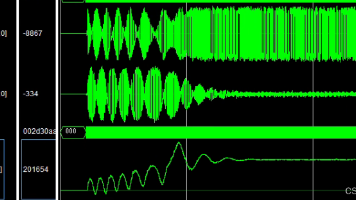

Matlab语音信号处理 7篇

Matlab语音信号处理 7篇 -

Matlab编译码 58篇

Matlab编译码 58篇 -

Matlab最优路径规划 16篇

Matlab最优路径规划 16篇 -

Matlab三维重建 20篇

Matlab三维重建 20篇 -

Matlab小波变换 4篇

Matlab小波变换 4篇 -

Matlab光学仿真 2篇

Matlab光学仿真 2篇 -

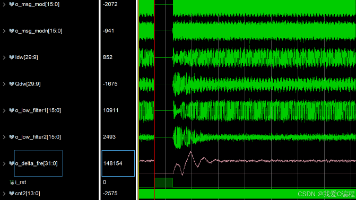

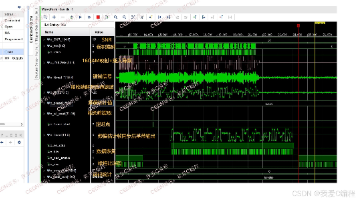

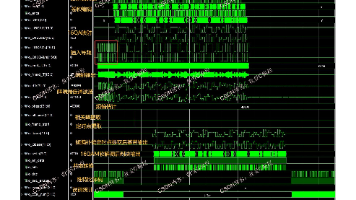

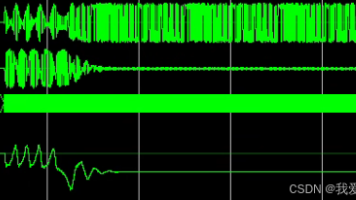

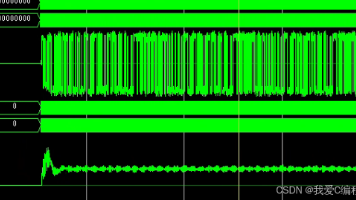

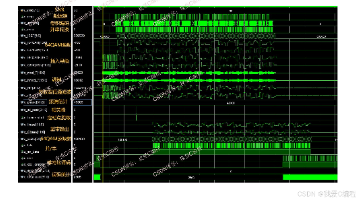

FPGA通信和信号处理【硬件测试】 41篇

FPGA通信和信号处理【硬件测试】 41篇 -

FPGA通信和信号处理 152篇

FPGA通信和信号处理 152篇 -

FPGA图像处理 4篇

FPGA图像处理 4篇 -

FPGA机器学习 1篇

FPGA机器学习 1篇 -

Simulink控制器 55篇

Simulink控制器 55篇

TA关注的专栏 7

TA关注的收藏夹 0

TA关注的社区 2

TA参与的活动 0

____我是"我爱C编程",专注通信信号,人工智能,控制以及图像处理,擅长FPGA、MATLAB等技术。项目合作/下载程序如报错可联系我邮箱: 1480526168@qq.com

博客文章源码获取方式:

————————————————————

方式1.直接打开面包多 :

————————————————————

方式2.扫一扫公众号二维码 :

AI 镜像开发实战征文活动

随着人工智能技术的飞速发展,AI 镜像开发逐渐成为技术领域的热点之一。Stable Diffusion 3.5 FP8 作为强大的文生图模型,为开发者提供了更高效的图像生成解决方案。为了推动 AI 镜像开发技术的交流与创新,我们特此发起本次征文活动,诚邀广大开发者分享在 Stable Diffusion 3.5 FP8 文生图方向的实战经验和创新应用 本次征文活动鼓励开发者围绕 Stable Diffusion 3.5 FP8 文生图方向,分享以下方面的内容: 1. 技术实践与优化 - Stable Diffusion 3.5 FP8 模型架构解析与优化技巧 - 文生图生成效果的提升方法与技巧 - 模型部署与加速策略,例如使用 Hugging Face、Diffusers 等工具 - 针对特定场景(例如二次元、写实风)的模型微调与定制化开发 2. 应用场景探索 - Stable Diffusion 3.5 FP8 在不同领域的应用案例分享,例如游戏设计、广告创意、艺术创作等 - 利用 Stable Diffusion 3.5 FP8 实现图像编辑、图像修复、图像增强等功能的探索 - 结合其他 AI 技术(例如 NLP、语音识别)构建更强大的应用 3. 创新应用与思考 - 基于 Stable Diffusion 3.5 FP8 的创新应用场景设计 - AI 镜像开发的未来发展方向的思考与展望 - 对 AI 镜像开发伦理、安全等问题的探讨

- 最近

- 文章

- 专栏

- 代码仓

- 资源

- 收藏

- 关注/订阅/互动

最近

文章

专栏

代码仓

资源

收藏

关注/订阅/互动

社区

帖子

问答

课程

视频